0% encontró este documento útil (0 votos)

100 vistas16 páginasFuncionamiento de Transistores FET y MOSFET

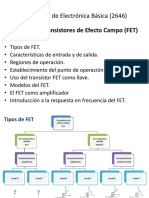

Los transistores de efecto de campo (FET) controlan el flujo de corriente a través de un canal semiconductor mediante la aplicación de un campo eléctrico. El FET más común es el MOSFET de óxido metálico semiconductor, el cual puede fabricarse como de tipo mejora o agotamiento. Los FET también pueden ser de canal n o p. El documento describe la estructura y funcionamiento del MOSFET de tipo mejora de canal n, explicando cómo la aplicación de voltajes de puerta, drenaje y fuente crea o elimina un canal que permite el

Cargado por

gonzaloDerechos de autor

© © All Rights Reserved

Nos tomamos en serio los derechos de los contenidos. Si sospechas que se trata de tu contenido, reclámalo aquí.

Formatos disponibles

Descarga como DOCX, PDF, TXT o lee en línea desde Scribd

0% encontró este documento útil (0 votos)

100 vistas16 páginasFuncionamiento de Transistores FET y MOSFET

Los transistores de efecto de campo (FET) controlan el flujo de corriente a través de un canal semiconductor mediante la aplicación de un campo eléctrico. El FET más común es el MOSFET de óxido metálico semiconductor, el cual puede fabricarse como de tipo mejora o agotamiento. Los FET también pueden ser de canal n o p. El documento describe la estructura y funcionamiento del MOSFET de tipo mejora de canal n, explicando cómo la aplicación de voltajes de puerta, drenaje y fuente crea o elimina un canal que permite el

Cargado por

gonzaloDerechos de autor

© © All Rights Reserved

Nos tomamos en serio los derechos de los contenidos. Si sospechas que se trata de tu contenido, reclámalo aquí.

Formatos disponibles

Descarga como DOCX, PDF, TXT o lee en línea desde Scribd