Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Fase 3 - Electronica Digital

Cargado por

Leidysita Ramirez0 calificaciones0% encontró este documento útil (0 votos)

26 vistas16 páginasDar solución al problema teniendo lo planteado

Derechos de autor

© © All Rights Reserved

Formatos disponibles

DOCX, PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoDar solución al problema teniendo lo planteado

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOCX, PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

26 vistas16 páginasFase 3 - Electronica Digital

Cargado por

Leidysita RamirezDar solución al problema teniendo lo planteado

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOCX, PDF, TXT o lea en línea desde Scribd

Está en la página 1de 16

FASE 3 - ANÁLISIS DE CIRCUITOS SECUENCIALES

Nombre: Álvaro Pérez

Código: 91421091

Tutor: Sandra Milena Garcia

Universidad Nacional Abierta y a Distancia UNAD

Escuela de Ciencias Básicas, tecnología e ingeniería ECBTI

Ingeniería electrónica

Electrónica digital

Barrancabermeja

2023

INTRODUCCIÓN

En el presente trabajo, desarrollaremos la tarea 3- Circuitos Secuenciales. Se realizaron

investigaciones de conceptos teóricos apoyándonos en la unidad 3 y diseñamos circuitos

secuenciales a nivel de diagrama de bloques, describiéndolos en VHDL utilizando el

software online EdaPlayGround. Con la realización de este informe fortalecemos

nuestros conocimientos en circuitos secuenciales Para la resolución del presente

informe, nos apoyamos en el libro de Muñoz y en la explicación que se encuentran en el

entorno de conocimiento unidad 2. Los circuitos lógicos que se han considerado han

sido combinatorios. En estos las salidas en cualquier punto del tiempo dependen

completamente de las entradas que se presenten en ese momento. flip-flop y latch, es un

circuito multivibrador, que tiene dos estados estables y puede almacenar información.

Se puede hacer que cambie de estado mediante señales aplicadas a una o más entradas

de control y tiene una o dos salidas. Es el elemento de almacenamiento básico en lógica

secuencial.

OBJETIVOS

Estudiar y comprender los circuitos digitales Secuenciales

Diseñar e implementar circuitos secuenciales a nivel de diagramas de bloques y

en lenguaje de programación basado en VHDL

Apropiar conceptos como memoria, registros, contadores, módulos entre otros,

en la aplicación de soluciones prácticas.

DESARROLLO DE LA ACTIVIDAD

1. Preguntas orientadoras:

Defina con sus propias palabras los siguientes conceptos luego de hacer la búsqueda en

los textos guías.

a. Circuitos asíncronos y síncronos.

Cuando un circuito secuencial cambia de estado, cuando se realiza el cambio en la

entrada se le denomina asíncrono y cuando existen varios elementos memoria, se

precisa que cambien todos a la vez, es entonces que el circuito se le denomina síncrono.

b. Latch

Son circuitos secuenciales biestables síncronos por nivel, estos deben tener una señal de

reloj que controla cuando el biestable actualiza sus salidas en función de las entradas. Es

decir, las salidas solo pueden cambiar cuando el reloj esta activo y permanece inmóviles

si el reloj se encuentra inactivo.

c. Flip-Flop

Son dispositivos biestables que funcionan como una memoria básica para operaciones

en lógica secuencial, son usadas normalmente en unidades llamadas registro para el

almacenamiento. Los flip-flop tipo D toman lo que está en la entrada de datos y lo copia

a la salida Q, cada que hay una transición de reloj.

d. Registro

Es el nombre que se le da a un conjunto de 8 o más flip-flops tipo D y tipo T. los más

populares son los de 8 bits Los tipos de registros son:

Entrada en paralelo - salida a paralelo

Entrada serial - salida serial

Entrada en paralelo - salida serial

Entrada serial - salida en paralelo

Corrimiento bidireccional

e. Contador

Es un circuito secuencial que puede ser sincrónico o asincrónico, tiene una entrada de

tipo reloj que activa una serie de circuitos lógicos para establecer como salida un

numero en formato de tipo binario, hexadecimal.

2. Descripción de hardware en VHDL

En el siguiente enlace encontrará las plantillas en VHDL requeridas para las diferentes

descripciones de hardware, se utilizará los archivos:

1. 0 Estructura_General

2. 1 archivo Simulación

3. 2 Reloj para simulación

4. Flip-Flop Reset y Enable

5. Flip-Flop Reset

Enlace: https://drive.google.com/open?id=1JjCgZSw1KY5fq99l8rOe9oNw4uPe83Ii

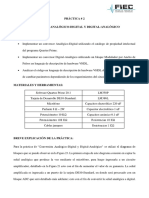

2.1. Diseño de Flip-Flop:

Hacer la descripción en VHDL de un Flip-Flop tipo D, con reset activo en alto y enable

activo en alto. Debe incluir en el informe:

Un diagrama de bloques y colocar la tabla de verdad.

Imagen 1. Diagrama de bloques y tabla de verdad

Impresión de Pantalla de la descripción en VHDL (Ver la advertencia al final

de la guía, con respecto a las impresiones de pantallas válidos).

Imagen 2. Script EDA playground, Flip- Flop

Imagen 3. Script EDA playground, Flip- Flop

Impresión de Pantalla del resultado (diagrama de tiempo) de la simulación,

en el cual se debe evidenciar el correcto funcionamiento del diseño. NO se

debe incluir el código VHDL de la simulación. Use la descripción en VHDL

de la figura 1 como orientación y complete el archivo de simulación.

Imagen 4. Diagrama de tiempo EDA playground, Flip- Flop

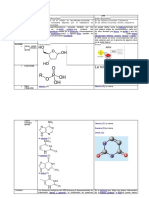

2.2. Diseño de un registro. Hacer la descripción en VHDL de un registro.

Debe incluir en el informe:

Número de bits del registro

Estudiante 1 4 bits

Un diagrama de bloques y colocar la tabla de verdad.

Imagen 5. Diagrama de bloques y tabla de verdad

Reset Entrada Clk Salida

1 0 1 1

0 0 1 0

1 1 0 0

0 1 0 1

Impresión de Pantalla de la descripción en VHDL (Ver la advertencia al final

de la guía, con respecto a las impresiones de pantallas válidos).

Imagen 6. Descripción EDA playground, Registro 4 bits

Imagen 7. Descripción EDA playground, Registro 4 bits

Impresión de Pantalla del resultado (diagrama de tiempo) de la simulación,

en el cual se debe evidenciar el correcto funcionamiento del diseño. NO se

debe incluir el código VHDL de la simulación.

Imagen 8. Diagrama de tiempo EDA playground, Registro

2.3. Contador ascendente.

Hacer la descripción en VHDL de un contador ascendente módulo N.

Modulo N

Estudiante 1 5

Debe incluir en el informe:

Un diagrama de bloques diseñado por el estudiante.

Imagen 8. Diagrama de bloques

Impresión de Pantalla de la descripción en VHDL (Ver la advertencia al final

de la guía, con respecto a las impresiones de pantallas válidos).

Imagen 9. Descripción EDA playground, Contador Ascendente

Imagen 10. Descripción EDA playground, Contador Ascendente

Impresión de Pantalla del resultado (diagrama de tiempo) de la simulación,

en el cual se debe evidenciar el correcto funcionamiento del diseño. NO se

debe incluir el código VHDL de la simulación.

Imagen 11. Diagrama de tiempo EDA playground, Contador Ascendente

2.4. Contador descendente

Hacer la descripción en VHDL de un contador descendente módulo N. Debe incluir en

el informe:

Modulo N

Estudiante 1 5

Un diagrama de bloques diseñado por el estudiante.

Imagen 12. Diagrama de bloque Contador descendente

Impresión de Pantalla de la descripción en VHDL (Ver la advertencia al final de

la guía, con respecto a las impresiones de pantallas válidos).

Imagen 13. Descripción EDA playground, Contador Descendente

Imagen 14. Descripción EDA playground, Contador Descendente

Impresión de Pantalla del resultado (diagrama de tiempo) de la simulación, en el

cual se debe evidenciar el correcto funcionamiento del diseño. NO se debe

incluir el código VHDL de la simulación.

Imagen 15. Diagrama de tiempo EDA playground, Contador Descendente

2.5. Contador ascendente y descendente

Hacer la descripción en VHDL de un contador ascendente/descendente módulo N. Debe

incluir en el informe:

Modulo M

Estudiante 1 10

Un diagrama de bloques diseñado por el estudiante.

10

10

Imagen 16. Diagrama de bloque Contador ascendente-descendente

Impresión de Pantalla de la descripción en VHDL (Ver la advertencia al final de

la guía, con respecto a las impresiones de pantallas válidos).

Imagen 17. Descripción EDA playground, Contador Ascendente-Descendente

Imagen 18. Descripción EDA playground, Contador Ascendente-Descendente

Impresión de Pantalla del resultado (diagrama de tiempo) de la simulación, en el

cual se debe evidenciar el correcto funcionamiento del diseño. NO se debe

incluir el código VHDL de la simulación.

Imagen 19. Diagrama de tiempo EDA playground, Contador Ascendente-Descendente

CONCLUSIONES

De acuerdo con los resultados obtenidos se concluye que se obtuvieron los

resultados esperados en la actividad, gracias a él buen manejo de los conceptos y

conocimientos aprendidos, Se dio el debido desarrollo a la guía aplicando los

conceptos y procedimientos otorgados en la unidad 3 circuitos digitales

secuenciales en VHDL.

Utilizar el conocimiento conceptual dado en clase para programar VHDL los

tipos de flip-flop y las aplicaciones de los mismos.

Garantizar el óptimo funcionamiento de cada flip-flop

Gracias al anterior trabajo se logró el entendimiento y funcionamiento de los

circuitos digitales secuenciales, cuáles pueden ser sus aplicaciones y como a

través del lenguaje de descripción de hardware podemos diseñar y realizar las

simulaciones de los circuitos para ver su comportamiento según el diseño

realizado

REFERENCIAS BIBLIOGRÁFICAS

Muñoz, J. (2012). Introducción a los Sistemas Digitales: Un enfoque usando Lenguajes

de Descripción de Hardware. (Capítulos 7, 9 y 10, pp. 135-149,177-208). Madrid.

Recuperado de: https://openlibra.com/es/book/introduccion-a-los-sistemas-digitales

Flórez, F. H. A. (2010). Diseño lógico: fundamentos de electrónica digital. (Capítulos

5,6 pp. 109-145). Recuperado de:

https://ebookcentralproquestcom.bibliotecavirtual.unad.edu.co/lib/unadsp/

reader.actiondocID=3 199073&ppg=1

Fajardo, C. (2019, abril 15), Contador con Modulo en EdaPlayGround [Archivo de

video], Recuperado de: https://youtu.be/S_nmINYWOOQ

También podría gustarte

- Fase 3 - Estudiante1 Neiker MuñozDocumento17 páginasFase 3 - Estudiante1 Neiker MuñozJavier Andres Arevalo GarayAún no hay calificaciones

- Tarea 4-Ever MartinezDocumento18 páginasTarea 4-Ever Martinezandres martinezAún no hay calificaciones

- Tarea 3Documento21 páginasTarea 3Naimer Urango BanquethAún no hay calificaciones

- Guía de Actividades y Rúbrica de Evaluación - Unidad 2 - Fase 2 - Análisis de Circuitos CombinacionalesDocumento14 páginasGuía de Actividades y Rúbrica de Evaluación - Unidad 2 - Fase 2 - Análisis de Circuitos CombinacionalesNilson Pajaro CastroAún no hay calificaciones

- Tarea 2 Circuitos CombinacionalesDocumento18 páginasTarea 2 Circuitos CombinacionalesEdgar PerezAún no hay calificaciones

- Multiplexor 8 A 2Documento12 páginasMultiplexor 8 A 2Nath GonzalezAún no hay calificaciones

- Tarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.Documento22 páginasTarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.MiGue DAzaAún no hay calificaciones

- Tarea 4 - Cristian Cortinez - 243004 - 11Documento14 páginasTarea 4 - Cristian Cortinez - 243004 - 11Angélica AyalaAún no hay calificaciones

- Laboratorio Calificado 2 - 2023 - 1 UTPDocumento5 páginasLaboratorio Calificado 2 - 2023 - 1 UTPCarlos Jesus Koo LabrinAún no hay calificaciones

- Laboratorio Logica Secuencial (Virtual)Documento4 páginasLaboratorio Logica Secuencial (Virtual)Juan Camilo Betancur RicoAún no hay calificaciones

- Unidad3 Tarea4 Johan PerezDocumento9 páginasUnidad3 Tarea4 Johan Perezsalvadore perezAún no hay calificaciones

- Tarea3 243004 45Documento13 páginasTarea3 243004 45Andres ManosalvaAún no hay calificaciones

- Unidad 2 James Bend Reinoso Diaz Grupo 243004 72Documento18 páginasUnidad 2 James Bend Reinoso Diaz Grupo 243004 72james reinosoAún no hay calificaciones

- Digital 1Documento17 páginasDigital 1Cristian RicauteAún no hay calificaciones

- Unidad3 - Tarea 4 Electronica DigitalDocumento12 páginasUnidad3 - Tarea 4 Electronica Digitalluz marina villarragaAún no hay calificaciones

- Laboratorio Calificado 2 - PresencialDocumento5 páginasLaboratorio Calificado 2 - PresencialEdgarciito Bryan Nino CcosccoAún no hay calificaciones

- Reductor de Frecuencia PDFDocumento8 páginasReductor de Frecuencia PDFAlejandro AlvarezAún no hay calificaciones

- Tarea3 Grupo32.Documento14 páginasTarea3 Grupo32.marcos andres nieves gullo50% (2)

- Trabajo Final de Electronica DigitalDocumento18 páginasTrabajo Final de Electronica DigitalkarenAún no hay calificaciones

- Tarea3 Grupo243004 49Documento34 páginasTarea3 Grupo243004 49Andres PerezAún no hay calificaciones

- Prepa 8Documento9 páginasPrepa 8Carlos SuarezAún no hay calificaciones

- Guia 4 SDI115Documento6 páginasGuia 4 SDI115Carlos_29Aún no hay calificaciones

- Guía4 SDI-1 2018Documento6 páginasGuía4 SDI-1 2018Jesus SJAún no hay calificaciones

- Tarea 3 Circuitos CombinacionalesDocumento9 páginasTarea 3 Circuitos CombinacionalesAndres PerezAún no hay calificaciones

- Lab14 AdcDocumento5 páginasLab14 AdcEdison RodriguezAún no hay calificaciones

- Portada Sistemas EmbebidosDocumento14 páginasPortada Sistemas EmbebidosALAN ULISES BANUELOS RUVALCABAAún no hay calificaciones

- Tarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.Documento22 páginasTarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.MiGue DAza100% (1)

- Contador 2Documento4 páginasContador 2cristobal hernandezAún no hay calificaciones

- Grupo45 Fase 3Documento22 páginasGrupo45 Fase 3Altahir Gamer (Altahir.3D)Aún no hay calificaciones

- Tarea 3Documento13 páginasTarea 3daniela cordobaAún no hay calificaciones

- Tarea2 - Jose Bernal - 243004A - 761Documento17 páginasTarea2 - Jose Bernal - 243004A - 761Jackson Giraldo100% (1)

- Ejercicio 5Documento2 páginasEjercicio 5GeovannyAún no hay calificaciones

- Tarea3 JacksonApraezDocumento12 páginasTarea3 JacksonApraezJairo HurtatisAún no hay calificaciones

- Laboratorio Calificado 2 PDFDocumento4 páginasLaboratorio Calificado 2 PDFSebastian Avila TelloAún no hay calificaciones

- Circuitos CombinacionalesDocumento13 páginasCircuitos CombinacionalesJairo Velasquez BustosAún no hay calificaciones

- Proyecto FinalDocumento5 páginasProyecto Finalemilio roaAún no hay calificaciones

- Ttarea3 Grupo24Documento19 páginasTtarea3 Grupo24Carlos Eduardo Rengifo AvilaAún no hay calificaciones

- Laboratorio de Diseño Digital Practica #3: Circuitos Aritméticos y DecodificadoresDocumento3 páginasLaboratorio de Diseño Digital Practica #3: Circuitos Aritméticos y DecodificadoresPaulina Bastida GarciaAún no hay calificaciones

- Tarea 2 Karen VillamilDocumento18 páginasTarea 2 Karen VillamilKaren VillamilAún no hay calificaciones

- 49 - Tarea - 3 - Circuitos - SecuencialesDocumento33 páginas49 - Tarea - 3 - Circuitos - SecuencialesKaren VillamilAún no hay calificaciones

- Práctica # 2 Conversión Analógico-Digital y Digital-AnalógicoDocumento18 páginasPráctica # 2 Conversión Analógico-Digital y Digital-AnalógicoMichelle martinez rAún no hay calificaciones

- Actividades A DesarrollarDocumento15 páginasActividades A DesarrollarJose M CaballeroAún no hay calificaciones

- Tarea 4 - Gelberth Baez - 243004 - 10Documento12 páginasTarea 4 - Gelberth Baez - 243004 - 10david cano moraAún no hay calificaciones

- Electronica DigitalDocumento19 páginasElectronica DigitalComark Ponguta100% (1)

- Tarea - 4 - Secuenciales3Documento7 páginasTarea - 4 - Secuenciales3UTUMAOAún no hay calificaciones

- Julian Ramiro Lopez - Fase 3 - Análisis de Circuitos SecuencialesDocumento6 páginasJulian Ramiro Lopez - Fase 3 - Análisis de Circuitos SecuencialesJulian LopezAún no hay calificaciones

- German-Tarea3 AportesDocumento14 páginasGerman-Tarea3 Aportesgerman.toro3885Aún no hay calificaciones

- Laboratorio Circuitos DigitalesDocumento10 páginasLaboratorio Circuitos DigitalesLuis BaldassariAún no hay calificaciones

- Tutorial Simulador AllegroDocumento44 páginasTutorial Simulador Allegroynot666Aún no hay calificaciones

- Lab13 Elementos Memoria VHDL 2022Documento12 páginasLab13 Elementos Memoria VHDL 2022Nocturnal BvAún no hay calificaciones

- ComponentesnennProgramacinnnnACTn2nnnEVn2 5162157aa03d062Documento8 páginasComponentesnennProgramacinnnnACTn2nnnEVn2 5162157aa03d062Santiago Caro UmbaribaAún no hay calificaciones

- Decodificador de 7 SegmentosDocumento12 páginasDecodificador de 7 SegmentosOliver Argote BritoAún no hay calificaciones

- Practica Con VHDLDocumento9 páginasPractica Con VHDLAle KeyAún no hay calificaciones

- Laboratorio de Electrónica IiDocumento15 páginasLaboratorio de Electrónica IiLeonardoAún no hay calificaciones

- Circuitos Secuenciales. Unidad 3 Tarea 3Documento15 páginasCircuitos Secuenciales. Unidad 3 Tarea 3EsnerAún no hay calificaciones

- Tarea 3 Grupo 3Documento24 páginasTarea 3 Grupo 3Cam Mcm PvcAún no hay calificaciones

- Practica #2 Control de Un Display de 7 SegmentosDocumento9 páginasPractica #2 Control de Un Display de 7 SegmentosJuan Pablo Garcia LanderoAún no hay calificaciones

- Tarea 2 - ELECTRONICA DIGITAL - Juan Felipe Perdomo NaverosDocumento12 páginasTarea 2 - ELECTRONICA DIGITAL - Juan Felipe Perdomo NaverosJuan Felipe PerdomoAún no hay calificaciones

- Tarea 3Documento18 páginasTarea 3Jose M CaballeroAún no hay calificaciones

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- ElectronicaDocumento8 páginasElectronicaLeidysita RamirezAún no hay calificaciones

- Laboratorio I6Documento8 páginasLaboratorio I6Leidysita RamirezAún no hay calificaciones

- Informe LaboratorioDocumento6 páginasInforme LaboratorioLeidysita RamirezAún no hay calificaciones

- EnsayoDocumento3 páginasEnsayoLeidysita RamirezAún no hay calificaciones

- Ejercicios Tarea 3Documento10 páginasEjercicios Tarea 3Leidysita RamirezAún no hay calificaciones

- Fase 2 - Control AnalogicoDocumento19 páginasFase 2 - Control AnalogicoLeidysita RamirezAún no hay calificaciones

- Cchacon - Sobre ElectrostáticaDocumento23 páginasCchacon - Sobre ElectrostáticaLeidysita RamirezAún no hay calificaciones

- 16 - BásicosDocumento3 páginas16 - BásicosLeidysita RamirezAún no hay calificaciones

- Infantería MarinaDocumento4 páginasInfantería MarinaLeidysita RamirezAún no hay calificaciones

- Átomos, Moléculas y IonesDocumento3 páginasÁtomos, Moléculas y IonesLeidysita RamirezAún no hay calificaciones

- 18 - AvanzadosDocumento4 páginas18 - AvanzadosLeidysita RamirezAún no hay calificaciones

- DISPOSITIVOS DE DIFRACCIÓN - 3er TrabajoDocumento7 páginasDISPOSITIVOS DE DIFRACCIÓN - 3er TrabajoLeidysita RamirezAún no hay calificaciones

- Cuadro de Cargas FinalDocumento3 páginasCuadro de Cargas FinalLeidysita RamirezAún no hay calificaciones

- I5. Estudio de Las Energías Cinética y Potencial en Sistemas Conservativos y No ConservativosDocumento1 páginaI5. Estudio de Las Energías Cinética y Potencial en Sistemas Conservativos y No ConservativosLeidysita RamirezAún no hay calificaciones

- Introducción MatlabDocumento3 páginasIntroducción MatlabLeidysita RamirezAún no hay calificaciones

- I4. Estudio Del Movimiento de Un Cuerpo Sobre Un Plano Inclinado Con RozamientoDocumento1 páginaI4. Estudio Del Movimiento de Un Cuerpo Sobre Un Plano Inclinado Con RozamientoLeidysita RamirezAún no hay calificaciones

- Materia y Propiedades de La MateriaDocumento2 páginasMateria y Propiedades de La MateriaLeidysita RamirezAún no hay calificaciones

- Cifras Significativas y Análisis DimensionalDocumento2 páginasCifras Significativas y Análisis DimensionalLeidysita RamirezAún no hay calificaciones

- C2 Asignacion 2Documento3 páginasC2 Asignacion 2Leidysita RamirezAún no hay calificaciones

- Química y Unidades de MedidaDocumento3 páginasQuímica y Unidades de MedidaLeidysita RamirezAún no hay calificaciones

- Asignacion 3Documento6 páginasAsignacion 3Leidysita RamirezAún no hay calificaciones

- Materia y Propiedades de La MateriaDocumento2 páginasMateria y Propiedades de La MateriaLeidysita RamirezAún no hay calificaciones

- Mide Lo Que Es Medible, y Haz Medible Lo Que No Lo Es" Galileo GalileiDocumento1 páginaMide Lo Que Es Medible, y Haz Medible Lo Que No Lo Es" Galileo GalileiLeidysita RamirezAún no hay calificaciones

- Asignacion 3Documento6 páginasAsignacion 3Leidysita RamirezAún no hay calificaciones

- Cuadro ComparativoDocumento6 páginasCuadro ComparativoLeidysita RamirezAún no hay calificaciones

- AGROTURISMODocumento20 páginasAGROTURISMOLeidysita RamirezAún no hay calificaciones

- Historia Del ComputadorDocumento3 páginasHistoria Del ComputadorLeidysita RamirezAún no hay calificaciones

- Receta de Salsa HolandesaDocumento6 páginasReceta de Salsa HolandesaLeidysita RamirezAún no hay calificaciones

- Adn y ArnDocumento3 páginasAdn y ArnLeidysita RamirezAún no hay calificaciones

- T Lab #03. Laboratorio Diseño Digital - 030218Documento34 páginasT Lab #03. Laboratorio Diseño Digital - 030218luis carrasquelAún no hay calificaciones

- T82 PDFDocumento221 páginasT82 PDFGamma RamAún no hay calificaciones

- Sistema Secuencial y CombinacionalDocumento4 páginasSistema Secuencial y CombinacionalDaniel Andres SanchezAún no hay calificaciones

- Fundamentos de Sistemas DigitalesDocumento21 páginasFundamentos de Sistemas DigitalessinnueAún no hay calificaciones

- Circuito SecuencialDocumento3 páginasCircuito SecuencialIsrael SánchezAún no hay calificaciones

- Controladores SecuencialesDocumento4 páginasControladores SecuencialesEmilio AlejandroAún no hay calificaciones

- Circuitos Secuenciales SincronosDocumento15 páginasCircuitos Secuenciales Sincronoswilber arenasAún no hay calificaciones

- Informe de Practicas de Circuitos Digitales Practica #5Documento8 páginasInforme de Practicas de Circuitos Digitales Practica #5carlos sanchezAún no hay calificaciones

- 07 electronicaII ContenidosDocumento21 páginas07 electronicaII ContenidosJavi Pinto0% (3)

- Proyecto FinalDocumento21 páginasProyecto FinalFerAún no hay calificaciones

- 1 - UNIDAD 1 DigitalDocumento79 páginas1 - UNIDAD 1 DigitalCesarAún no hay calificaciones

- 555 Temporizador 2023FDocumento22 páginas555 Temporizador 2023FEDITH LOPEZ RAMONAún no hay calificaciones

- 05 Formato Sistemas de Examen Final Forma 2 202150-Signed-SignedDocumento6 páginas05 Formato Sistemas de Examen Final Forma 2 202150-Signed-SignedCARLOS SANTIAGO CADENA VILCAHUANOAún no hay calificaciones

- Sistemas Secuenciales SincronosDocumento59 páginasSistemas Secuenciales SincronosCamilo RoncancioAún no hay calificaciones

- Examen de C Electronicos II 2016Documento28 páginasExamen de C Electronicos II 2016Jano EstradaAún no hay calificaciones

- Sistemas Secuenciales Con Boole-DeustoDocumento9 páginasSistemas Secuenciales Con Boole-DeustoTomas Sanchez TronoAún no hay calificaciones

- Manejo 555 e Introducción A Flip FlopsDocumento22 páginasManejo 555 e Introducción A Flip FlopsNicoll GonzalezAún no hay calificaciones

- Maquinas Finitas ExpoDocumento19 páginasMaquinas Finitas ExpoNatalia G LazcanoAún no hay calificaciones

- El Control Industrial. Clasificación y EtapasDocumento39 páginasEl Control Industrial. Clasificación y EtapasANDERSON ADONIS SOSA LOPEZAún no hay calificaciones

- Maquina Expendedora Asm PDFDocumento52 páginasMaquina Expendedora Asm PDFJhozy CuevaAún no hay calificaciones

- Tarea S1 Electronicadigital JeDocumento9 páginasTarea S1 Electronicadigital JeJOFFRE ESTRADAAún no hay calificaciones

- Maquina Moore y MealyDocumento24 páginasMaquina Moore y MealyKiara Salcedo Mamani100% (1)

- Guia 1 Circuitos SecuencialesDocumento13 páginasGuia 1 Circuitos SecuencialesIVAN GALINDO VILLARRAGAAún no hay calificaciones

- Sistemas Digitales 3Documento26 páginasSistemas Digitales 3Adrian Calva SuarezAún no hay calificaciones

- Introducción A Los Circuitos SecuencialesDocumento26 páginasIntroducción A Los Circuitos SecuencialesArturo72Aún no hay calificaciones

- Practica 8Documento22 páginasPractica 8irvin_aguilar_17Aún no hay calificaciones

- Automatización 1Documento24 páginasAutomatización 1Kyoki DriftersAún no hay calificaciones

- Informe Practica de Circuitos DigitalesDocumento9 páginasInforme Practica de Circuitos DigitalescamiloAún no hay calificaciones

- Clasificacion de Los Sistemas DigitalesDocumento14 páginasClasificacion de Los Sistemas DigitalesChristian MoralesAún no hay calificaciones

- Practica Semaforo AutomaDocumento5 páginasPractica Semaforo AutomaCarlos RamosAún no hay calificaciones