Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Diseño de circuitos aritméticos binarios y BCD usando sumadores y ALU de 4 bits

Cargado por

Dario Nina SantosTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Diseño de circuitos aritméticos binarios y BCD usando sumadores y ALU de 4 bits

Cargado por

Dario Nina SantosCopyright:

Formatos disponibles

4

Practica #

CIRCUITOS ARITMÉTICOS.

1. OBJETIVOS DE LA PRÁCTICA A REALIZAR

• Sintetizar funciones lógicas utilizando sumadores.

• Realizar operaciones aritméticas de números binarios con signo.

• Poder comprender las operaciones aritméticas que se pueden realizan con los

sumadores.

• Diseñar sumadores que realicen la operación de suma y resta con un código BCD ya

definido.

• Diseñar un pequeño ALU con funciones ya definidas y conocer a la unidad aritmética

lógica de 4 bits de selección 74LS181

• Escribir los programas para los circuitos aritméticos en un lenguaje de descripción de

Hardware.

2. EJERCICIOS DE LA PRÁCTICA

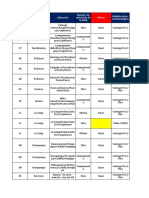

1. Sintetizar sólo con sumadores las siguientes funciones:

a) 𝐹𝐴𝐵𝐶𝐷 = ∑4(1,2,4,5,6,7,9,10)

b) 𝐺𝑊𝑋𝑌𝑍 = ∏4(4̅, 5̅, 6̅, 9̅, 10

̅̅̅̅, 11

̅̅̅̅, 14

̅̅̅̅)

c) 𝐻𝐴𝐵𝐶𝐷 = ∑4(0,3,5,9,12,15)

2. Realizar las siguientes operaciones, A+B, A-B, -A+B, -A-B, para los números

codificados en binario natural, mediante el complemento a 1 y el complemento

a 2:

a) A=33 B=42

b) A=-20 B=-88

3. Realizar las siguientes operaciones, A+B, A-B, -A+B, -A-B, para los números

codificados en BCD 8421, mediante el complemento a 9 y el complemento a

10:

a) A=29 B=67

b) A=-123 B=50

4. Diseñar un circuito que realice la suma del número A de cuatro bits con el

mayor de los dos números B y C de 4 bits. Los tres números están codificados

en el sistema binario natural. Utilizar sumadores binarios y comparadores y las

puertas lógicas que se consideren necesarias. En base al código VHDL realice

el código de la operación y el vector de pruebas en ISE.

5. Realice un análisis completo (teórico y práctico) de la generación anticipada

del acarreo para un sumador de 4 bits, dibuje el circuito final del sumador

completo de 4 bits con acarreo anticipado con compuertas lógicas NAND

únicamente y a partir del diseño planteado, escriba el código en Verilog y VHDL.

6. Diseñe un sumador de dos dígitos con signo utilizando complemento a 9 para

números BCD Ex3 sin utilizar transcodificador. Dibuje el circuito resultante y

realice el código en VHDL y en WinCUPL.

7. Se dispone de tres números codificados en Jhonson, diseñar el circuito

combinacional que realice la suma de los dos números mayores. Dibuje el

circuito resultante y explique su funcionamiento. Realice el código en Verilog.

8. Diseñar solamente con sumadores un sistema que permita transcodificar un

digito en código 2 en 5 a código Aiken y viceversa. Dibuje el circuito, realice el

código VHDL y el vector de pruebas para ISE.

9. Diseñar un circuito divisor que realice la división de un número de 4 bits entre

un número de 2 bits. Utilice compuertas lógicas y módulos necesarios. Dibuje

el circuito resultante y realice el mismo diseño utilizando GAL’s.

10. Diseñe una ALU que realice las siguientes funciones:

F1= A+B

F2= Complemento a 10 de B

F3= A+1

F4= A-B

Utilice compuertas lógicas y módulos necesarios. Dibuje el circuito resultante y

realice el programa VHDL correspondiente.

- NOTA .-

Se tomará en cuenta, en la calificación los siguientes puntos:

➢ El procedimiento de los ejercicios.

➢ La puntualidad en la entrega de las prácticas.

➢ La “similitud” entre las prácticas de los estudiantes (si se encontrara

copia, se anulará el ejercicio y/o la práctica en su totalidad).

También podría gustarte

- Simulación de circuitos electrónicos con OrCAD® PSpice®De EverandSimulación de circuitos electrónicos con OrCAD® PSpice®Aún no hay calificaciones

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Circuitos aritméticos sumadores BCD ALU prácticaDocumento3 páginasCircuitos aritméticos sumadores BCD ALU prácticaDaniel AguilarAún no hay calificaciones

- Laboratorio 4 I 2023 601Documento6 páginasLaboratorio 4 I 2023 601JOELAún no hay calificaciones

- Guia 5Documento2 páginasGuia 5Joseph Pérez GuédezAún no hay calificaciones

- Laboratorio 3 Etn 601 I 2016Documento6 páginasLaboratorio 3 Etn 601 I 2016Daniel AguilarAún no hay calificaciones

- Guia de Ejercicios Etn601-Ii - 2022Documento30 páginasGuia de Ejercicios Etn601-Ii - 2022Bleymar Quinteroz LauraAún no hay calificaciones

- Laboratorio N4Documento2 páginasLaboratorio N4Jonathan Chafloque TasaycoAún no hay calificaciones

- Modulos CombinacionalesDocumento6 páginasModulos CombinacionalesRolando Choque CahuanaAún no hay calificaciones

- Guia IseDocumento33 páginasGuia IseMiguel Lara NisttahuzAún no hay calificaciones

- Karnaugh Mapas DigitalesDocumento10 páginasKarnaugh Mapas DigitalesRonald PuchaAún no hay calificaciones

- Trabajo Práctico #1 - ConsignaDocumento2 páginasTrabajo Práctico #1 - Consignakipadaj730Aún no hay calificaciones

- Práctica No.1Documento16 páginasPráctica No.1Andrés CabayAún no hay calificaciones

- TP07 Diseño Con MSI 2019Documento7 páginasTP07 Diseño Con MSI 2019JonatanArtalAún no hay calificaciones

- Práctica 5a Deco7sgmnt (MapaK)Documento2 páginasPráctica 5a Deco7sgmnt (MapaK)Ian CaballeroAún no hay calificaciones

- P3 DDDocumento3 páginasP3 DDPaulina Bastida GarciaAún no hay calificaciones

- Práctica 01 CompuertasDocumento5 páginasPráctica 01 CompuertasOrlando Jose HerediaAún no hay calificaciones

- CTOSCOMBINATORIOSDocumento7 páginasCTOSCOMBINATORIOSIsc Edgar EduardoAún no hay calificaciones

- PRAC3 Comparadores Sumadores RestadoresDocumento6 páginasPRAC3 Comparadores Sumadores RestadoresJose IsaiasAún no hay calificaciones

- Examen Parcial de Circuitos Digitales g3 2022 PreguntasDocumento1 páginaExamen Parcial de Circuitos Digitales g3 2022 Preguntasian carlo espinoza santiagoAún no hay calificaciones

- ETN601LABORATORIO3Documento6 páginasETN601LABORATORIO3Dario Nina SantosAún no hay calificaciones

- ITE-426-Lab-02-Karnaugh & VerilogDocumento4 páginasITE-426-Lab-02-Karnaugh & VerilogDiego Samuel Benitez MarcanoAún no hay calificaciones

- Unm2021-Td1-Tp7 - Msi y MemDocumento6 páginasUnm2021-Td1-Tp7 - Msi y MemAriel Eduardo FariasAún no hay calificaciones

- Laboratorio 5: Codificadores, decodificadores, comparadores y generadores de paridadDocumento3 páginasLaboratorio 5: Codificadores, decodificadores, comparadores y generadores de paridadRaul Depaz NuñezAún no hay calificaciones

- Uni-Fiee Sistemas Digitales I CICLO 2020-1 EE-635 M-N Segundo LaboratorioDocumento3 páginasUni-Fiee Sistemas Digitales I CICLO 2020-1 EE-635 M-N Segundo LaboratorioAlfred PILLACA GOMEZAún no hay calificaciones

- Ej T3FtosDocumento6 páginasEj T3Ftospete sajotAún no hay calificaciones

- AC TP Clase Gua Unificada v1 8Documento23 páginasAC TP Clase Gua Unificada v1 8Aguss BosseroAún no hay calificaciones

- Laboratorio 4 Etn 601 I 2016Documento6 páginasLaboratorio 4 Etn 601 I 2016Daniel AguilarAún no hay calificaciones

- 01 GuiaCombinacionalesDocumento8 páginas01 GuiaCombinacionalesCesar Lautaro AngeloffAún no hay calificaciones

- Decodificador 5 a 32 con módulos 74154Documento23 páginasDecodificador 5 a 32 con módulos 74154Juan CarlosAún no hay calificaciones

- guiaDocumento58 páginasguiaEnzoAún no hay calificaciones

- Uni-Fiee Sistemas Digitales I CICLO 2020-1 EE-635 M-N Tercer LaboratorioDocumento3 páginasUni-Fiee Sistemas Digitales I CICLO 2020-1 EE-635 M-N Tercer LaboratorioEduardo Mendoza CentenoAún no hay calificaciones

- Guia I - 2020Documento33 páginasGuia I - 2020Omar MarcaAún no hay calificaciones

- CircuitoDocumento3 páginasCircuitoJose Jairo VinceAún no hay calificaciones

- FUNDEC-CompComplemento9-MuxFuncionDocumento2 páginasFUNDEC-CompComplemento9-MuxFuncionJorge Santiago MontielAún no hay calificaciones

- Clase Práctica #7Documento7 páginasClase Práctica #7Erick Rafael Ramirez BonacheaAún no hay calificaciones

- Practica 6Documento3 páginasPractica 6Sangu Sumerio Solis CAún no hay calificaciones

- Sumador y restador 4 bits VHDLDocumento2 páginasSumador y restador 4 bits VHDLjhoanAún no hay calificaciones

- Diseña comparadores y convertidores usando CI 74LS85Documento1 páginaDiseña comparadores y convertidores usando CI 74LS85markolzAún no hay calificaciones

- Practica 3 Electronica DigitalDocumento6 páginasPractica 3 Electronica DigitalALVARO RMZ.FLORESAún no hay calificaciones

- 03 Electronica - Trabajo T3Documento2 páginas03 Electronica - Trabajo T3Jorge Imaña valenciaAún no hay calificaciones

- UNLaM2020 IntSistDig TP6 - MSI y MemDocumento6 páginasUNLaM2020 IntSistDig TP6 - MSI y MemGabrielSoteloDuarteAún no hay calificaciones

- Actividades 2 Con MULTISIMDocumento9 páginasActividades 2 Con MULTISIMnewmanchegaAún no hay calificaciones

- Módulos funcionales de lógica combinacionalDocumento3 páginasMódulos funcionales de lógica combinacionalDario Nina SantosAún no hay calificaciones

- 01 Ejercicios Funciones de Lógica Combinacional Resueltos-1Documento10 páginas01 Ejercicios Funciones de Lógica Combinacional Resueltos-1Abyd SantanaAún no hay calificaciones

- Practica 5 - Circuitos CombinacionalesDocumento12 páginasPractica 5 - Circuitos CombinacionalesJuan ValienteAún no hay calificaciones

- ED-GITT Prac02Documento14 páginasED-GITT Prac02Mario MontecatineAún no hay calificaciones

- Sumador 1Documento4 páginasSumador 1ingridAún no hay calificaciones

- Práctica 5Documento2 páginasPráctica 5jorge quintero galindoAún no hay calificaciones

- Ejercicios de electrónica digital - conversiones numéricas, Karnaugh, circuitos lógicosDocumento23 páginasEjercicios de electrónica digital - conversiones numéricas, Karnaugh, circuitos lógicosretrueke1170Aún no hay calificaciones

- Trabajo 6 Diseño de Convertidores de Códigos DigitalesDocumento2 páginasTrabajo 6 Diseño de Convertidores de Códigos DigitalesANTONIO GRATEROLAún no hay calificaciones

- Decodificador de 7 SegmentosDocumento12 páginasDecodificador de 7 SegmentosOliver Argote BritoAún no hay calificaciones

- LAB 8-2023-2-CD-Circuitos - AritmeticosDocumento3 páginasLAB 8-2023-2-CD-Circuitos - AritmeticosjustinguillermolamadridrijalbaAún no hay calificaciones

- P3 CombinacionalesDocumento7 páginasP3 CombinacionalesDrone DevotionAún no hay calificaciones

- Tarea Sistema Digitales PDFDocumento11 páginasTarea Sistema Digitales PDFJorge CruzAún no hay calificaciones

- TP2 - Circuitos CombinatoriosDocumento3 páginasTP2 - Circuitos CombinatoriosSantiago CouraultAún no hay calificaciones

- Digital Practica 4Documento12 páginasDigital Practica 4Jaciel Alexis Meraz TovarAún no hay calificaciones

- 01 Ejercicios Funciones de Lógica CombinacionalDocumento2 páginas01 Ejercicios Funciones de Lógica CombinacionalAbyd SantanaAún no hay calificaciones

- Exámenes resueltos de Estructura y Tecnología de Computadores IDocumento97 páginasExámenes resueltos de Estructura y Tecnología de Computadores IJose RamirezAún no hay calificaciones

- Taller PiuveytkDocumento6 páginasTaller Piuveytkdavid estebanAún no hay calificaciones

- ETN601LABORATORIO1Documento12 páginasETN601LABORATORIO1Dario Nina SantosAún no hay calificaciones

- ETN601LABORATORIO3Documento6 páginasETN601LABORATORIO3Dario Nina SantosAún no hay calificaciones

- ETN601EJERCICIOS5II2021601Documento3 páginasETN601EJERCICIOS5II2021601Dario Nina SantosAún no hay calificaciones

- ETN601LABORATORIO2Documento7 páginasETN601LABORATORIO2Dario Nina SantosAún no hay calificaciones

- ETN601EJERCICIOS6II2021601Documento3 páginasETN601EJERCICIOS6II2021601Dario Nina SantosAún no hay calificaciones

- ETN601EJERCICIOS2II2021601Documento3 páginasETN601EJERCICIOS2II2021601Dario Nina SantosAún no hay calificaciones

- Módulos funcionales de lógica combinacionalDocumento3 páginasMódulos funcionales de lógica combinacionalDario Nina SantosAún no hay calificaciones

- Marco Teorico - Internet de Las CosasDocumento12 páginasMarco Teorico - Internet de Las CosasJoséValdés :3Aún no hay calificaciones

- Presentación Variador PF7000 (O.varas)Documento67 páginasPresentación Variador PF7000 (O.varas)MAITA QUISPE EDY INESAún no hay calificaciones

- FYR2023 Laboratorio Integrador E1Documento7 páginasFYR2023 Laboratorio Integrador E1Jose Rovelo Perez AlvarezAún no hay calificaciones

- SOMATOM Go - Now - Agente FARKIM-1Documento1 páginaSOMATOM Go - Now - Agente FARKIM-1Juan Jose Aucar FarkimAún no hay calificaciones

- Diagnostico Financiero de La Empresa Samsung Electronic S - 1Documento12 páginasDiagnostico Financiero de La Empresa Samsung Electronic S - 1ANGELA VICTORIA GONZALEZ CARRERAAún no hay calificaciones

- Sesión 1. LEGODocumento16 páginasSesión 1. LEGORuben Luque MamaniAún no hay calificaciones

- Ficha Practica 1-22Documento2 páginasFicha Practica 1-22Edwin H QuiñonesAún no hay calificaciones

- ZOOMDocumento8 páginasZOOMFrancisca JavierAún no hay calificaciones

- Conciliacion BancariaDocumento51 páginasConciliacion BancariaOrlando DiazAún no hay calificaciones

- Implementación progresiva de CIM maximiza beneficiosDocumento20 páginasImplementación progresiva de CIM maximiza beneficiosMiguelSchenoneAún no hay calificaciones

- Manual Del Epoch 650Documento400 páginasManual Del Epoch 650ANDRESAún no hay calificaciones

- Examen 1Documento5 páginasExamen 1segundo juan montalvo riosAún no hay calificaciones

- Importancia de la información y fuentes para el comercio exteriorDocumento20 páginasImportancia de la información y fuentes para el comercio exteriorAntonio TichyAún no hay calificaciones

- Guia de Firma EspectralDocumento16 páginasGuia de Firma EspectralSoFi PerezAún no hay calificaciones

- Ruiz CO-SDDocumento89 páginasRuiz CO-SDLuis Gustavo Inga ParionaAún no hay calificaciones

- Math For Machine Learning Book (Spanish Version) (Final) PDFDocumento151 páginasMath For Machine Learning Book (Spanish Version) (Final) PDFFranklin Portillo100% (4)

- Estado de Estaciones Meteorológicas BNVDocumento10 páginasEstado de Estaciones Meteorológicas BNVFIDEL HUMBERTO DE PAZ LUNAAún no hay calificaciones

- Control Semana 7 ABDDocumento12 páginasControl Semana 7 ABDfrancoco420 sierraAún no hay calificaciones

- Ejercicios ResueltosDocumento10 páginasEjercicios ResueltosFrzhAún no hay calificaciones

- Interfaces POODocumento4 páginasInterfaces POOEduardoAún no hay calificaciones

- Actividad A Realizar Actividad 5 La UltimaDocumento3 páginasActividad A Realizar Actividad 5 La UltimaYira MartichAún no hay calificaciones

- Visual Studio 2019 Developer (Online)Documento3 páginasVisual Studio 2019 Developer (Online)Chris PasacheAún no hay calificaciones

- CTS521 Centros de Transformación de Pedestal. Dimensiones Mínimas Del Local Con Equipos Tipo Pedestal PDFDocumento2 páginasCTS521 Centros de Transformación de Pedestal. Dimensiones Mínimas Del Local Con Equipos Tipo Pedestal PDFPaola Correa MoncadaAún no hay calificaciones

- 2 Estructura de DatosDocumento20 páginas2 Estructura de DatosManuel PerezAún no hay calificaciones

- Definición de Soporte Técnico y Características PrincipalesDocumento7 páginasDefinición de Soporte Técnico y Características PrincipalesMarcos CervantesAún no hay calificaciones

- Taller # 1 Organizador Gráfico Sistema de TransmisiónDocumento4 páginasTaller # 1 Organizador Gráfico Sistema de TransmisiónAlex Ortegano100% (1)

- Optimización de procesos químicos: Conjunto de problemas 2.1A y 2.2ADocumento9 páginasOptimización de procesos químicos: Conjunto de problemas 2.1A y 2.2ABUITRAGO VARGAS ANGIE TATIANAAún no hay calificaciones

- Neurable recauda $6M para BCI cotidianasDocumento5 páginasNeurable recauda $6M para BCI cotidianasCuarso // Cultura Arte SociedadAún no hay calificaciones

- Cálculo de peso máximo de cajas de chocolate con diferentes gramajesDocumento3 páginasCálculo de peso máximo de cajas de chocolate con diferentes gramajesAngel Valcarcel LopezAún no hay calificaciones

- Clases de ComputacionDocumento6 páginasClases de ComputacionDaimler DCAún no hay calificaciones