Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Piat Arquitectura Del PC

Cargado por

Chris CaballeroTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Piat Arquitectura Del PC

Cargado por

Chris CaballeroCopyright:

Formatos disponibles

Universidad Nacional Experimental

de los Llanos Occidentales

“Ezequiel Zamora”

CONTENIDO PROGRAMÁTICO DEL SUBPROYECTO:

ARQUITECTURA DEL COMPUTADOR

VICERRECTORADO: Planificación y Desarrollo Social

PROGRAMA: Ingeniería, Arquitectura y Tecnología

SUBPROGRAMA: Ingeniería en Informática

CARRERA: Ingeniería en Informática

ÁREA DE

CONOCIMIENTO: Formación Profesional Específica

PROYECTO: Electrónica del Computador y Comunicaciones

CÓDIGO: II51002060502

PRELACIÓN: Electrónica

HORAS SEMANALES: 5 Horas: 2 Horas Teóricas y 3 Horas Prácticas

UNIDADES CRÉDITO: 03

SEMESTRE: V

CONDICIÓN: Obligatoria (De naturaleza Especial)

PERFIL DEL Ingeniero en Redes y Comunicaciones, Ingeniero en Informática, Ingeniero

Electrónico, Licenciado en Computación, Ingeniero en Información, Licenciado en

DOCENTE: Informática, Ingeniero en Telecomunicaciones, Ingeniero en Computación, o afines

PROFESOR(ES) Prof. Darjeling Silva, Prof. Antonio Garcia y

DISEÑADOR(ES): Prof. Richard Zerpa

Barinas, Julio 2008

Contenido Programático del Subproyecto Arquitectura del Computador

Carrera Ingeniería en Informática

Página 1 de 8

JUSTIFICACIÓN

Este subproyecto se basará en lo que significa los procesadores y la

ingeniería de estos y así dar continuidad al subproyecto de electrónica, como se

señalo en esté ultimo subproyecto un procesador es una combinación de

dispositivos (eléctricos y fotoeléctricos), ensamblados a fin de desempeñar y

procesar distintas funciones. Asimismo los temas de la asignatura ampliarán,

complementará y profundizará los conocimientos adquiridos en subproyectos

previos, permitiendo, de esta forma, el alumno adquiera una base firme para su

futuro desarrollado profesional, detallado de las diferentes técnicas que se

utilizan en la actualidad.

OBJETIVO GENERAL

Conocer la metodología para realizar el diseño de circuitos con lógica

combinacional, funcionamiento y aplicación de los circuitos integrados más

importantes empleados en el diseño lógico y por último describir la estructura

interna de un CPU y los tipos de arquitecturas que existen.

OBJETIVOS ESPECÍFICOS

Conocer el esquema básico de un Microprocesador.

Definir los tipos de Arquitectura: Secuencial y Paralela.

Conocer el procesamiento en pipeline (Segmentación).

Diferenciar las Arquitecturas RISC y CISC.

Contenido Programático del Subproyecto Arquitectura del Computador

Carrera Ingeniería en Informática

Página 2 de 8

MÓDULO I: ESUEMA BÁSICO DE UN MICROPROCESADOR

Duración 3 semanas

Valor 20%

Objetivo Específico

1. Conocer el esquema básico de un Microprocesador.

2. Definir los tipos de Arquitectura: Secuencial y Paralela.

Contenido

Arquitectura de Von Neuman.

Definición basada en tiempo de ejecución y productividad.

Ciclos de reloj por instrucción, y demás componentes del rendimiento.

Aceleración del tiempo de ejecución y formas de obtenerla: mejoras

tecnológicas, mejoras en arquitectura y en organización; y empleo de la

computación en paralelo.

La jerarquía de las memorias y su importancia.

Arquitecturas Paralelas

Taxonomía del paralelismo y las arquitecturas paralelas

Paralelismo espacial y temporal

Medidas de rendimiento

Arquitecturas de bus común

Consistencia de memoria y coherencia cache

Modelos de programación.

Estrategias Metodológicas

Clase teóricas y

Prácticas dirigidas.

Prueba escrita y práctica.

Técnicas dinámica de grupos.

Trabajo de investigación.

Contenido Programático del Subproyecto Arquitectura del Computador

Carrera Ingeniería en Informática

Página 3 de 8

MÓDULO II: PROCESAMIENTO EN

“PIPELINE” (SEGMENTACIÓN)

Duración 3 semanas

Valor 15%

Objetivos Específicos

1. Conocer el procesamiento en pipeline (Segmentación).

2. Diferenciar las Arquitecturas RISC y CISC.

Contenido

Conceptos básicos, cálculo de la mejora que introduce; aceleración,

rendimiento y productividad.

Clasificación de sistemas en “pipeline”.

Ejemplos de “pipelines” operativos y “pipelines” de instrucciones.

Análisis de las limitaciones del “pipeline” real: riesgos y sus distintos

tipos: por dependencia de datos, por dependencia de control, por

colisiones.

Análisis de casos en procesadores típicos.

Computadores de Conjunto de Instrucciones Reducido (“RISC”).

Arquitectura RISC y sus características. Ejemplos. “Pipelines” en

arquitecturas RISC, saltos “retardados”

Controversia entre RISC y CISC

Estrategias Metodológicas

Clase teóricas y

Prácticas dirigidas.

Prueba escrita y práctica.

Técnicas dinámica de grupos.

Contenido Programático del Subproyecto Arquitectura del Computador

Carrera Ingeniería en Informática

Página 4 de 8

MÓDULO III: PARALELISMO - MULTIPROCESADOR

Duración 3 semanas

Valor 15%

Objetivos Específicos

Definir y conocer el paralelismo en las instrucciones.

Contenido

¿Qué es el paralelismo entre instrucciones?

Limitaciones del paralelismo entre instrucciones

Procesadores superescalares

Ejecución fuera de orden frente a ejecución en orden

Renombrado de registros

Procesadores VLIW

Paralelismo y granularidad.

Clasificación de FLYNN para sistemas computadores: análisis

comparativo de los diferentes tipos.

Técnicas de compilación para mejorar el paralelismo entre instrucciones

Ganancia en velocidad y prestaciones

Sistemas multiprocesador

Sistemas de paso de mensajes

Sistemas de memoria compartida

Comparación entre el paso de mensajes y la memoria compartida

Estrategias Metodológicas

Clases prácticas dirigidas.

Técnicas dinámica de grupos.

Prueba Práctica

Contenido Programático del Subproyecto Arquitectura del Computador

Carrera Ingeniería en Informática

Página 5 de 8

MÓDULO IV: COMPUTADORES VECTORIALES Y

MATRICIALES

Duración 3 semanas

Valor 20%

Objetivos Específicos

1. Definir la computación vectorial.

2. Conocer los procesadores matriciales.

Contenido

Principio general, arquitectura y organización de super computadores

vectoriales basados en “pipelines”.

Análisis de ejemplos típicos y de su influencia sobre la evolución de las

arquitecturas.

Computadores matriciales del tipo SIMD: diferencias con los

computadores “vectoriales”.

Consideraciones sobre rendimiento y ley de Amdahl.

Estrategias Metodológicas

Clase prácticas dirigidas.

Prueba práctica.

Técnicas dinámica de grupos.

Contenido Programático del Subproyecto Arquitectura del Computador

Carrera Ingeniería en Informática

Página 6 de 8

MÓDULO V: MODELOS DE PROGRAMACIÓN DEFINIDOS POR

LAS LIBRERÍAS ESTÁNDARES MPI, PVM

Duración 4 semanas

Valor 30%

Objetivos Específicos

Conocer los modelos de programación paralela o software paralelo

Contenido

Bibliotecas de funciones de pasaje de mensajes: “PVM” (Parallel Virtual

Machine) y “MPI” (Message Passing Interface); funciones de comunicación

punto a punto y colectivas: principios del uso de esos recursos.

Bases del diseño de algoritmos paralelos: partición, comunicación,

aglomeración, y “mapping”.

Creación de programas simples en ambientes MPI o PVM: ejemplos y práctica

en una red disponible.

Estrategias Metodológicas

Prácticas dirigidas.

Técnicas dinámica de grupos.

Examen Práctico

Contenido Programático del Subproyecto Arquitectura del Computador

Carrera Ingeniería en Informática

Página 7 de 8

BIBLIOGRAFÍA

• Hamacher, C. Vranesic, Z. Zaky, S. (2003). Organización de computadores.

España: McGraw-Hill.

• Mandado, E. (1992). Sistemas electrónicos digitales. México: Alfaomega,

Marcombo.

• Martinez G., Olivera J., Agustín J. (2000). Organización y Arquitectura de

Computadores.

• Morris, M. (1994). Arquitectura de computadoras. México: Pretince-Hall.

• Preparata, F. (1987). Introducción a la ingeniería en computación. México:

Harla.

• Stallings, W. (2000). Organización y arquitectura de computadores : diseño

para optimizar prestaciones. Edición 5ª. Prentice Hall.

• Hwang K. y Briggs F. (1988). Arquitectura de Computadores y Procesamiento

Paralel. McGraw-Hill.

Contenido Programático del Subproyecto Arquitectura del Computador

Carrera Ingeniería en Informática

Página 8 de 8

También podría gustarte

- 0436505T - Organizaciòn Del Computador - Analitico y SipnoticoDocumento8 páginas0436505T - Organizaciòn Del Computador - Analitico y SipnoticoeavsequeraAún no hay calificaciones

- C4E AcoDocumento21 páginasC4E AcoMariana FagandiniAún no hay calificaciones

- Sisope PDFDocumento13 páginasSisope PDFChris CaballeroAún no hay calificaciones

- 710192M - Arquitectura de Computadores 1Documento2 páginas710192M - Arquitectura de Computadores 1LUIS GERMAN TORO PAREJAAún no hay calificaciones

- If 0503 Arquitectura de Com Put AdoresDocumento11 páginasIf 0503 Arquitectura de Com Put AdoresYeny Candida Cahuana HuarcayaAún no hay calificaciones

- ArquitecturaComputadorDocumento6 páginasArquitecturaComputadorpaula.ossaAún no hay calificaciones

- SAF-1314 Electronica DigitalDocumento8 páginasSAF-1314 Electronica DigitalCesar EspinozaAún no hay calificaciones

- I.T.S.C.S.: Syllabus de Arquitectura IDocumento13 páginasI.T.S.C.S.: Syllabus de Arquitectura IGUILLEN ROMANI CARLOS ALBERTOAún no hay calificaciones

- Electrónica Informática UNELLEZDocumento9 páginasElectrónica Informática UNELLEZFrancisco FernándezAún no hay calificaciones

- Arquitectura Del SoftwareDocumento10 páginasArquitectura Del SoftwareJose Antonio Cabrera RamosAún no hay calificaciones

- PLANIFICACIONDocumento13 páginasPLANIFICACIONjavierAún no hay calificaciones

- Syllabus EE681MDocumento4 páginasSyllabus EE681MDavidAún no hay calificaciones

- Microprocesadores 1Documento9 páginasMicroprocesadores 1RG JKariAún no hay calificaciones

- Arquitectura de Computadoras IS461Documento15 páginasArquitectura de Computadoras IS461Darwin Jhordan Salazar LlanosAún no hay calificaciones

- Programa Introducción A La InformáticaDocumento14 páginasPrograma Introducción A La InformáticaLuis Eliseo Castellano A.100% (1)

- Programa - Planificacion - Programacion en Computación - 2019Documento18 páginasPrograma - Planificacion - Programacion en Computación - 2019Leonel SterbaAún no hay calificaciones

- Programa Planificacion Programacion en Computación 2019Documento18 páginasPrograma Planificacion Programacion en Computación 2019Fabricio AlfaroAún no hay calificaciones

- Programacion Orientada A ObjetosDocumento9 páginasProgramacion Orientada A ObjetosJuan SantiagoAún no hay calificaciones

- PLAN DE ASIGNATURA Arquitectura de Computadores 2021 - IDocumento7 páginasPLAN DE ASIGNATURA Arquitectura de Computadores 2021 - ILeiderAún no hay calificaciones

- Arquitectura ComputadoresDocumento3 páginasArquitectura ComputadoresLaura HuecaAún no hay calificaciones

- Esp Computo Alto Rendimiento Tomo IIDocumento41 páginasEsp Computo Alto Rendimiento Tomo IIVar VarAún no hay calificaciones

- UNEDDocumento20 páginasUNEDHéctor Tadeo100% (1)

- Plan de Curso MicroprocesadoresDocumento7 páginasPlan de Curso MicroprocesadoresRodrigo Vela PérezAún no hay calificaciones

- Arquitectura de Computadoras IiDocumento9 páginasArquitectura de Computadoras IiMiguel MoyaAún no hay calificaciones

- Algoritmos y Programación I (1395)Documento4 páginasAlgoritmos y Programación I (1395)Dayana MejiaAún no hay calificaciones

- Doctorado en InformaticaDocumento1 páginaDoctorado en InformaticaEdgar Mauricio Lopez RojasAún no hay calificaciones

- Universidad Mayor de San Andrés Facultad de Ingeniería - Ingeniería Electrónica Doc. MSC - Ing. Jorge Mario Leon GomezDocumento5 páginasUniversidad Mayor de San Andrés Facultad de Ingeniería - Ingeniería Electrónica Doc. MSC - Ing. Jorge Mario Leon GomezJhoel VrtAún no hay calificaciones

- Informatica Telecomunicaciones PDFDocumento5 páginasInformatica Telecomunicaciones PDFDanyeell GmezAún no hay calificaciones

- Migración de prácticas de TOC a plataforma FPGA de bajo coste IceZUMDocumento7 páginasMigración de prácticas de TOC a plataforma FPGA de bajo coste IceZUMJosé Manuel Ortiz RodriguezAún no hay calificaciones

- Silabo Arquitectura de Computadoras 2021-1Documento8 páginasSilabo Arquitectura de Computadoras 2021-1AdolfoAún no hay calificaciones

- Malla Curricular Atlantida HondurasDocumento46 páginasMalla Curricular Atlantida Hondurasjocrima75% (4)

- Paralel oDocumento7 páginasParalel oManuel CastañedaAún no hay calificaciones

- APM74 Algoritmos y ProgramacionDocumento5 páginasAPM74 Algoritmos y ProgramacionCorporacion Corfes Fortalecimiento EmpresarialAún no hay calificaciones

- Arquitectura Computadoras UNPRGDocumento10 páginasArquitectura Computadoras UNPRGElias GasteloAún no hay calificaciones

- 8 Microprocesadores y Microcontroladores PDF PDFDocumento7 páginas8 Microprocesadores y Microcontroladores PDF PDFVicente Borja JaimesAún no hay calificaciones

- Circuitos Lógicos SecuencialesDocumento10 páginasCircuitos Lógicos SecuencialeschristianFPTAún no hay calificaciones

- Arquitectura y Organización Del ComputadorDocumento39 páginasArquitectura y Organización Del ComputadorLuigiCastroAlvisAún no hay calificaciones

- Arquitectura de ComputadorasDocumento11 páginasArquitectura de ComputadorasAlexander BaldecAún no hay calificaciones

- Circuitos Digitales EspolDocumento4 páginasCircuitos Digitales EspolByron MotocheAún no hay calificaciones

- Arquitectura de As II REE - 0803Documento12 páginasArquitectura de As II REE - 0803Roy PérezAún no hay calificaciones

- Sistemas Digitales II EspolDocumento4 páginasSistemas Digitales II EspolByron MotocheAún no hay calificaciones

- Modelado Virtual TemarioDocumento14 páginasModelado Virtual TemarioEliel Carreto Moreno0% (1)

- TIC SYLLABUS - M RamonDocumento9 páginasTIC SYLLABUS - M RamonLucyReyesAún no hay calificaciones

- Temario Organización de ComputadorasDocumento13 páginasTemario Organización de ComputadorasCarlosAún no hay calificaciones

- 1 Sistemas de Microprocesadores PDFDocumento2 páginas1 Sistemas de Microprocesadores PDFOmar CedeñoAún no hay calificaciones

- Arquitectura de Computadoras IPNDocumento11 páginasArquitectura de Computadoras IPNEdgar VillarrealAún no hay calificaciones

- Academia de Desarrollo 2023 - Módulo 1Documento71 páginasAcademia de Desarrollo 2023 - Módulo 1pedroAún no hay calificaciones

- Resumen Programaciones 1 BACHILLERATODocumento4 páginasResumen Programaciones 1 BACHILLERATOCORAL ALONSO JIMÉNEZAún no hay calificaciones

- Prog Analitico Eln 352 Fac - Tecnol.Documento7 páginasProg Analitico Eln 352 Fac - Tecnol.Eliot BalcazarAún no hay calificaciones

- Estructuras Computacionales: Conceptos y Herramientas BásicasDocumento5 páginasEstructuras Computacionales: Conceptos y Herramientas BásicasESTUDIANTEAún no hay calificaciones

- Microcontroladores PDFDocumento8 páginasMicrocontroladores PDFEmerson Otálora DíazAún no hay calificaciones

- Electronica_Aplicada_InformaticaDocumento20 páginasElectronica_Aplicada_InformaticaErmaBlanesVialeAún no hay calificaciones

- Electronic A DigitalDocumento16 páginasElectronic A DigitalRichard CLAún no hay calificaciones

- Programacion Paralela y ConcurrenteDocumento4 páginasProgramacion Paralela y ConcurrenteJuan Carlos ZeusAún no hay calificaciones

- Introducción A La Computación NivelacionDocumento9 páginasIntroducción A La Computación Nivelacionsamuel roblesAún no hay calificaciones

- SyllabusDocumento10 páginasSyllabusOSCAR ANTONIO MARTINEZ CENDALESAún no hay calificaciones

- Mecatrónica - sistemas de control electrónico en la ingeniería mecánica y eléctricaDe EverandMecatrónica - sistemas de control electrónico en la ingeniería mecánica y eléctricaCalificación: 5 de 5 estrellas5/5 (3)

- Fundamentals of industrial communications in automationDe EverandFundamentals of industrial communications in automationAún no hay calificaciones

- Curso de Programación y Análisis de Software - 2ª EdiciónDe EverandCurso de Programación y Análisis de Software - 2ª EdiciónAún no hay calificaciones

- tesis_final_Bustos_y_teran_2324 (1)Documento96 páginastesis_final_Bustos_y_teran_2324 (1)Chris CaballeroAún no hay calificaciones

- LilianaDocumento6 páginasLilianaChris CaballeroAún no hay calificaciones

- GGDocumento7 páginasGGChris CaballeroAún no hay calificaciones

- Paradigma Imperativo Mod IIDocumento7 páginasParadigma Imperativo Mod IIChris CaballeroAún no hay calificaciones

- LilianaDocumento6 páginasLilianaChris CaballeroAún no hay calificaciones

- Go 6079Documento46 páginasGo 6079Chris CaballeroAún no hay calificaciones

- Go 40776Documento32 páginasGo 40776Chris CaballeroAún no hay calificaciones

- Temas Por DesarrollarDocumento1 páginaTemas Por DesarrollarChris CaballeroAún no hay calificaciones

- Fisica PDFDocumento186 páginasFisica PDFDaniel AscanioAún no hay calificaciones

- Auditoria hardware y software laboratorio informática UNELLEZDocumento37 páginasAuditoria hardware y software laboratorio informática UNELLEZLuis TorresAún no hay calificaciones

- Fisica PDFDocumento186 páginasFisica PDFDaniel AscanioAún no hay calificaciones

- Relacion de OrdenDocumento48 páginasRelacion de Ordenleviomat60% (5)

- Auditorc3ada Informc3a1tica IsnayaDocumento44 páginasAuditorc3ada Informc3a1tica IsnayaRenzo R.PonceAún no hay calificaciones

- Auditoria Mod I 1Documento20 páginasAuditoria Mod I 1Chris CaballeroAún no hay calificaciones

- Experiencia SC.-ElioDuranDocumento1 páginaExperiencia SC.-ElioDuranChris CaballeroAún no hay calificaciones

- Auditoria hardware y software laboratorio informática UNELLEZDocumento37 páginasAuditoria hardware y software laboratorio informática UNELLEZLuis TorresAún no hay calificaciones

- Guia de 2 Año TreminadaDocumento6 páginasGuia de 2 Año TreminadaChris CaballeroAún no hay calificaciones

- Experiencia SC.-ElioDuranDocumento1 páginaExperiencia SC.-ElioDuranChris CaballeroAún no hay calificaciones

- Programación con Papel Cuadriculado: Introducción a la ProgramaciónDocumento3 páginasProgramación con Papel Cuadriculado: Introducción a la ProgramaciónChris CaballeroAún no hay calificaciones

- Paradigma Declarativo ModDocumento3 páginasParadigma Declarativo ModChris CaballeroAún no hay calificaciones

- Guia de 2 Año TreminadaDocumento6 páginasGuia de 2 Año TreminadaChris CaballeroAún no hay calificaciones

- Nivel 3 AbsDocumento1 páginaNivel 3 AbsChris CaballeroAún no hay calificaciones

- Informe de Etica Profesional y de OdontologiaDocumento4 páginasInforme de Etica Profesional y de OdontologiaChris CaballeroAún no hay calificaciones

- 17 Libro de Todo Es Negociable PDFDocumento145 páginas17 Libro de Todo Es Negociable PDFMarco Antonio Do Rosario100% (1)

- Curso de gestión del tiempo: Matriz de priorizaciónDocumento1 páginaCurso de gestión del tiempo: Matriz de priorizaciónChris CaballeroAún no hay calificaciones

- Manual de Scrathito A MediasopdfDocumento19 páginasManual de Scrathito A MediasopdfChris CaballeroAún no hay calificaciones

- Sic2005675 231 PDFDocumento1 páginaSic2005675 231 PDFChris CaballeroAún no hay calificaciones

- Laboratorio N 03 - Caida Libre Con RejillaDocumento5 páginasLaboratorio N 03 - Caida Libre Con RejillaLuisJose Vereau AguileraAún no hay calificaciones

- Actitudes y MotivacionDocumento3 páginasActitudes y MotivacionJacqueLine Ingrid Perez SuasnabarAún no hay calificaciones

- Cuadro Comparativo Entre NIIF y Anteriores.Documento25 páginasCuadro Comparativo Entre NIIF y Anteriores.Jonathan FernandezAún no hay calificaciones

- Geoestadística Aplicación en La Caracterización de Yacimientos PDFDocumento49 páginasGeoestadística Aplicación en La Caracterización de Yacimientos PDFLuis Gustavo Choque Borda100% (1)

- Plan Circuital 1 PDFDocumento39 páginasPlan Circuital 1 PDFelkarboneroAún no hay calificaciones

- Presentacion de Power Point SilviaDocumento22 páginasPresentacion de Power Point SilviasilviatagerAún no hay calificaciones

- Tabla PeriódicaDocumento10 páginasTabla PeriódicajulieAún no hay calificaciones

- Verificacion Diaria de VehiculosDocumento3 páginasVerificacion Diaria de VehiculosJonathan Martinez GuerraAún no hay calificaciones

- Como Leer Un Diagrama ElectrónicoDocumento4 páginasComo Leer Un Diagrama ElectrónicoJaime PinedaAún no hay calificaciones

- UntitledDocumento1 páginaUntitledNutriservicios CandelariaAún no hay calificaciones

- Reglamento General Convocatoria 2023 MECENAZGODocumento31 páginasReglamento General Convocatoria 2023 MECENAZGOcami asconaAún no hay calificaciones

- Minerales IsotropicosDocumento17 páginasMinerales IsotropicosDiego Fonseca Peña0% (1)

- NEO-32 Máquinas Herramientas - Tornos Mecánicos y Fresadoras.Documento36 páginasNEO-32 Máquinas Herramientas - Tornos Mecánicos y Fresadoras.Paulo Diego AguileraAún no hay calificaciones

- Guía Pedagógica Del Módulo Diagnóstico y Servicio A Sistemas de Aire Acondicionado PDFDocumento55 páginasGuía Pedagógica Del Módulo Diagnóstico y Servicio A Sistemas de Aire Acondicionado PDFConalep VictoriaAún no hay calificaciones

- Como Crer Una Presentación en AutoCadDocumento5 páginasComo Crer Una Presentación en AutoCadRodrigo MegniniAún no hay calificaciones

- Cargador Frontal 994F CATDocumento32 páginasCargador Frontal 994F CATEduardo Segundo Gonzalez Muñoz100% (1)

- Estrés y AdaptaciónDocumento139 páginasEstrés y AdaptaciónConi VergaraAún no hay calificaciones

- Indicaciones del ayuno terapéutico: una revisión de sus beneficios para la saludDocumento13 páginasIndicaciones del ayuno terapéutico: una revisión de sus beneficios para la saludAlbert CalvetAún no hay calificaciones

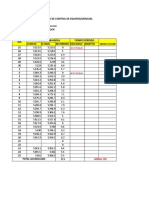

- 5 Control de Horometro MayoDocumento15 páginas5 Control de Horometro MayoFigueroa RichardAún no hay calificaciones

- Presupuesto de ventas y costos La Golosa SACDocumento18 páginasPresupuesto de ventas y costos La Golosa SACHosin CotaAún no hay calificaciones

- Plegable Aplicar Las Normas para La Redacci N de TextosDocumento2 páginasPlegable Aplicar Las Normas para La Redacci N de TextosVillabona JenniferAún no hay calificaciones

- Skate Holístico Un Breve Análisis de Soundboarding de Panayiotis KokorasDocumento2 páginasSkate Holístico Un Breve Análisis de Soundboarding de Panayiotis KokorasMaximilianoAún no hay calificaciones

- Manual Bomba UPADocumento16 páginasManual Bomba UPAGabrielBravoAún no hay calificaciones

- El Equilibrio de Starling para El Intercambio CapilarDocumento2 páginasEl Equilibrio de Starling para El Intercambio CapilarHelen AnguloAún no hay calificaciones

- API 650 Tanques de almacenamientoDocumento58 páginasAPI 650 Tanques de almacenamientoBrayan Verduguez AlcalaAún no hay calificaciones

- Planificacion SegmentoDocumento6 páginasPlanificacion SegmentonegrotucAún no hay calificaciones

- El Producto Bruto Interno y La Riqueza NacionalDocumento1 páginaEl Producto Bruto Interno y La Riqueza NacionalCesar Cotrina VargasAún no hay calificaciones

- 2012 Tesis Mantilla Gualdron Jose PabloDocumento79 páginas2012 Tesis Mantilla Gualdron Jose PabloAndrés AlarcónAún no hay calificaciones

- PRUEBA # 4 TÉCNICA DE SEGURIDADDocumento2 páginasPRUEBA # 4 TÉCNICA DE SEGURIDADJohn Jairo Bolivar OrtizAún no hay calificaciones

- 1SDA067391R1 xt1c 160 TMD 25 450 3p F FDocumento4 páginas1SDA067391R1 xt1c 160 TMD 25 450 3p F FRaul HernandezAún no hay calificaciones