Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Informe N7

Cargado por

Jefferson Guala FonsecaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Informe N7

Cargado por

Jefferson Guala FonsecaCopyright:

Formatos disponibles

INFORME N.

º 7

CP-SISTEMAS DIGITALES

FACULTAD DE INGENIERIA ELECTRICA Y ELECTRONICA

DISEÑO SSI

Nombre:

Gr: 8

Fecha: 22/07/2020

1. OBJETIVOS

1.1. Familiarizar al estudiante con la utilización y funcionamiento de circuitos lógicos

combinacionales que realizan operaciones binarias.

2. INFORME

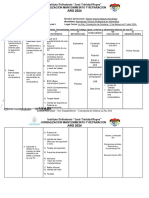

2.1. Para el demultiplexor de 1 a 4:

Realizar la tabla de verdad.

A B S0 S1 S2 S3

0 O 1 0 0 0

0 1 0 1 0 0

1 0 0 0 1 0

1 1 0 0 0 1

Tabla 1. Tabla de verdad del demultiplexor 1 a 4.

Encontrar los minterminos de la función.

S 0=m0

S 1=m 1

S 2=m 2

S 0=m3

Encontrar la función canónica.

S 0= Á B́

S 1= Á B

S 2= A B́

S 0= AB

Reducir la función canónica utilizando algebra de Boole.

S 0= Á B́

S 1= Á B

S 2= A B́

S 0= AB

Realizar el diagrama del circuito utilizando compuertas AON.

Figura 1. Demultiplexor 1 a 4.

2.2. Conclusiones.

El multiplexor permite distribuir los datos, el cual consta de un número de líneas de

entradas con una salida, respetando que el número de salidas es igual a dos

elevado al número de entradas (N) 2 N ,mientras que un demultiplexor realiza el

proceso inverso es decir distribuye los datos de 1 entrada a dos salidas, esto

respetando que el numero de salidas es 2 N .

Los sumadores realizan la suma aritmética de dos números enteros positivos, en

cazo del medio sumador este suma dos datos de un solo bit y producir un bit de

acarreo de salida.

2.3. Recomendaciones.

Entender el funcionamiento practico de un sumador y de un multiplexor, y luego

proceder al análisis matemático y su posterior simulación para que de esta manera

el desarrollo de la práctica se realice con éxito.

BIBLIOGRAFIA.

[1] TOCCI/WIDMER/MOSS. “Sistemas Digitales. Principios y Aplicaciones”. Prentice

Hall. 10ma. Edición. 2007.

También podría gustarte

- Problemas resueltos de Hidráulica de CanalesDe EverandProblemas resueltos de Hidráulica de CanalesCalificación: 4.5 de 5 estrellas4.5/5 (7)

- Manual IPI2winDocumento9 páginasManual IPI2winCristian Dominguez100% (2)

- Caracterización química, morfológica y estructural de materialesDe EverandCaracterización química, morfológica y estructural de materialesAún no hay calificaciones

- Chicaiza Intriago Práctica#7 InformeDocumento7 páginasChicaiza Intriago Práctica#7 InformeAlejandro Sebastian Chicaiza Tipan100% (1)

- Previo de Sumadores y RestadoresDocumento9 páginasPrevio de Sumadores y RestadoresCarlosAndresSolisChavezAún no hay calificaciones

- Previo de La Practica 7 de Sistemas Digitales (FESC-C4)Documento10 páginasPrevio de La Practica 7 de Sistemas Digitales (FESC-C4)Jesús GarcíaAún no hay calificaciones

- Práctica No 5 - Sumador y MultipleaxadoDocumento19 páginasPráctica No 5 - Sumador y MultipleaxadoMauricio Pazos100% (1)

- Gallardo Luis-Practica 1.6Documento10 páginasGallardo Luis-Practica 1.6Luis Javier GallardoAún no hay calificaciones

- L2 Jimenez BrendaDocumento11 páginasL2 Jimenez BrendaSilvana JimenezAún no hay calificaciones

- Aplicaciones de Circuitos MSIDocumento7 páginasAplicaciones de Circuitos MSIkevinAún no hay calificaciones

- LAB 02 - Simplificación de Funciones Lógicas TrerminadoDocumento7 páginasLAB 02 - Simplificación de Funciones Lógicas TrerminadoNahid Uriel Cayra MamaniAún no hay calificaciones

- Logica DigitalDocumento4 páginasLogica DigitalAlejandro Quinteros CabreraAún no hay calificaciones

- Experiencia IV - Circuitos DigitalesDocumento11 páginasExperiencia IV - Circuitos DigitalesIvan Rondinel BulejeAún no hay calificaciones

- Informe Laboratorio #6 SDDocumento9 páginasInforme Laboratorio #6 SDBenjo CalleAún no hay calificaciones

- Informe 4 - GRUPO 2Documento17 páginasInforme 4 - GRUPO 2Leo NogalesAún no hay calificaciones

- Practica 4 Sitemas DigitalesDocumento12 páginasPractica 4 Sitemas DigitalesAlessandra BernardoAún no hay calificaciones

- P7 Ruiz CHDocumento10 páginasP7 Ruiz CHJMartin Herdez TAún no hay calificaciones

- Informe de Mapas de KarnaughDocumento11 páginasInforme de Mapas de KarnaughBhily Quipo100% (1)

- Inf Prev 6Documento8 páginasInf Prev 6Ayrton Castro S.Aún no hay calificaciones

- Guia-7 Uso Del Mux y DemuxDocumento7 páginasGuia-7 Uso Del Mux y DemuxAlejandro GarriazoAún no hay calificaciones

- Informe de Laboratorio n.-6Documento3 páginasInforme de Laboratorio n.-6alexisAún no hay calificaciones

- Latorre Jhonny 2121 Lab. 5 EadDocumento29 páginasLatorre Jhonny 2121 Lab. 5 EadMNBVGCFRSTERBAún no hay calificaciones

- Reporte 3Documento5 páginasReporte 3Emmanuel TrujanoAún no hay calificaciones

- Sumador de 8 BiitsDocumento18 páginasSumador de 8 BiitsjuanAún no hay calificaciones

- LaboratorioCD1 L2Documento13 páginasLaboratorioCD1 L2ruben vilcaAún no hay calificaciones

- Compuertas Lógicas PDFDocumento43 páginasCompuertas Lógicas PDFStephMetalAún no hay calificaciones

- Informe 6 Vicente AlvarezDocumento17 páginasInforme 6 Vicente AlvarezVicente AlvarezAún no hay calificaciones

- Práctica #5Documento19 páginasPráctica #5Misshel BurgosAún no hay calificaciones

- Practica 5 - Funcion NandDocumento22 páginasPractica 5 - Funcion NandCarlos NuñezAún no hay calificaciones

- Laboratorio 1Documento13 páginasLaboratorio 1Elfrugele ViscarraAún no hay calificaciones

- Semaforo BinarioDocumento10 páginasSemaforo BinarioSUAREZ TORRES ANDREA ALEJANDRAAún no hay calificaciones

- Semaforo BinarioDocumento10 páginasSemaforo BinarioSUAREZ TORRES ANDREA ALEJANDRAAún no hay calificaciones

- Laboratorio #3 Circuitos LogicosDocumento7 páginasLaboratorio #3 Circuitos LogicosYira FernándezAún no hay calificaciones

- CUESTIONARIO FINAL 2 Digitales (Recuperado)Documento13 páginasCUESTIONARIO FINAL 2 Digitales (Recuperado)Renzo TuyoAún no hay calificaciones

- Practica 5 Electronica Digital..Documento7 páginasPractica 5 Electronica Digital..Juan Diego LMAún no hay calificaciones

- Lab05 2C5B Aritmetica Binaria MARCAQUISPEDocumento25 páginasLab05 2C5B Aritmetica Binaria MARCAQUISPEFlexXcat MiguelAún no hay calificaciones

- PracticasDocumento10 páginasPracticasErnesto Lopez AvilaAún no hay calificaciones

- Sumador Binario de 4 BitsDocumento12 páginasSumador Binario de 4 BitsEvaristo Camargo Esteban DoloresAún no hay calificaciones

- Lab #1 - Compuertas Lógicas - Tabla de Verdad (Recuperado Automáticamente)Documento5 páginasLab #1 - Compuertas Lógicas - Tabla de Verdad (Recuperado Automáticamente)ZAITAún no hay calificaciones

- Informe Lab9 DISPDocumento18 páginasInforme Lab9 DISPmicuantaAún no hay calificaciones

- Reporte de Practica de Los Sumadores y Flip Flop Tipo DDocumento21 páginasReporte de Practica de Los Sumadores y Flip Flop Tipo DAngel leon de jorgeAún no hay calificaciones

- Demultiplexor y MultiplexorDocumento6 páginasDemultiplexor y MultiplexorStwart EspinozaAún no hay calificaciones

- IDL2020 Pca2Documento7 páginasIDL2020 Pca2Electro MotiveAún no hay calificaciones

- Lab05 AritméticaBinariaDocumento9 páginasLab05 AritméticaBinariajulio enriqueAún no hay calificaciones

- L9 Simplificación de Funciones Lógicas 2005Documento20 páginasL9 Simplificación de Funciones Lógicas 2005GIOVANNI JOSE QUISPE ESPINOZAAún no hay calificaciones

- Electrónica HoyDocumento7 páginasElectrónica HoyRoberto Rafael Ospino Páez50% (2)

- LRT2022 10 08 08Documento10 páginasLRT2022 10 08 08Edir PerezAún no hay calificaciones

- Informe Coder MuxDocumento13 páginasInforme Coder MuxFabricio Veintimilla BautistaAún no hay calificaciones

- Práctica No 5 - 6EV2 - Sumador y MultipleaxadoDocumento19 páginasPráctica No 5 - 6EV2 - Sumador y MultipleaxadoObed GarcíaAún no hay calificaciones

- TEMA 4: SISTEMAS DIGITALES - Fundamentos de ComputadoresDocumento11 páginasTEMA 4: SISTEMAS DIGITALES - Fundamentos de ComputadoresFernando Meneses PovedaAún no hay calificaciones

- U3 Actividades Eca Digital Parte 3 PRINT PDFDocumento4 páginasU3 Actividades Eca Digital Parte 3 PRINT PDFMáximo Gómez GómezAún no hay calificaciones

- Calculadora Mux Demux INFORMEDocumento4 páginasCalculadora Mux Demux INFORMEMAVA SUAREZAún no hay calificaciones

- Lab #1 Compuertas LogicasDocumento5 páginasLab #1 Compuertas Logicassanes durangoAún no hay calificaciones

- M2.3 Practica3 Mapas Karnaugh Alcay ErikDocumento27 páginasM2.3 Practica3 Mapas Karnaugh Alcay ErikErik Xavier Alcay SanjuanAún no hay calificaciones

- InformelogicaDocumento3 páginasInformelogicaCarlos PardoAún no hay calificaciones

- Informe 9 FIIDocumento7 páginasInforme 9 FIIJonathan Harold Quevedo PulidoAún no hay calificaciones

- APUNTES y EJERCICIOS Sistemas Digitales (Fernando Martinez Moya) PDFDocumento19 páginasAPUNTES y EJERCICIOS Sistemas Digitales (Fernando Martinez Moya) PDFalmarpaAún no hay calificaciones

- LABORATORIO 1 Digitales.Documento5 páginasLABORATORIO 1 Digitales.Daniela Paez BoteroAún no hay calificaciones

- Informe Digitales 3Documento18 páginasInforme Digitales 3MiguelAngelOchoaBolanosAún no hay calificaciones

- Laboratorio ElectronicaDocumento16 páginasLaboratorio ElectronicaBrandacaAún no hay calificaciones

- Práctica 2 (Compuertas Lógicas)Documento13 páginasPráctica 2 (Compuertas Lógicas)JulianAún no hay calificaciones

- JeffersonGuala Semana2 Dia1 PDFDocumento4 páginasJeffersonGuala Semana2 Dia1 PDFJefferson Guala FonsecaAún no hay calificaciones

- Deber 3Documento1 páginaDeber 3Jefferson Guala FonsecaAún no hay calificaciones

- Historiasde UsuariosDocumento2 páginasHistoriasde UsuariosJefferson Guala FonsecaAún no hay calificaciones

- Informe N7Documento2 páginasInforme N7Jefferson Guala FonsecaAún no hay calificaciones

- INNFORME 3dsipositivosDocumento5 páginasINNFORME 3dsipositivosJefferson Guala FonsecaAún no hay calificaciones

- Deber 2Documento2 páginasDeber 2Jefferson Guala FonsecaAún no hay calificaciones

- Deber 1 CableadoDocumento1 páginaDeber 1 CableadoJefferson Guala FonsecaAún no hay calificaciones

- Preparatorio 2 DigitalesDocumento3 páginasPreparatorio 2 DigitalesJefferson Guala FonsecaAún no hay calificaciones

- INNFORME 3dsipositivosDocumento5 páginasINNFORME 3dsipositivosJefferson Guala FonsecaAún no hay calificaciones

- Prepa 3 DigitalesDocumento8 páginasPrepa 3 DigitalesJefferson Guala FonsecaAún no hay calificaciones

- INFORME 2 DigitalesDocumento5 páginasINFORME 2 DigitalesJefferson Guala FonsecaAún no hay calificaciones

- Algebra ReDocumento3 páginasAlgebra ReJefferson Guala FonsecaAún no hay calificaciones

- INFORME 2 DigitalesDocumento5 páginasINFORME 2 DigitalesJefferson Guala FonsecaAún no hay calificaciones

- EPNDiseñode AMpDocumento2 páginasEPNDiseñode AMpJefferson Guala FonsecaAún no hay calificaciones

- Diseño de Amplificador Con TBJDocumento2 páginasDiseño de Amplificador Con TBJJefferson Guala FonsecaAún no hay calificaciones

- InstagramDocumento4 páginasInstagramJefferson Guala FonsecaAún no hay calificaciones

- Preparatorio 8Documento2 páginasPreparatorio 8Jefferson Guala FonsecaAún no hay calificaciones

- Informe Regulador VoltajeDocumento3 páginasInforme Regulador VoltajeJefferson Guala FonsecaAún no hay calificaciones

- Preparatorio 8Documento2 páginasPreparatorio 8Jefferson Guala FonsecaAún no hay calificaciones

- Tarea 15Documento5 páginasTarea 15jeffersonAún no hay calificaciones

- EjercimathDocumento2 páginasEjercimathJefferson Guala FonsecaAún no hay calificaciones

- Informe Regulador VoltajeDocumento3 páginasInforme Regulador VoltajeJefferson Guala FonsecaAún no hay calificaciones

- Dispositivos de EntradaDocumento6 páginasDispositivos de EntradaJefferson Guala FonsecaAún no hay calificaciones

- La UsabilidadDocumento2 páginasLa UsabilidadjeffersonAún no hay calificaciones

- Deber 1Documento2 páginasDeber 1Jefferson Guala FonsecaAún no hay calificaciones

- Deber 1Documento2 páginasDeber 1Jefferson Guala FonsecaAún no hay calificaciones

- Deber 4Documento1 páginaDeber 4Jefferson Guala FonsecaAún no hay calificaciones

- Deber 3Documento1 páginaDeber 3Jefferson Guala FonsecaAún no hay calificaciones

- Deber 3Documento1 páginaDeber 3Jefferson Guala FonsecaAún no hay calificaciones

- JORNALIZACION MANTENIMIENTO Y REPARACION I Parcial 2023Documento5 páginasJORNALIZACION MANTENIMIENTO Y REPARACION I Parcial 2023wil1974Aún no hay calificaciones

- Resumen Pasantías - TECSUPDocumento19 páginasResumen Pasantías - TECSUPJorge ReyesAún no hay calificaciones

- HONOR 10 Lite Manual Del Usuario (HRY-LX1, EMUI9.0.1 - 01, ES) PDFDocumento92 páginasHONOR 10 Lite Manual Del Usuario (HRY-LX1, EMUI9.0.1 - 01, ES) PDFGabriel Fabiani CortesAún no hay calificaciones

- Versiones de Chrome OsDocumento5 páginasVersiones de Chrome OsDanMasAún no hay calificaciones

- Servicios RESTDocumento10 páginasServicios RESTalejandro piambaAún no hay calificaciones

- ETAP Sistemas de CuadrosDocumento2 páginasETAP Sistemas de Cuadrosdbogantesg9710Aún no hay calificaciones

- Redes de Computadores 10Documento7 páginasRedes de Computadores 10Hilda Paola Molina MaestreAún no hay calificaciones

- 1.2. Guía-Taller Crucigrama Recibo y DespachoDocumento4 páginas1.2. Guía-Taller Crucigrama Recibo y DespachoYülłïï Polania0% (1)

- Leame Zoo Tycoon 2Documento16 páginasLeame Zoo Tycoon 2jeremiasAún no hay calificaciones

- Como Abrir Un Archivo PDF en PaintDocumento2 páginasComo Abrir Un Archivo PDF en PaintRobinAún no hay calificaciones

- Matlab - Tarea 3Documento1 páginaMatlab - Tarea 3abcd1234ppAún no hay calificaciones

- Lab 02 - Herramientas de Software de ProgramaciónDocumento7 páginasLab 02 - Herramientas de Software de ProgramaciónAndre JacintoAún no hay calificaciones

- Metodos ProgramaciónDocumento9 páginasMetodos ProgramaciónyamejiaAún no hay calificaciones

- Diap - Wifi 6Documento19 páginasDiap - Wifi 6Soly Real YepezAún no hay calificaciones

- Python v12Documento154 páginasPython v12Luis Ibarguen MosqueraAún no hay calificaciones

- Infografía Caso ScrumDocumento1 páginaInfografía Caso ScrumSabastian SebastianAún no hay calificaciones

- Ejercicios Diagramas de Casos de UsosDocumento12 páginasEjercicios Diagramas de Casos de UsosCristian Rodriguez100% (1)

- EXO - F230 GG 02 ManualNbook SmartPro Q5Documento24 páginasEXO - F230 GG 02 ManualNbook SmartPro Q5Matías AlvarezAún no hay calificaciones

- Manual Windows AIKDocumento11 páginasManual Windows AIKBack BeatAún no hay calificaciones

- 370 MR TP 2019-2 - NFDocumento5 páginas370 MR TP 2019-2 - NFJosé Gregorio PérezAún no hay calificaciones

- Habilitar Permisos de Un Archivo o Una CarpetaDocumento2 páginasHabilitar Permisos de Un Archivo o Una Carpetafabian erazoAún no hay calificaciones

- GC-F-005 Formato Plantilla Word V01Documento3 páginasGC-F-005 Formato Plantilla Word V01AnabellyluAún no hay calificaciones

- Help Blophome ManualDocumento27 páginasHelp Blophome ManualMary GarciaAún no hay calificaciones

- sp4000 Manual de Instalacion MGSP Su14 PDFDocumento32 páginassp4000 Manual de Instalacion MGSP Su14 PDFMarcoAún no hay calificaciones

- Parte 2Documento23 páginasParte 2Daniel VeraAún no hay calificaciones

- Guia de Instalación Prezensa 2.4Documento29 páginasGuia de Instalación Prezensa 2.4Maria ChavezAún no hay calificaciones

- Configuracion GPRS WXP HT2000Documento11 páginasConfiguracion GPRS WXP HT2000gustavoleyriaAún no hay calificaciones

- Nangusé González Sergio RicardoDocumento114 páginasNangusé González Sergio RicardomariAún no hay calificaciones

- Control 2Documento20 páginasControl 2Javier OrtuñoAún no hay calificaciones