Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Sistemas Computacionales Sesion01 v1 1

Cargado por

Oscar Canchari OrunaDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Sistemas Computacionales Sesion01 v1 1

Cargado por

Oscar Canchari OrunaCopyright:

Formatos disponibles

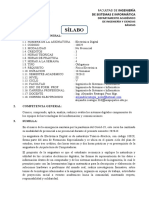

Diseño de Sistemas Computacionales para

Aplicación Específica

Sesión 01: Introducción al diseño

de sistemas digitales y

FPGAs

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

PRESENTACIÓN

Docente:

MSc. Miguel Angel Torres Lázaro

(e-mail: miguel.torres@maelpro.com)

Nombre del curso:

Diseño de sistemas computacionales para aplicación específica (100000I24N)

Frecuencia y duración:

6 horas p/semana

54 horas (9 semanas)

Pre-requisitos:

- Arquitectura del procesador digital de señales

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

PRESENTACIÓN

Estructura de las clases:

1) Preguntas sobre la clase anterior

2) Definiciones y conceptos

3) Desarrollo del tema

4) Preguntas

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

PRESENTACIÓN

Evaluación:

1) Prácticas calificadas: PC1, PC2, PC3, PC4, PC5

2) Examen final: EXFN

Promedio Final = (10xPC1 + 10xPC2 + 10xPC3 + 15xPC4 + 15xPC5 + 40xEXFN)

–-------------------------------------------------------------------------------------

100

Nota mínima aprobatoria: 12

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

PRESENTACIÓN

Logros del curso:

Al final del curso el estudiante estará en capacidad de:

●

Describir el comportamiento de un circuito digital mediante VHDL.

●

Diseñar soluciones de sistemas electrónicos y sintetizarlas en arreglos

de compuertas programables en campo (FPGAs).

●

Hacer uso de núcleos de propiedad intelectual (IP cores).

●

Diseñar núcleos de propiedad intelectual.

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

BIBLIOGRAFÍA

[1] Volnei A. Pedroni, Circuit Design with VHDL.

[2] Antonio Rubio, Josep Altet, Xavier Aragonés, José Luis Gonzales,

Diego Mateo, Francesc Moll, Diseño de circuitos y sistemas integrados..

[3] James O. Hamblen, Tyson S. Hall, Michael D. Furman , Rapid

Prototyping of Digital Systems SoPC Edition.

[4] Opencores. [Online] Disponible: http://www.opencores.org

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

Temario:

– Concepto de análisis y síntesis

– Síntesis de sistemas digitales

– Niveles de abstracción

– Lenguaje de descripción de hardware (HDL)

– Etapas en la síntesis automatizada de un sistema digital

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.1.- Síntesis de sistemas digitales

¿En qué consiste la síntesis de

sistemas digitales?

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.1.- Síntesis de sistemas digitales

Análisis f =(a . c )+(b . c)

Circuito físico Diagrama esquemático Descripción

f =(a . c )+( b . c)

Síntesis

Expresión Diseño Implementación

lógica/matemática (Diagrama esquemático) (Circuito físico)

(Descripción)

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.1.- Síntesis de sistemas digitales

a=sck (t−1 )

b=sck (t−2 )

sckfall=a . b

Descripción Diseño Implementación

assign sck_fall = ~a & b;

always@(posedge clk)

begin

a <= sck;

b <= a;

end

Descripción Diseño Implementación

(HDL) (RTL) (CPLD / FPGA)

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.2.- Síntesis automatizada

PLD

Editor de Sintetizador

texto Inicial

Simulador Sintetizador Sintetizador de

(funcional) Lógico Disposición

Simulador Generador de ...101100...

(Tiempo) secuencia de bits

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.3.- Niveles de abstracción

Nivel sistema

(organizado en bloques) F

l

e

S x

i i

m Nivel transferencia de registros

(RTL) b

p i

l l

i i

c Nivel lógico d

i (basado en compuertas)

a

d d

a

d Nivel compuerta

(basado en transistores)

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.3.- Niveles de abstracción

En diseño digital, un nivel de abstracción es un nivel de detalle con el cual se puede

describir un sistema digital.

Un sistema digital puede representarse a diferentes niveles, entre los principales tenemos:

Sistema

Define particiones de diseño y sus interfaces.

Algoritmo

Modela el comportamiento con un “lenguaje de programación” de alto nivel.

RTL (Register Transfer Level)

Define una “microarquitectura”, separando las partes de control y ruta de datos.

Lógica

Define el comportamiento de componentes RTL con ecuaciones booleanas.

Compuerta

Implementa el comportamiento de las compuertas lógicas con estructuras basadas en

transistores.

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.4.- Lenguaje de descripción de hardware (HDL)

Lenguajes de descripción de hardware (HDL) estándar.

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.4.- Lenguaje de descripción de hardware (HDL)

Ejemplo implementado en VHDL y Verilog.

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.4.- Lenguaje de descripción de hardware (HDL)

Lenguajes estándar en la industria de desarrollo de sistemas digitales.

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.5.- Sintetizador inicial

input a, b,c;

output f;

assign f = (~a & ~b & c) |

(a & ~b & ~c) |

(a & ~b & c) |

(a & b & ~c);

HDL RTL

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.6.- Sintetizador lógico

Traducción literal Versión optimizada

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.7.- Sintetizador de disposición

Lógica (RTL) Ubicación e interconexiones

en hardware (Netlist)

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.8.- Generador de secuencia de bits

11000000000011

00000010100001

00000010100011

00100000100010

00011110100011

...

Netlist Secuencia de bits

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.9.- Simulador

Simulación en el tiempo

Simulación funcional

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.9.- Simulador

¿Por qué es necesaria una simulación en el tiempo?

EJEMPLO:

Condición de carrera

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

1.- CONCEPTOS Y DEFINICIONES

1.9.- Simulador

PLD

Editor de Sintetizador

texto Inicial

Simulador Sintetizador Sintetizador de

(funcional) Lógico Disposición

Simulador Generador de ...101100...

(Tiempo) secuencia de bits

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

2.- PRÁCTICA

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

2.- PRÁCTICA

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

2.- PRÁCTICA

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

3.- RESUMEN

Análisis y síntesis

Análisis:

Síntesis:

Lenguajes de descripción de hardware (estándares)

-

-

Etapas de la síntesis automatizada de sistemas digitales:

1)

2)

3)

4)

5)

6)

Sesión 01 – Introducción Miguel A. Torres Lázaro

Diseño de Sistemas Computacionales para

Aplicación Específica

4.- PREGUNTAS

Sesión 01 – Introducción Miguel A. Torres Lázaro

También podría gustarte

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- UF0852 - Instalación y actualización de sistemas operativosDe EverandUF0852 - Instalación y actualización de sistemas operativosCalificación: 5 de 5 estrellas5/5 (1)

- Sistemas Computacionales Sesion02 v1Documento30 páginasSistemas Computacionales Sesion02 v1Oscar Canchari OrunaAún no hay calificaciones

- Arquitectura de Computadoras - Semana 1Documento12 páginasArquitectura de Computadoras - Semana 1Victor Junco RenteraAún no hay calificaciones

- Design FPGADocumento18 páginasDesign FPGALorena GinardAún no hay calificaciones

- Arquitectura Semana 1Documento92 páginasArquitectura Semana 1Victor Junco RenteraAún no hay calificaciones

- SilaboDocumento8 páginasSilabofernando francia peraltaAún no hay calificaciones

- Utn-Sistemas-Modalidad Académica 2021 Arquitectura de ComputadorasDocumento24 páginasUtn-Sistemas-Modalidad Académica 2021 Arquitectura de ComputadorasAbraham JohnsonAún no hay calificaciones

- Silabo 2023-II ARQUITECTURA Y ORGANIZACIÓN DE COMPUTADORAS ADocumento7 páginasSilabo 2023-II ARQUITECTURA Y ORGANIZACIÓN DE COMPUTADORAS AAlhex MbsAún no hay calificaciones

- Programa Elt 362 15Documento6 páginasPrograma Elt 362 15Rodri GoAún no hay calificaciones

- Top DownDocumento12 páginasTop DownjairGlzAún no hay calificaciones

- Modulo 1Documento48 páginasModulo 1Maryoris BlancoAún no hay calificaciones

- Arquitectura de Computadoras - Semana 5Documento75 páginasArquitectura de Computadoras - Semana 5Victor Junco RenteraAún no hay calificaciones

- AlgoritmosDocumento55 páginasAlgoritmosOscar MirandaAún no hay calificaciones

- T109 - 06 - Programa Sistemas de Computación II (2022) v04Documento10 páginasT109 - 06 - Programa Sistemas de Computación II (2022) v04Valentín RegalAún no hay calificaciones

- Tema 1Documento39 páginasTema 1José Burgos MirasAún no hay calificaciones

- Circuitos Digitales y MicroprocesadoresDocumento74 páginasCircuitos Digitales y MicroprocesadoresPeri MaximilianoAún no hay calificaciones

- Silabus de Sistemas DigitalesDocumento5 páginasSilabus de Sistemas DigitalesFrank Chavez LinaresAún no hay calificaciones

- Repaso Arqutecturas de ComputadoresDocumento83 páginasRepaso Arqutecturas de ComputadoresSergio Ruben FloresAún no hay calificaciones

- Gmv-Ft-1638-Controladores Lógicos Programables (PLC)Documento2 páginasGmv-Ft-1638-Controladores Lógicos Programables (PLC)Rey RodriguezAún no hay calificaciones

- Arquitectura 2021 Clase 0 - IntroducciónDocumento7 páginasArquitectura 2021 Clase 0 - IntroducciónMeli MonteroAún no hay calificaciones

- ALGORITMOSDocumento21 páginasALGORITMOSgimena weisheimAún no hay calificaciones

- Paper JSDocumento7 páginasPaper JSJosé Manuel Ortiz RodriguezAún no hay calificaciones

- TPC - Plan de Estudios y Contenidos MinimosDocumento5 páginasTPC - Plan de Estudios y Contenidos MinimosSuárez al DíaAún no hay calificaciones

- Algoritmos y Lógica de ProgramaciónDocumento14 páginasAlgoritmos y Lógica de ProgramaciónMikasa AckermanbbAún no hay calificaciones

- Introducción A La Estructura de ComputadoresDocumento272 páginasIntroducción A La Estructura de ComputadoresAxel KürtenAún no hay calificaciones

- PF0451 Mantenimiento de Redes e InfraestructuraDocumento18 páginasPF0451 Mantenimiento de Redes e InfraestructuraCapacitaciones CaitecAún no hay calificaciones

- Prog Analitico QuimicaDocumento14 páginasProg Analitico QuimicaWilliam HarrisAún no hay calificaciones

- Sistemas Digitales VHDLDocumento70 páginasSistemas Digitales VHDLJeo HkAún no hay calificaciones

- Silabo IntroduccionDocumento5 páginasSilabo IntroduccionIván Soria SolísAún no hay calificaciones

- Silabo de Electronica Digital 2020 - Ii - V1Documento13 páginasSilabo de Electronica Digital 2020 - Ii - V1HugoAún no hay calificaciones

- Diseño de ALUDocumento7 páginasDiseño de ALULeviatánBeluzAún no hay calificaciones

- Informatica Basica: Examen de Microsoft WordDocumento9 páginasInformatica Basica: Examen de Microsoft WordAlexAún no hay calificaciones

- Transparencias Tema 3 Diseno Orientado A ObjetosDocumento61 páginasTransparencias Tema 3 Diseno Orientado A ObjetosEzequiel JiménezAún no hay calificaciones

- Circuitos Digitales EspolDocumento4 páginasCircuitos Digitales EspolByron MotocheAún no hay calificaciones

- Modulo 27062021Documento2 páginasModulo 27062021Juan FerrerAún no hay calificaciones

- Presentación Curso Programación de Plcs Basico M221 PDFDocumento50 páginasPresentación Curso Programación de Plcs Basico M221 PDFJheicot Paredes JaldinAún no hay calificaciones

- Module01 Lec02 V2 2Documento48 páginasModule01 Lec02 V2 2Raul SantosAún no hay calificaciones

- Tema1 Var InstruccionesDocumento108 páginasTema1 Var InstruccionesDiego Alejandro Perdomo HerreraAún no hay calificaciones

- M3-Programación Orientada A Objetos PDFDocumento26 páginasM3-Programación Orientada A Objetos PDFCarmen castillo lopezAún no hay calificaciones

- Informe 7 Teclado VHDLDocumento2 páginasInforme 7 Teclado VHDLCatalina GonzálezAún no hay calificaciones

- AIC Tema 1Documento16 páginasAIC Tema 1GianfrancoPBAún no hay calificaciones

- Uso Didactico Del ProteusDocumento6 páginasUso Didactico Del Proteusruben posadasAún no hay calificaciones

- 01 Introduccionx2Documento32 páginas01 Introduccionx2ricardoruizfdezAún no hay calificaciones

- Silabo Electrónica DigitalDocumento6 páginasSilabo Electrónica DigitalGuido MartinezAún no hay calificaciones

- L 6 - Esquema Numérico 3Documento2 páginasL 6 - Esquema Numérico 3Diego Alejandro Vargas HuayancaAún no hay calificaciones

- Fase 2 Documento Proyecto MySDocumento4 páginasFase 2 Documento Proyecto MySNayeli Denise Abigail Aburto MarchenaAún no hay calificaciones

- Laboratorio de RedesDocumento12 páginasLaboratorio de RedesESTHER PLUAAún no hay calificaciones

- Diseño de Circuitos Lógicos CombinacionalesDocumento6 páginasDiseño de Circuitos Lógicos CombinacionalesPEDRO DAVID PESANTEZ PESANTEZAún no hay calificaciones

- Programa IASDocumento4 páginasPrograma IASRichard HansenAún no hay calificaciones

- 06 Guia de Laboratorio 3.10Documento2 páginas06 Guia de Laboratorio 3.1020 MAYOR PNP SALAS VILLAFUERTE EdisonAún no hay calificaciones

- Syllabus Procesamiento Digital de SeñalesDocumento6 páginasSyllabus Procesamiento Digital de SeñalesSteven RoseroAún no hay calificaciones

- Tema 1. Introducción A La Arquitectura de Computadores: Diseño, Coste y RendimientoDocumento16 páginasTema 1. Introducción A La Arquitectura de Computadores: Diseño, Coste y RendimientoRigoberto LariosAún no hay calificaciones

- Arquitectura de Computadores y LaboratorioDocumento5 páginasArquitectura de Computadores y Laboratorioestefania.perez.2000Aún no hay calificaciones

- Silabo 2023-II INTRODUCCIÓN A LA INGENIERÍA DE SISTEMAS Y COMPUTACIÓN ADocumento8 páginasSilabo 2023-II INTRODUCCIÓN A LA INGENIERÍA DE SISTEMAS Y COMPUTACIÓN AYared AmirAún no hay calificaciones

- Cacic 2013Documento7 páginasCacic 2013Eduardo KunyszAún no hay calificaciones

- CC51A Clase10 Documento de DisenoDocumento45 páginasCC51A Clase10 Documento de DisenoMary Fernando R. MartinezAún no hay calificaciones

- UF0853 - Explotación de las funcionalidades del sistema microinformáticoDe EverandUF0853 - Explotación de las funcionalidades del sistema microinformáticoAún no hay calificaciones

- UF0307 - Representación Gráfica y maquetismoDe EverandUF0307 - Representación Gráfica y maquetismoCalificación: 2 de 5 estrellas2/5 (1)

- Fundamentals of industrial communications in automationDe EverandFundamentals of industrial communications in automationAún no hay calificaciones

- Semana 4 - Teoría de La Producción Corto y Largo PlazoDocumento25 páginasSemana 4 - Teoría de La Producción Corto y Largo PlazoLuis Anthony Montoya QuispeAún no hay calificaciones

- Informe Técnico Ampliatorio Alca - MontegrandeDocumento7 páginasInforme Técnico Ampliatorio Alca - MontegrandeJulio Mazza CallirgosAún no hay calificaciones

- Kevin Durant PDFDocumento7 páginasKevin Durant PDFElias Rodriguez MadridAún no hay calificaciones

- Ejercicio de Nivelacion Control InternoDocumento11 páginasEjercicio de Nivelacion Control InternoAris Arturo Córdova CamposAún no hay calificaciones

- Modulo de Danza Folklorica EcuatorianaDocumento99 páginasModulo de Danza Folklorica EcuatorianaMariella Centeno JaureguiAún no hay calificaciones

- NURS 2730 Tarea 7.1Documento6 páginasNURS 2730 Tarea 7.1JENNIFER ROMANAún no hay calificaciones

- SAIME - Trámites LeninDocumento2 páginasSAIME - Trámites LeninPytronic CAAún no hay calificaciones

- Manual de FuncionesDocumento17 páginasManual de FuncionesValentina Martinez100% (8)

- Formato Solicitud de Empleo WordDocumento2 páginasFormato Solicitud de Empleo WordLuis Pedraza100% (1)

- Cantos para PentecostesDocumento7 páginasCantos para PentecostesPablo HernándezAún no hay calificaciones

- Tarea 2 Condiciones Previas de La EntrevistaDocumento7 páginasTarea 2 Condiciones Previas de La Entrevistayisus CisCAAún no hay calificaciones

- Ciclo Estral y Gestación de Conejos, Cuyes y PorcinosDocumento11 páginasCiclo Estral y Gestación de Conejos, Cuyes y PorcinosCristina ÑacataAún no hay calificaciones

- Solicitud KX 24017Documento38 páginasSolicitud KX 24017J Fer TelloAún no hay calificaciones

- Reglamento Academico 1Documento72 páginasReglamento Academico 1terrerojohanna030Aún no hay calificaciones

- Aristóteles - Poética (Ed. Alianza)Documento62 páginasAristóteles - Poética (Ed. Alianza)hurracapepe92% (36)

- Parálisis FacialDocumento4 páginasParálisis FacialEzeBorjesAún no hay calificaciones

- Instructivo VenappDocumento6 páginasInstructivo VenappalexisAún no hay calificaciones

- Li25 Ficha - de - Ejercicios - Mov. - Parabolico - Docx LisssssDocumento2 páginasLi25 Ficha - de - Ejercicios - Mov. - Parabolico - Docx LisssssAli Ala Sufa TerrenoAún no hay calificaciones

- TP #1 PDFDocumento5 páginasTP #1 PDFLautaro Elías VieraAún no hay calificaciones

- Reseña Histora AgatoDocumento5 páginasReseña Histora AgatoAndre OrdoñezAún no hay calificaciones

- Ejerciciosresueltos 02 PDFDocumento3 páginasEjerciciosresueltos 02 PDFJuanAún no hay calificaciones

- Progra Gasoducto PDFDocumento20 páginasProgra Gasoducto PDFPaola TorricoAún no hay calificaciones

- MEPU Elementos Del RatingDocumento2 páginasMEPU Elementos Del RatingAdemia LolAún no hay calificaciones

- Titulo IIDocumento560 páginasTitulo IILuisazcaballero0% (1)

- Normas Apa Sobre Material Estadístico y MatemáticoDocumento8 páginasNormas Apa Sobre Material Estadístico y Matemáticomar817Aún no hay calificaciones

- CDS Obolus CDocumento2 páginasCDS Obolus Cmarco.valdez1989Aún no hay calificaciones

- DGM8500 SpanishDocumento4 páginasDGM8500 SpanishLuis Francisco Gómez MottaAún no hay calificaciones

- Analisis Semiotica Spot PublicitarioDocumento9 páginasAnalisis Semiotica Spot PublicitarioEmily A. CastilloAún no hay calificaciones

- Estructuración Del PsiquismoDocumento6 páginasEstructuración Del PsiquismoAgustin ZehnderAún no hay calificaciones

- TallerDocumento2 páginasTallerJEYSSER SEBASTIAN ROJAS CARRILLOAún no hay calificaciones