Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Tema 5 - Biestables

Tema 5 - Biestables

Cargado por

teiloccDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Tema 5 - Biestables

Tema 5 - Biestables

Cargado por

teiloccCopyright:

Formatos disponibles

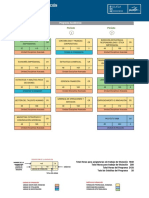

Tema 5 BIESTABLES

5.1. CIRCUITOS SECUENCIALES

Al igual que el Algebra de Boole era el modelo matem atico de la l ogica combinacional, la Teor a de Aut omatas (de n umero de estados nito) es el modelo matem atico de la l ogica secuencial. En l ogica combinacional se representan todas aquellas funciones en las que, para conocer el valor de la salida en un determinado instante, s olo hace falta conocer los valores de las entradas en ese instante, es decir, el circuito no tiene memoria y, por consiguiente, no es necesario denir su estado interno para poder predecir el valor de la salida una vez que se conoce la funci on y los valores de las entradas. Existen, no obstante, una serie de problemas que no pueden analizarse ni resolverse utilizando s olo l ogica combinacional. El ejemplo m as sencillo de sistema cuya descripci on es imposible sin denir estados internos es el que simula el comportamiento de un bol grafo. Podemos admitir que es un sistema que posee una entrada con dos valores (pulsar o no pulsar), y que responde sacando o metiendo la punta. Sin embargo, esta respuesta depende del estado anterior (punta dentro o punta fuera). Si pulsamos estando la punta dentro, esta sale. En cambio si estaba fuera, entra. Decimos entonces que el bol grafo es un aut omata de 2 estados. Como ya hemos mencionado en el primer tema, existen 2 formas equivalentes de denir o representar un aut omata: la representaci on Moore y la representaci on Mealy (gura 5.1). Como tambi en hemos dicho, F1 y F2 son funciones combinacionales, que ya sabemos manejar utilizando el Algebra de Boole y los m etodos de minimizaci on descritos en temas anteriores. En este tema, estudiaremos una de las formas de implementar el bloque : a trav es de biestables o ip-ops. Los biestables son los dispositivos secuenciales m as sencillos, ya que s olo disponen de dos estados internos distintos. Se les puede considerar memorias de 1 bit, puesto que son celdas capaces de almacenar un bit de informaci on (un estado interno corresponder a al 0 l ogico y el otro al 1 l ogico), y de mantenerlo en tanto no se produzcan unas condiciones determinadas en sus entradas. En este tema estudiaremos los distintos tipos de 77

78

TEMA 5. BIESTABLES

F1

F1

S !

S !

F2

F2

(a)

(b)

Figura 5.1: Denici on de un aut omata Mealy (a) y Moore (b).

Figura 5.2: Flip-op RS b asico con puertas NOR. ip-ops existentes y analizaremos las distintas condiciones de disparo de cada uno de ellos (activaci on del ip-op o generaci on de un nuevo estado interno y salida en funci on de sus entradas). Asimismo, veremos algunas de las aplicaciones m as importantes de los biestables.

5.2.

FLIP-FLOP RS

Un ip-op, en su estructura m as simple, se puede construir con dos puertas NOR realimentadas, tal y como se ilustra en la gura 5.2. Cada uno de los circuitos mostrados conforma un ip-op b asico a partir del cual se construyen formas m as sosticadas de biestables. La conexi on cruzada de la salida de cada puerta a la entrada de la otra constituye el lazo de realimentaci on imprescindible en todo dispositivo de memoria. Cada una de estas celdas b asicas cuenta con dos salidas (Q y Q), y con dos entradas: set (S ) y reset (R). Este tipo de biestable se conoce con el nombre de ip-op RS.

5.2. FLIP-FLOP RS

79

5.2.1.

Funcionamiento del ip-op RS.

Las dos entradas de un biestable RS van a realizar las siguientes acciones (opuestas) cuando son activadas: - R (reset): poner la salida a cero (Q = 0, Q = 1) - S (set): poner la salida a uno (Q = 1, Q = 0) Si ninguna de las entradas est a activa, el ip-op mantendr a las salidas en el valor an el previo. En el caso en que ambas entradas se activen simult aneamente Q y Q tomar mismo valor, con lo que esta conguraci on normalmente no se utilizar a.

5.2.2.

Flip-op RS construido a partir de puertas NOR.

En este caso las dos entradas R y S son activas a nivel alto (a 1), ya que, como se puede deducir r apidamente de la tabla de verdad de la puerta NOR, siempre que una de las entradas sea 1, la salida ser a siempre 0 (independientemente del valor de la segunda entrada). Esta caracter stica es la que nos va a ayudar a analizar los circuitos con puertas NOR realimentadas.

A 0 0 1 1

B 0 1 0 1

NOR 1 0 0 0

Se pueden dar los siguientes cuatro casos: a) Si se activa el reset (R = 1, S = 0) la salida ser a siempre cero (Q = 0). La otra puerta NOR tendr a entonces dos ceros como entradas, con lo que Q ser a uno.

b) Si se activa el set mientras el reset est a desactivada (S = 1, R = 0) entonces Q siempre ser a cero (0). La otra puerta NOR tendr a, por lo tanto, dos ceros como entradas con lo que su salida (Q) ser a uno.

80

TEMA 5. BIESTABLES

c) Si ambos, reset y set se activan (R = 1, S = 1) se har a (Q = 0, Q = 0). Esta conguraci on normalmente no se utilizar a, ya que, por norma general, nos interesar a que Q y Q sean siempre opuestas una a la otra. Es importante recalcar que el hecho de que las salidas se llamen Q y Q no signica que una es la negada de la otra (y este caso, en donde activamos reset y set a la vez, es una buena prueba de ello).

d) Supongamos que ninguna de ambas entradas sean activas (R = 0, S = 0). En esta situaci on el valor de las salidas de las puertas NOR no est a determinada por estas entradas, an posibles dos conguraciones, sino por el valor de los lazos de realimentaci on (Q y Q ). Ser que depender an del valor previo de los lazos de realimentaci on y, por tanto, de todas las entradas anteriores. Como se puede ver, en ambos casos se mantendr a invariable la conguraci on inmediatamente anterior. a) d)

b) d)

5.2. FLIP-FLOP RS

81

Figura 5.3: Ejemplo de funcionamiento de un ip-op RS (NOR). Por lo tanto, las tablas de transiciones de estado para un ip-op RS (NOR) son: R 0 0 0 0 1 1 1 1 S 0 0 1 1 0 0 1 1 Qn 0 1 0 1 0 1 0 1 Qn+1 0 1 1 1 0 0 No usado No usado

R 0 0 1 1

S 0 1 0 1

Qn+1 Qn 1 0 No usado

Por tanto, cuando las entradas R y S est an inactivas el ip-op mantiene la conguraci on alcanzada en la operaci on previa, es decir, el estado siguiente (Qn+1 ) ser a igual al n estado actual (Q ). De esta forma se guarda el bit de informaci on previamente almacenado (1 si se ha actuado sobre el set o 0 si se ha actuado sobre el reset).

5.2.3.

Flip-op RS (NOR) sincronizado por nivel.

El ip-op b asico, tal como se ha descrito hasta aqu , es un circuito secuencial as ncrono. En cualquier sistema digital que incluya un cierto n umero de puertas y elementos de este tipo pr acticamente va a ser imposible garantizar que las se nales R y S se presenten, exactamente, en los instantes de tiempo requeridos para realizar las operaciones l ogicas, con lo que podemos perder f acilmente el control sobre el circuito. Esta dicultad puede soslayarse permitiendo cambios de estado en el ip-op s olo cuando lo indique un reloj externo que, usualmente, ser a com un para todo el sistema secuencial. De este modo, las se nales de salida se sincronizar an con el reloj, no dependiendo las transiciones del momento de llegada de las se nales R y S , mejorando por tanto la coordinaci on. El ip-op RS sincronizado por nivel (gura 5.4) consta de una celda RS b asica con puertas NOR, a la que se a naden dos puertas AND adicionales en la entrada. La se nal de reloj que realiza la sincronizaci on es introducida en cada puerta AND, en tanto que las se nales R y S constituyen las otras entradas. De esta manera, las entradas a las puertas

82

TEMA 5. BIESTABLES

Figura 5.4: Flip-op RS (NOR) sincronizado a nivel.

CLK

Figura 5.5: Ejemplo de funcionamiento de un ip-op RS (NOR) s ncrono. NOR (Ry S ) s olo ser an activas cuando el reloj est e en alta, con lo que las entradas R y S seguir an determinando el estado nal del ip-op, pero en transiciones que u nicamente podr an ocurrir cuando el reloj las permita. Este dispositivo es tambi en conocido como latch RS. Por tanto, la se nal de reloj (CLK ) que hemos introducimos genera el siguiente comportamiento del biestable (ver gura 5.5): - Cuando el reloj est a inactivo (CLK = 0), el ip-op mantiene su estado, independientemente de los valores de las se nales R y S . - Cuando el reloj est a activo (CLK = 1) entonces R= R y S = S (gura 5.4), con lo cual el ip-op tendr a un funcionamiento similar a un RS as ncrono. La tabla de transiciones de estado de un ip-op RS s ncrono es:

CLK 0 1 1 1 1

R x 0 0 1 1

S x 0 1 0 1

Qn+1 Qn Qn 1 0 No usado

5.2. FLIP-FLOP RS

83

Figura 5.6: Flip-op RS (NOR) sincronizado a nivel y con entradas P r y Cl as ncronas.

5.2.4.

Flip-op RS (NOR) sincronizado a nivel con entradas as ncronas de Preset y Clear.

En toda la descripci on previa de los ip-ops RS sincronizados hemos partido de un cierto estado inicial de ip-op a partir del cual se realizan las transiciones sincronizadas por la se nal de reloj. En la pr actica, es frecuentemente deseable disponer de los medios de resetear (Q = 0) o presetear (Q= 1) el ip-op, independientemente de sus entradas R, S o del reloj. Esto se consigue modicando el circuito del latch en la forma ilustrada en la gura 5.6. Las se nales de Preset (P r) y Clear (Cl) act uan de manera prioritaria e independiente de las otras l neas de entrada: si se activa P r, Q pasar a a 1, independientemente del resto de las se nales; y si se activa Cl, Q pasar a a 0. El comportamiento del biestable completo se puede ver en las siguientes tablas de transiciones de estado: Pr 0 1 1 0 0 0 0 0 Cl 1 0 1 0 0 0 0 0 CLK x x x 0 1 1 1 1 R x x x x 0 0 1 1 S x x x x 0 1 0 1 Qn+1 0 1 No permitido Qn Qn 1 0 No usado

Pr 0 0 1 1

Cl 0 1 0 1

Qn+1 Qn 0 1 No permitido

Resumiendo: P r y S ponen a 1. Cl y R ponen a 0. S y R sincronizadas (s olo tienen efecto cuando el reloj est a activo). P r y Cl as ncronas (tienen efecto siempre). En caso de contradicci on tienen prioridad P r y Cl.

84

TEMA 5. BIESTABLES

Figura 5.7: Flip-op JK sincronizado a nivel.

5.3.

OTROS FLIP-FLOPS SINCRONIZADOS POR NIVEL

Flip-op JK.

5.3.1.

En el ip-op RS vimos que exist a un estado ambiguo como consecuencia de aplicar simult aneamente dos niveles activos a las l neas R y S . La ambig uedad surge como consecuencia de resultar Q = Q a la salida, y por no conocer con certeza el estado del ip-op resultante si ambas entradas se hacen inactivas simult aneamente. El ip-op JK es un renamiento del RS en el que el estado indeterminado queda, en este caso, perfectamente denido. Las entradas J y K se comportan como las entradas S y R, respectivamente; sin embargo, cuando se activan simult aneamente, el ip-op conmuta al estado complementario del que se encuentra. En la gura 5.7 se muestra el esquema l ogico de un ip-op sincronizado a nivel. Como se aprecia existe un lazo de realimentaci on de las salidas hacia la puerta AND de entrada, para evitar la inestabilidad del RS. Cuando las entradas J y K aparecen simult anemanete activas, la salida que en ese momento se encuentre a 1 hace que la salida de la puerta AND correspondiente se ponga a 1 (la otra permanecer a en 0), lo que hace bascular el ip-op en cualquier caso. Hay que hacer notar que esta conexi on de realimentaci on del ip-op JK a la que hac amos referencia hace que, si la se nal de reloj permanece a 1 (siempre que J = K = 1), se producir an transiciones de forma continua e incontrolada, con el resultado nal de que no podemos predecir en que estado se va a quedar el ip-op al deshabilitar el reloj. Para evitar este proceso indeseable, se deben dise nar ip-ops m as complejos que, en vez de activarse con un nivel alto del reloj, se activen o disparen en las transiciones del reloj, lo que se denomina ancos. La ventaja de estos nuevos ip-ops radica en que es mucho m as f acil y able controlar la transici on de una se nal (de 0 a 1, o viceversa) que la duraci on de un pulso (con la precisi on de decenas de nanosegundos necesaria). El comportamiento de un ip-op JK s ncrono se puede resumir en la siguiente tabla:

5.3. OTROS FLIP-FLOPS SINCRONIZADOS POR NIVEL

85

Figura 5.8: Flip-op tipo JK sincronizado a nivel con entradas J = 0 y K = 1. CLK 0 1 1 1 1 J x 0 0 1 1 K x 0 1 0 1 Qn+1 Qn Qn 0 1 n Q

J K

pone a 1 pone a 0

En la gura 5.7 puede observarse que cuando el reloj es cero se verica que R= S = 0, con lo que el ip-op mantiene el estado previamente almacenado, es decir, Qn+1 = Qn . Veamos algunas transiciones debidas a la activaci on de J y K cuando el reloj est a en un nivel activo (CLK = 1). Obviamente, cuando J y K est an desactivadas, es decir son cero, el biestable mantiene el estado actual, lo mismo que ocurr a con el ip-op RS. i) Supongamos el ip-op en Q = 1 y queremos ponerlo a 0. Para ello necesitamos activar (poner a 1) la entrada K . El comportamiento del biestable se puede observar en la gura 5.8. ii) Supongamos el ip-op en Q = 0 y queremos ponerlo a 1. Para ello necesitamos activar (poner a 1) la entrada J (gura 5.9). iii) En la gura 5.10 vemos que pasa cuando J y K est an activas simult aneamente (es decir, J = K = 1). Suponemos que inicialmente el biestable tiene almacenado el estado Q = 1. En este u ltimo caso, se puede observar que el ip-op conmuta de estado continuamente, pasando alternativamente por las dos condiciones de salida estables (enmarcadas en un rect angulo en la gura). Este fen omeno se debe a la realimentaci on de las salidas del biestable a las puertas AND de entrada, que es precisamente lo que nos permite conmutar

86

TEMA 5. BIESTABLES

Figura 5.9: Flip-op tipo JK sincronizado a nivel con entradas J = 1 y K = 0. de estado. El problema es que al conmutar de estado, dejamos de activar Ry pasamos a activar S , con lo que volvemos a conmutar de estado, y as sucesivamente. Las tablas de transiciones del ip-op JK (completa y continuaci on. J K Qn Qn+1 0 0 0 0 J K 0 0 1 1 0 0 0 0 1 0 0 1 0 0 1 1 1 0 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 0 reducida) se pueden ver a

Qn+1 Qn 0 1 n Q

A partir de la u ltima podemos obtener la ecuaci on de transici on para el ip-op JK que nos da el estado siguiente (Qn+1 ) en funci on de J , K y el estado actual (Qn ):

Q J KQ

n n+1

00

01 1

11

10

0 1 1

1

n

Qn+1 = JQ + KQn

5.3. OTROS FLIP-FLOPS SINCRONIZADOS POR NIVEL

87

Figura 5.10: Flip-op tipo JK sincronizado a nivel con entradas J = 1 y K = 1.

88

TEMA 5. BIESTABLES

Figura 5.11: Flip-op tipo T sincronizado a nivel.

5.3.2.

Flip-op T.

El ip-op tipo T es una versi on simplicada del ip-op JK. Tal y como se observa en la gura 5.11, se obtiene directamente del JK conectando juntas las entradas J y K . La designaci on T para este ip-op es consecuencia de la caracter stica de cambio de estado de este ip-op (toggle ). Cuando T = 1, entonces J = K = 1 y el ip-op cambiar a de estado (cambiar a de estado indenidas veces mientras que el reloj sea 1).Cuando T = 0, entonces J = K = 0 y el ip-op permanece en el estado en el que se encontraba. CLK 0 1 1 T x 0 1 Qn+1 Qn Qn n Q T 0 0 1 1 Qn 0 1 0 1 Qn+1 0 1 1 0

La ecuaci on del estado siguiente (Qn+1 ) de un ip-op T en funci on de sus entradas n actuales (T y Q ) es:

Q T Q

n n+1

1 1

0 1 1

n

Qn+1 = T Q + T Qn

5.3.3.

Flip-op D.

El ip-op tipo D (gura 5.12) es una modicaci on del ip-op RS sincronizado por nivel. La entrada D se aplica directamente a la entrada S , y su complemento a la entrada

5.4. FLIPFLOPS SINCRONIZADOS O DISPARADOS A FLANCOS

89

Figura 5.12: Flip-op D sincronizado a nivel. R. El nombre de ip-op D viene como consecuencia de su capacidad de transferir datos desde la l nea de entrada a la salida, siempre que los pulsos de reloj lo permitan. Cuando D es 0, se activa R y el ip-op pasa a Q = 0; mientras que, cuando D es 1, se activa S y el ip-op pasa a Q = 1. En ambos casos, la entrada se transmite a la salida. Es decir, CLK 0 1 1 D x 0 1 Qn+1 Qn 0 1

5.4.

FLIPFLOPS SINCRONIZADOS O DISPARADOS A FLANCOS

La posible modicaci on del estado de un ip-op se debe a alg un cambio en las se nales de entrada. Diremos que ese cambio ha disparado (trigger ) el ip-op. En ip-ops as ncronos, es decir, en aquellos que no admiten una se nal de reloj, se requiere simplemente un cambio de nivel en las se nales de entrada para producir el disparo del ip-op. En ip-ops disparados por niveles, s olo es posible un cambio de estado en sincronismo con uno de los niveles de la se nal del reloj (t picamente el nivel 1). En un ip-op disparado por ancos, el cambio de estado s olo se permite en las transiciones de la se nal de reloj, o bien cuando la se nal pasa del nivel 0 al nivel 1 (ip-op disparado en ancos positivos), o bien cuando la se nal de reloj pasa de 1 a 0 (ip op disparado en ancos negativos). Hay varias formas de construir ip-ops disparados por ancos. Nosotros s olo veremos una de ellas: los ip-ops master-slave.

5.4.1.

Flip-op master-slave.

Un ip-op master-slave se construye mediante dos ip-ops en cascada: un circuito sirve como maestro (master ) y el otro como esclavo (slave ). El esquema de un biestable RS de este tipo se muestra en la gura 5.13 y consta, como puede apreciarse, de dos

90

TEMA 5. BIESTABLES

Figura 5.13: Flip-op RS master-slave.

CLK 1 CLK 2 S = S1 R = R1 Q1 = S 2 Q1 = R 2 Q = Q2

Figura 5.14: Ejemplo de funcionamiento de un ip-op RS master-slave. ip-ops y un inversor. Cuando el reloj se halla en alta, el ip-op master se encuentra habilitado, con lo que la salida del mismo ser a funci on de las entradas R y S , mientras que el ip-op slave se encuentra inhibido, con lo cual mantiene el estado. Cuando el reloj pasa a baja, la situaci on es la inversa, de forma que el ip-op master se encuentra aislado del exterior (con lo que mantiene su estado), mientras que el ip-op slave responde a las se nales procedentes del master. De esta forma el ip-op master responde en el nivel alto de la se nal de reloj y el ip-op slave responde en los niveles bajos. El circuito completo responder a justo en el intervalo de transici on del nivel alto al nivel bajo de la se nal de reloj. Ser a, por tanto, un ip-op sincronizado con los ancos negativos de la se nal de reloj. Con este montaje se consigue tambi en desacoplar las entradas del circuito a las salidas, y el efecto es que las salidas no presentar an la inestabilidad inherente a las realimentaciones. La combinaci on master-slave tambi en se puede construir con el ip-op tipo D, sin m as que a nadir un ip-op RS a su salida, tal y como indica la gura 5.15, dando lugar a un ip-op D master-slave. El esquema anterior no es v alido para los ip-op JK y T, puesto que si J = K = 1

5.4. FLIPFLOPS SINCRONIZADOS O DISPARADOS A FLANCOS

91

Figura 5.15: Flip-op D master-slave.

Figura 5.16: Flip-op JK master-slave. o T = 1 y se habilita el reloj (CLK = 1) el ip-op master conmutar a un n umero indeterminado de veces, con lo que no podemos saber cual va a ser su estado nal cuando el reloj se desactive (CLK = 0). En este caso, la construcci on de los ip-ops JK y T master-slave requiere modicar su estructura interna. La modicaci on u nicamente consiste en realizar la realimentaci on no desde las salidas del biestable master, sino desde las salidas del biestable slave, tal y como podemos observar en la gura 5.16 para un JK. Para un ip-op T master-slave s olo habr a que hacer que J y K fuesen siempre iguales a T . Ahora, en un ip-op JK master-slave (disparado a ancos), cuando las entradas J y K son activas simult aneamente (J = K = 1), el ip-op s olo podr a cambiar de estado una vez, a diferencia de lo que vimos anteriormente en el caso de un ip-op disparado a

CLK

J=K=1

Figura 5.17: Funcionamiento de un ip-op JK master-slave con entradas J = K = 1.

92

TEMA 5. BIESTABLES

niveles, que cambia indenidamente de estado mientras el reloj est e activo (CLK = 1).

EJERCICIOS

93

EJERCICIOS

5.1. Las formas de onda de la siguiente gura son aplicadas a un ip-op RS disparado por niveles y con entradas as ncronas de Preset y Clear. Obtener la forma Q resultante suponiendo que inicialmente est a en baja.

CLK S R Cl Pr

5.2.

i) Construir un ip-op JK a partir de un ip-op D. ii) Construir un ip-op JK a partir de un ip-op T. iii) Construir un ip-op JK a partir de un ip-op RS.

También podría gustarte

- Opel Frontera 1999Documento393 páginasOpel Frontera 1999Richard Zerpa50% (4)

- Curso Fotografia EspanolDocumento49 páginasCurso Fotografia Espanolcrd osorno100% (1)

- Practica 05 Edg 1Documento25 páginasPractica 05 Edg 1Patricio OrdoñezAún no hay calificaciones

- Movimiento en El Plano y en El EspacioDocumento31 páginasMovimiento en El Plano y en El EspacioRichard Zerpa0% (1)

- Grupos Emergentes en El PerúDocumento10 páginasGrupos Emergentes en El PerúCarlos LuyoAún no hay calificaciones

- Apunte Logica Secuencial Flip FlopDocumento9 páginasApunte Logica Secuencial Flip FlopTity Cristina VergaraAún no hay calificaciones

- Biestables VSRDocumento54 páginasBiestables VSRDaniel AlvarezAún no hay calificaciones

- Flip FlopDocumento23 páginasFlip FlopRenzoAún no hay calificaciones

- Sistema Lógico Secuencial Asincrónico y SincrónicoDocumento38 páginasSistema Lógico Secuencial Asincrónico y SincrónicoNemessis Pacheco100% (1)

- Invernadero Proy 3.Documento8 páginasInvernadero Proy 3.Omar Alejandro Arroyo ArellanoAún no hay calificaciones

- 10 BiestablesDocumento45 páginas10 BiestablesFERMINAún no hay calificaciones

- Flip FlopDocumento13 páginasFlip FlopFranklin AldanaAún no hay calificaciones

- Reporte Practica Flip FlopsDocumento18 páginasReporte Practica Flip FlopsChamín AlcántaraAún no hay calificaciones

- I Circuitos Secuenciales Básicos 3-09Documento18 páginasI Circuitos Secuenciales Básicos 3-09valeria LopezAún no hay calificaciones

- PROYECTO 5 ReconfigDocumento12 páginasPROYECTO 5 ReconfigAiraAún no hay calificaciones

- Capitulo 4 - Elementos de MemoriaDocumento18 páginasCapitulo 4 - Elementos de MemoriaTurbo59Aún no hay calificaciones

- Flip FlopDocumento13 páginasFlip Flop28792kymmAún no hay calificaciones

- Resumen de Flip FlopsDocumento10 páginasResumen de Flip FlopserickAún no hay calificaciones

- Flip Flops ApunteDocumento14 páginasFlip Flops ApunteIsrael RamosAún no hay calificaciones

- El Flip Flop y Los Circuitos SecuencDocumento26 páginasEl Flip Flop y Los Circuitos Secuencb4tipibeAún no hay calificaciones

- Flip FlopDocumento23 páginasFlip FlopJoseph JesusAún no hay calificaciones

- Flip FlopDocumento6 páginasFlip FlopJulian Andres EcheverryAún no hay calificaciones

- Circuitos Digitales Flip FlopDocumento13 páginasCircuitos Digitales Flip FlopCorimayo MaximilianoAún no hay calificaciones

- Contador Binario de 4 Bits Utilizando Flip - Flop J-KDocumento7 páginasContador Binario de 4 Bits Utilizando Flip - Flop J-KCarlos MichelAún no hay calificaciones

- Flip FlopDocumento14 páginasFlip FlopEduard ContrerasAún no hay calificaciones

- Electronica Digital II Lab. 2Documento9 páginasElectronica Digital II Lab. 2Leonardo VieraAún no hay calificaciones

- Celda BásicaDocumento2 páginasCelda BásicaWendyAún no hay calificaciones

- Flip FlopDocumento12 páginasFlip FlopEmilys QuijadaAún no hay calificaciones

- Practica Flip Flop Sistemas Digitales 1Documento17 páginasPractica Flip Flop Sistemas Digitales 1Carlos FrancoAún no hay calificaciones

- ScridbDocumento13 páginasScridbGeorge SmithAún no hay calificaciones

- Báscula RSDocumento3 páginasBáscula RSCarlos Raul Gomez Frayre100% (1)

- Informe 7 Aulestia PabloDocumento5 páginasInforme 7 Aulestia PabloSHADOWFREE8000Aún no hay calificaciones

- Informe Previo 2Documento13 páginasInforme Previo 2Ronal HbAún no hay calificaciones

- Flip Flop Informe 4 Circuitos Electrónicos IIDocumento13 páginasFlip Flop Informe 4 Circuitos Electrónicos IIDavid IturriagaAún no hay calificaciones

- XOR y Flip Flop PDFDocumento3 páginasXOR y Flip Flop PDFIsis Vivanco VivancoAún no hay calificaciones

- El Flip Flop Maza Vilchez CarlosDocumento8 páginasEl Flip Flop Maza Vilchez CarlosLuis Ramos CuroAún no hay calificaciones

- Labo 1Documento21 páginasLabo 1Jhoselyn Nikol Jimenez AcevedoAún no hay calificaciones

- SISTEMAS DIGITALES Asignacion 9 y 10Documento25 páginasSISTEMAS DIGITALES Asignacion 9 y 10jose2001Aún no hay calificaciones

- Wilson LOGICA DIGITALDocumento10 páginasWilson LOGICA DIGITALANA MERCEDES CONTRERAS DE LA ROSAAún no hay calificaciones

- Los Flip FlopDocumento18 páginasLos Flip FloproxanaAún no hay calificaciones

- Flip FlopsDocumento7 páginasFlip FlopsJuan LainaAún no hay calificaciones

- Flip-Flops SincrónicosDocumento6 páginasFlip-Flops SincrónicosjuanAún no hay calificaciones

- Bies TableDocumento27 páginasBies TablemarialaurarodriguezAún no hay calificaciones

- Digital 8 ADCDocumento6 páginasDigital 8 ADCRodrigo Jose Montaño RodriguezAún no hay calificaciones

- Informe Previo #1aDocumento13 páginasInforme Previo #1aDiego Gutierrez AyalaAún no hay calificaciones

- Universidad Nacional de PiuraDocumento7 páginasUniversidad Nacional de PiurasergioabelramirezzapAún no hay calificaciones

- Bies TableDocumento37 páginasBies TableLuz Karina Lopez SaavedraAún no hay calificaciones

- Circuitos y MicroDocumento26 páginasCircuitos y MicroSlayerMcboAún no hay calificaciones

- Actividad3 P Rez Padr N Edgar AbrahamDocumento10 páginasActividad3 P Rez Padr N Edgar AbrahamMartín Bermúdez BeltránAún no hay calificaciones

- Actividad 13Documento16 páginasActividad 13Stalin Armijos ZambranoAún no hay calificaciones

- FsgsfgsDocumento5 páginasFsgsfgsCarlos javier bellidoAún no hay calificaciones

- Flip-Flops RSDocumento4 páginasFlip-Flops RSDaniel CrespoAún no hay calificaciones

- JK Flip FlopDocumento28 páginasJK Flip FlopangelmauriciormzAún no hay calificaciones

- Trabajo Sistemas Digitales Unidad 3Documento13 páginasTrabajo Sistemas Digitales Unidad 3Oswaldo RosasAún no hay calificaciones

- Flip Flop RsDocumento12 páginasFlip Flop RsRamiro MorenoAún no hay calificaciones

- cd2 Final1Documento8 páginascd2 Final1Eleazar CastilloAún no hay calificaciones

- Caro DigitalesDocumento65 páginasCaro DigitalesJamm MomaAún no hay calificaciones

- Latch NorDocumento3 páginasLatch NorRoberto SolorzanoAún no hay calificaciones

- Capitulo 6Documento5 páginasCapitulo 6Fanny Vanessa Uc PootAún no hay calificaciones

- LCDDocumento38 páginasLCDEddy León RamírezAún no hay calificaciones

- Mecatronica Automotriz 6 Semestre PDFDocumento44 páginasMecatronica Automotriz 6 Semestre PDFRichard Zerpa100% (1)

- Philips Dps-182bp Chassis Lc7.1ala 32pfl5332Documento2 páginasPhilips Dps-182bp Chassis Lc7.1ala 32pfl5332takatalvi100% (1)

- IPS E-Max System - Técnico DentalDocumento18 páginasIPS E-Max System - Técnico DentalRichard Zerpa100% (1)

- Reparacion TV PlasmaDocumento50 páginasReparacion TV PlasmaRichard ZerpaAún no hay calificaciones

- Sem 285 PDFDocumento84 páginasSem 285 PDFRicardo TapiaAún no hay calificaciones

- A09-A10 - Memoria 24LC512 Con Interfaz I2CDocumento48 páginasA09-A10 - Memoria 24LC512 Con Interfaz I2CRichard ZerpaAún no hay calificaciones

- Control de Un Motor Paso A Paso PIC PDFDocumento125 páginasControl de Un Motor Paso A Paso PIC PDFjulio gamboaAún no hay calificaciones

- 05-11-2001Documento26 páginas05-11-2001La GacetaAún no hay calificaciones

- Absorcion y Concentracion de Nitrogeno Fosforo y PDocumento9 páginasAbsorcion y Concentracion de Nitrogeno Fosforo y PDina Marcela Herrera BeltranAún no hay calificaciones

- A Vuelo de Pajaro-Ediciondigital Serindigena PDFDocumento155 páginasA Vuelo de Pajaro-Ediciondigital Serindigena PDFEdgar RamírezAún no hay calificaciones

- Informatización de Cooperativas AgrícolasDocumento78 páginasInformatización de Cooperativas AgrícolasCamilo HerreñoAún no hay calificaciones

- 1 Respiratorios - CardiovascularDocumento30 páginas1 Respiratorios - CardiovascularMagalí M. DuarteAún no hay calificaciones

- Manual AcuarioDocumento12 páginasManual AcuarioNASaccesorios HIDnasxenonAún no hay calificaciones

- Informe Reconocimiento de MaterialDocumento7 páginasInforme Reconocimiento de MaterialMiguel Angel Burbano CastilloAún no hay calificaciones

- Toma de ApuntesDocumento3 páginasToma de ApuntesRubenCalle100% (2)

- Gfpi-F-019 - Guia - de - Aprendizaje - 1 Protección Ambiental y de SSTDocumento4 páginasGfpi-F-019 - Guia - de - Aprendizaje - 1 Protección Ambiental y de SSTMaria Paula Perez RodríguezAún no hay calificaciones

- Literatura Reacimiento Triptico Parte 3Documento2 páginasLiteratura Reacimiento Triptico Parte 3Electronicdeivi Deivi100% (1)

- Act 3 TTE Cuadro ComparativoDocumento3 páginasAct 3 TTE Cuadro ComparativoDan Isai RosalesAún no hay calificaciones

- Parcial - Escenario 4 - Primer Bloque-Teorico - Practico - Gerencia Financiera - (Grupo b19)Documento11 páginasParcial - Escenario 4 - Primer Bloque-Teorico - Practico - Gerencia Financiera - (Grupo b19)alejandragonzalezAún no hay calificaciones

- CAP 25 - Hipopotasemia CECILDocumento4 páginasCAP 25 - Hipopotasemia CECILalejandra haroAún no hay calificaciones

- Tarjetas URCADocumento6 páginasTarjetas URCAandres.jeriadiazAún no hay calificaciones

- Guia para El Desarrollo de Las de Pca-For WebDocumento24 páginasGuia para El Desarrollo de Las de Pca-For WebJacob Delgado OrtizAún no hay calificaciones

- AderezosDocumento11 páginasAderezosAnonymous pEiRlWcs0% (1)

- Manual Bienvenida WBF 2014 ESP PDFDocumento17 páginasManual Bienvenida WBF 2014 ESP PDFrubenAún no hay calificaciones

- Separadores en Medios Densos - EscritoDocumento10 páginasSeparadores en Medios Densos - EscritoKarlita TituanaAún no hay calificaciones

- Taller Inicial PetrografiaDocumento4 páginasTaller Inicial PetrografiaERIKA DANIELA ALFONSO TORRESAún no hay calificaciones

- AccessDocumento34 páginasAccessDIEGO ARMANDO LOPEZ MARCIALAún no hay calificaciones

- Lipovetsky Gilles - La Era Del Vacio y Del MiedoDocumento11 páginasLipovetsky Gilles - La Era Del Vacio y Del MiedoOmar Romero100% (4)

- MBA UDLA MallaDocumento1 páginaMBA UDLA MallaDanes Vinicio Reyes RoseroAún no hay calificaciones

- JhonJairo Rodriguez Entregable 1 - EvaluacionDocumento17 páginasJhonJairo Rodriguez Entregable 1 - EvaluacionJhon Jairo Rodriguez CerónAún no hay calificaciones

- Balance General Alameda SRL 31122020Documento4 páginasBalance General Alameda SRL 31122020Carmen GonzalezAún no hay calificaciones

- Expo Criminalistic ADocumento26 páginasExpo Criminalistic AJosé Carlos Estrada De Los RiosAún no hay calificaciones

- Solución Caso ChancletaDocumento6 páginasSolución Caso ChancletaCarlos GonalezAún no hay calificaciones

- OHSAS - Evaluación de Riesgos Laborales (Lectura) PDFDocumento291 páginasOHSAS - Evaluación de Riesgos Laborales (Lectura) PDFred_rex666Aún no hay calificaciones

- Actividad ElectricidadDocumento9 páginasActividad ElectricidadEvanni Carrera RamirezAún no hay calificaciones