0% encontró este documento útil (0 votos)

1K vistas20 páginasComunicación SPI en Sistemas Embebidos

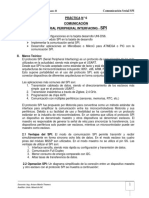

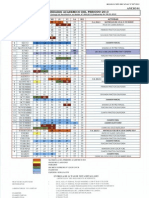

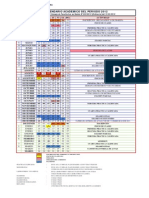

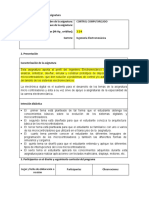

El documento describe la interfaz SPI (Serial Peripheral Interface) utilizada para la comunicación síncrona serial entre microcontroladores y periféricos. Explica que la interfaz SPI permite la transmisión y recepción simultánea de datos de 8 bits entre un dispositivo maestro y uno o más esclavos utilizando las señales de reloj, datos de entrada y salida. También detalla la configuración y uso de los pines asociados a la comunicación SPI en los microcontroladores PIC.

Cargado por

RubensaiDDerechos de autor

© Attribution Non-Commercial (BY-NC)

Nos tomamos en serio los derechos de los contenidos. Si sospechas que se trata de tu contenido, reclámalo aquí.

Formatos disponibles

Descarga como PPTX, PDF, TXT o lee en línea desde Scribd

0% encontró este documento útil (0 votos)

1K vistas20 páginasComunicación SPI en Sistemas Embebidos

El documento describe la interfaz SPI (Serial Peripheral Interface) utilizada para la comunicación síncrona serial entre microcontroladores y periféricos. Explica que la interfaz SPI permite la transmisión y recepción simultánea de datos de 8 bits entre un dispositivo maestro y uno o más esclavos utilizando las señales de reloj, datos de entrada y salida. También detalla la configuración y uso de los pines asociados a la comunicación SPI en los microcontroladores PIC.

Cargado por

RubensaiDDerechos de autor

© Attribution Non-Commercial (BY-NC)

Nos tomamos en serio los derechos de los contenidos. Si sospechas que se trata de tu contenido, reclámalo aquí.

Formatos disponibles

Descarga como PPTX, PDF, TXT o lee en línea desde Scribd