Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Flip Flops

Cargado por

Angie RaigosaDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Flip Flops

Cargado por

Angie RaigosaCopyright:

Formatos disponibles

Sistemas Digitales II.

FLIP-FLOP, LM-555 Y DIAGRAMAS DE ESTADOS

Angelica Patricia Raigosa Figueroa

e-mail: paty_raigosa@hotmail.com

RESUMEN: Basicamente este laboratorio tiene

como objetivo fundamental el conocimiento de cada uno de los tres tipos de flip-flops vistos en clase y un respectiva programacin en los lenguajes de verilog y VHDL. Tambien se aplican conocimientos teoricos en la realizacin del piano digital de la primera parte de la practica con base en la aplicacin de el circuito oscilador LM555 en configuracin de modo astable. PALABRAS CLAVE: CPLD, LM555, y flip-flop tipo: D, JK y T.

3.1 FLIP-FLOP

Este circuito es una combinacin de compuertas lgicas, A diferencia de las caractersticas de las compuertas solas, si se unen de cierta manera, estas pueden almacenar datos que podemos manipular con reglas preestablecidas por el circuito mismo. La figura 1 es la representacin general para un Flip Flop. Figura1. Representacin estndar de un FF

1 INTRODUCCIN

En la prctica de laboratorio numero 3 es necesario tener en cuenta los conocimientos de flip-flops, sus tipos de FF, su tabla de verdad y su diseo esquemtico. Tambien es necesario conocer los estados de inicio de cada FF, sus flancos de accin. Respecto al LM555 es necesario conocer a cabalidad el Datasheet de este integrado para poder realizar pruebas y dems conexionados necesarios para el montaje del circuito.

Tomado http://www.forosdeelectronica.com/tutoriales/flipflops.htm

de:

2 CONCLUSIONES

2.1 CONCLUSIONES GENERALES

Fue necesario estudiar a fondo el funcionamiento del Flip- Flop tipo D. Hay que analizar detenidamente los valores necesarios para obtener los tiempos requeridos en los relojs de esta prctica. La aplicacin de los conceptos aprendidos previamente en clase sobre diagramas de estados fueron fundamentales para interpretar claramente el enunciado de la practica de laboratorio. La ayuda del programa e simulacin BOOLE fue de utilidad pues tiene una gran cantidad de herramientas y opciones para la creacin de diagramas de estado.

Los FF pueden tener varias entradas, dependiendo del tipo de las funciones internas que realice, y tiene dos salidas:

Las salidas de los FF slo pueden tener dos estados (binario) y siempre tienen valores contrarios, como se puede ver en la tabla1 Tabla1.

3 CONCEPTOS BASICOS

Las entradas de un FF obligan a las salidas a conmutar hacia uno u otro estado o hacer "flip flop" (Trmino anglosajn), ms adelante explicaremos cmo interactan las entradas con las salidas para lograr los efectos caractersticos de cada FF.

Sistemas Digitales II.

.

con compuertas (clocked) dispuestas de tal forma que la accin PONER - QUITAR (set - reset) sea llevada a cabo por una sola lnea de entrada. Bsicamente, se puede considerar el JK flip-flop como un circuito biestable con una sola entrada y dos salidas, completamente entre s. En la prctica, el circuito integrado dispone de dos entradas auxiliares, marcadas J y K, dispuestas para "condicionar}" el estado que debe tomar la salida a partir del momento que llegue la prxima transicin activa del pulso clock. La figura 3 muestra el circuito lgico y tabla de verdad para este flip-flop. Se puede observar que, de acuerdo a como se encuentren las entradas J y K, la salida Q puede operar como toggle o quedarse indefinidamente en un determinado estado, sin importar los pulsos en la entrada clock. Cuando se utiliza al flip-flop como contador o divisor, se pueden dejar libres las entradas J y K; en este caso, los pulsos cuya frecuencia se desea modificar, se deben poner en la entrada correspondiente al clock. Figura3.

El FF tambin es conocido como:

"Registro Bsico" trmino utilizado para la forma ms sencilla de un FF. "Multivibrador Biestable" trmino pocas veces utilizado para describir a un FF.

3.1.2 TIPOS DE FLIP-FLOP

EL DATA o D FLIP - FLOP El flip - flop tipo D es una cierta modficacin introducida al flip-flop clocked Rs(controlado en su funcionamiento por los pulsos Clock en una sola lnea comn de entreda). El principio bsico se muestra en la figura 2 FIGURA2

Tomado de: http://www.electronica2000.com/digital/cirlogse.htm Podemos apreciar que, es agregado un inversor a una de las dos entradas del flip-flop, de tal forma que la entrada restante y la entrada del inversor queden unidas. Lo anterior garantiza que las entradas a la seccin RS sean siempre complementarias una de otra, y asegura que el estado lgico en la salida Q sser siempre el mismo estado lgico, alto o bajo, del ltimo pulso que lleg a la entrada D. La informacin dada tiene un carcter general, ya que no se pueden dar conceptos concretos por razn de la amplia variedad de flip-flop que se fabrican en circuito integrado, an dentro de un mismo tipo. Nos servir para dejar cimentados ciertos principios, los cuales nos ayudarn a interpretar luego las diferentes tablas de verdad, dadas por el fabricante para facilitar al experimentador la comprensin del funcionamiento de una u otra referencia. EL JK FLIP FLOP

Tomado de: http://www.electronica2000.com/digital/cirlogse.htm

3.2 LM555

El circuito integrado 555 es de bajo costo y de grandes prestaciones. Inicialmente fue desarrollado por la firma Signetics. En la actualidad es construido por muchos otros fabricantes. Entre sus aplicaciones principales cabe destacar las de multivibrador astable (dos estados metaestables) y monoestable (un estado estable y otro metaestable), detector de impulsos, etctera. Est constituido por una combinacin de comparadores lineales, flip-flops (biestables digitales), transistor de descarga y excitador de salida. Las tensiones de referencia de los comparadores se establecen en 2/3 V para el primer comparador C1 y en 1/3 V para el segundo comparador C2, por medio del divisor de tensin compuesto por 3 resistencias iguales R. En el grfico se muestra el nmero de pin con su correspondiente funcin.

Probablemente es el flip-flop ms usado en los circuitos secuenciales lgicos, por su capacidad para CONTAR y DIVIDIR. Entrega un pulso completo de salida por cada dos pulsos de entrada, caracterstica tenida en cuenta por muchos para denominarlo, tambin, "toggle"(basculante, ondulante, Si - No - Si - No, etc.) flip-flop, o sencillamente un T flip-flop. Bsicamente, el JK flip-flop es un biestable RS flip-flop

Sistemas Digitales II.

. 3.2.1 Descripcin de las terminales del Temporizador 555 GND (normalmente la 1): es el polo negativo de

3.3 DIAGRAMA DE ESTADOS

Los diagramas de estados son una tcnica conocida para describir el comportamiento de un sistema. Describen todos los estados posibles en los que puede entrar un objeto particular y la manera en que cambia el estado del objeto, como resultado de los eventos que llegan a l.

la alimentacin, generalmente tierra. Disparo (normalmente la 2): Es en esta patilla, donde se establece el inicio del tiempo de retardo, si el 555 es configurado como monostable. Este proceso de disparo ocurre cuando este pin va por debajo del nivel de 1/3 del voltaje de alimentacin. Este pulso debe ser de corta duracin, pues si se mantiene bajo por mucho tiempo la salida se quedar en alto hasta que la entrada de disparo pase a alto otra vez. Salida (normalmente la 3): Aqu veremos el resultado de la operacin del temporizador, ya sea que est conectado como monostable, astable u otro. Cuando la salida es alta, el voltaje ser el voltaje de alimentacin (Vcc) menos 1.7 Voltios. Esta salida se puede obligar a estar en casi 0 voltios con la ayuda de la patilla de reset (normalmente la 4). Reset (normalmente la 4): Si se pone a un nivel por debajo de 0.7 Voltios, pone la patilla de salida a nivel bajo. Si por algn motivo esta patilla no se utiliza hay que conectarla a Vcc para evitar que el 555 se "resetee". Control de voltaje (normalmente la 5): Cuando el temporizador se utiliza en el modo de controlador de voltaje, el voltaje en esta patilla puede variar casi desde Vcc (en la prctica como Vcc -1 voltio) hasta casi 0 V (aprox. 2 Voltios). As es posible modificar los tiempos en que la salida est en alto o en bajo independiente del diseo (establecido por las resistencias y condensadores conectados externamente al 555). El voltaje aplicado a la patilla de control de voltaje puede variar entre un 45 y un 90 % de Vcc en la configuracin monostable. Cuando se utiliza la configuracin astable, el voltaje puede variar desde 1.7 voltios hasta Vcc. Modificando el voltaje en esta patilla en la configuracin astable causar la frecuencia original del astable sea modulada en frecuencia (FM). Si esta patilla no se utiliza, se recomienda ponerle un condensador de 0.01F para evitar las interferencias. Umbral (normalmente la 6): Es una entrada a un comparador interno que tiene el 555 y se utiliza para poner la salida a nivel bajo. Descarga (normalmente la 7): Utilizado para descargar con efectividad el condensador externo utilizado por el temporizador para su funcionamiento. V+ (normalmente la 8): Tambin llamado Vcc, alimentacin, es el pin donde se conecta el voltaje de alimentacin que va de 4.5 voltios hasta 18 voltios (mximo). Hay versiones militares de este integrado que llegan hasta 18 Voltios.

4. DISEO 4.1 MAQUINA PARA APLICAR PEGANTE

Primero analizamos el enunciado, y se empieza a crear la tabla de estados que se puede ver en la figura 4, luego de tener la tabla de estados, se procede a realizar el diagrama de estamos para las dos entradas y las tres salidas; las dos entradas son el pulsador de inicio y el swicth para cuando hay una unidad defectuosa en la maquina( este diagrama se encuentra en la figura 5. Figura4. Tabla de estados. Tomado de: Autor Figura 5. Diagrama de estados.

Fuente: Autor. Por medio de un simulador corremos el diagrama de estados y cumple con los parmetros pedidos para la activacin de los leds. De la tabla se saca variable por variable y por medio de mapas de karnaught se encuentra la funcin para cada una de las salidas ( como se puede observar en la figura 6, 7,8,9,10 y 11). Luego de tener las funciones halladas por medio de los mapas. Se procede a conectar estas funciones a flipflops tipo D como se pide en el enunciado( se puede ver en la figura 12)

Sistemas Digitales II.

.

Figura 6. Mapa de karnaught Figura 10. Mapa de karnaught

Figura 7. Mapa de karnaught

Figura 11. Mapa de karnaught

Figura 8. Mapa de karnaught

Figura 12. Esquematico funciones conectadas al tipo D.

Figura 9. Mapa de karnaught

Luego de tener el esquematico para los flip-flops tipo D, procedemos a conectar los tiempos al los circuito monoestable y al Astable. (todo junto queda conectado de tal manera como se ve en la figura 13)

Sistemas Digitales II.

.

Figura 13. Circuito completo Simulado.

En este circuito se implemento el display para revisar en que estado se encuentra el ciclo, este display es tipo anodo comn por ende es surtido por un 74s47.

4 BIBLIOGRAFIA O REFERENCIAS

[1] G. Obregn-Pulido, B. Castillo-Toledo and A. Loukianov, A globally convergent estimator for n frequencies, IEEE Trans. On Aut. Control. Vol. 47. No 5. pp 857-863. May 2002. [2] H. Khalil, Nonlinear Systems, 2nd. ed., Prentice Hall, NJ, pp. 50-56, 1996. [3] Ronald J. Tocci, Neal S. Widmer, Sistemas Digitales Principios y Aplicaciones, Sexta ed. PRENTICE HALL HISPANO AMERICANO, S.A, Mxico 1996. [4] Thomas L. Floyd, Fundamentos de Sistemas Digitales, Sptima ed. PEARSON EDUCACION, S.A, Madrid 2000.

También podría gustarte

- Control 7 ErgonomiaDocumento5 páginasControl 7 Ergonomiacamila100% (1)

- Caldera Peisa Manual 23 Ds FDocumento24 páginasCaldera Peisa Manual 23 Ds Fkadikito60% (5)

- Medición y Conversión de UnidadesDocumento5 páginasMedición y Conversión de Unidadesgregoriofernandez100% (1)

- Mate2B2 ExamenDocumento9 páginasMate2B2 ExamenBerenice Acosta CotaAún no hay calificaciones

- 26 - El Ladron de TiempoDocumento196 páginas26 - El Ladron de TiempoKristell Bonilla Ramírez100% (1)

- Diseño de Secciones TDocumento18 páginasDiseño de Secciones TTamir Portal HuamanAún no hay calificaciones

- Frank Sosa Informe02 Ley de Charles 2ADocumento3 páginasFrank Sosa Informe02 Ley de Charles 2AVíctor AguilarAún no hay calificaciones

- Práctica No4 DENSIDAD Y PESO ESPECIFICO (Documento13 páginasPráctica No4 DENSIDAD Y PESO ESPECIFICO (Yessica Quisbert Gutierrez100% (1)

- Informe 1 Lodos Nativos y Desificados2Documento57 páginasInforme 1 Lodos Nativos y Desificados2irmaAún no hay calificaciones

- Introduccion Teoria ColasDocumento190 páginasIntroduccion Teoria ColasFrank CornejoAún no hay calificaciones

- Practicas de Electronica Malvino (Libre)Documento376 páginasPracticas de Electronica Malvino (Libre)John Jairo Silva95% (19)

- Calculo Seccion Cables Vehiculos Mejor Excelente OkDocumento34 páginasCalculo Seccion Cables Vehiculos Mejor Excelente OkJohn Freddy Franco Yela100% (1)

- Ejercicios para Trabajar Las Propiedades de La MultiplicaciónDocumento5 páginasEjercicios para Trabajar Las Propiedades de La MultiplicaciónYuliana GomezAún no hay calificaciones

- Iso 87Documento4 páginasIso 87Maria Guadalupe Acevedo CruzAún no hay calificaciones

- PQ200v187 Manual EspanolDocumento142 páginasPQ200v187 Manual EspanolAbel Rivera CervantesAún no hay calificaciones

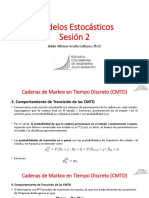

- Modelos Estocásticos Sesión 2Documento22 páginasModelos Estocásticos Sesión 2Juancho CorreaAún no hay calificaciones

- Práctica 02 - CBR In-SituDocumento13 páginasPráctica 02 - CBR In-SitumrnicusAún no hay calificaciones

- Dossier 1Documento62 páginasDossier 1winghost ghostAún no hay calificaciones

- Lab.2 - Rect. Media OndaDocumento2 páginasLab.2 - Rect. Media OndaBratt ArangoAún no hay calificaciones

- Circuito TanqueDocumento3 páginasCircuito TanqueKeviin ArronaAún no hay calificaciones

- Reporte de Investigacion - Transformacion LinealDocumento7 páginasReporte de Investigacion - Transformacion LinealDanna JaegerAún no hay calificaciones

- Informe Ambiental - Calidad de Aire - Flesan Chincha - Noviembre - v01Documento129 páginasInforme Ambiental - Calidad de Aire - Flesan Chincha - Noviembre - v01anderson inquil guzmanAún no hay calificaciones

- Terminología BásicaDocumento6 páginasTerminología BásicaLuisArroyoAún no hay calificaciones

- Grado 7 - La Ciencia de Los SuperhéroesDocumento25 páginasGrado 7 - La Ciencia de Los SuperhéroesJero GallegoAún no hay calificaciones

- Historia Del Billar de BuchacasDocumento44 páginasHistoria Del Billar de BuchacasJose FloAún no hay calificaciones

- Telefono BellDocumento2 páginasTelefono BellKevin Diaz CabreraAún no hay calificaciones

- Elemento de Diseño AnomaliaDocumento14 páginasElemento de Diseño AnomaliaRobertinio HchAún no hay calificaciones

- CS201 - Análisis VectorialDocumento6 páginasCS201 - Análisis VectorialnaruatAún no hay calificaciones