Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Guia Practica 1 2024 MARCELO AZPILCUETA RUBINA

Guia Practica 1 2024 MARCELO AZPILCUETA RUBINA

Cargado por

Marcelo Azpilcueta RubinaDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Guia Practica 1 2024 MARCELO AZPILCUETA RUBINA

Guia Practica 1 2024 MARCELO AZPILCUETA RUBINA

Cargado por

Marcelo Azpilcueta RubinaCopyright:

Formatos disponibles

UNIVERSIDAD PARTICULAR CATÓLICA DE SANTA MARÍA DE AREQUIPA

ESCUELA PROFESIONAL DE INGENIERÍA MECATRONICA

CÓDIGO: 4M202104 GUÍA DE LABORATORIO NRO

ASIGNATURA: SISTEMAS DIGITALES 01

PRIMERA FASE: LOGICA COMBINACIONAL

Docente(s):

Ing. Sergio Mestas Ramos.

PARÁMETROS DE LAS PUERTAS LOGICAS

Fecha: 2024.03.15.

I. OBJETIVO:

• Analizar las características electrónicas de las compuertas lógicas TTL y CMOS

II. MARCO TEORICO:

FAMILIA TTL (LÓGICA DE TRANSISTOR - TRANSISTOR)

- Esta fue la primera familia de éxito comercial, se utilizó entre 1965 y 1985. Los circuitos TTL

utilizan transistores bipolares y algunas resistencias de polarización. La tensión nominal de

alimentación de los circuitos TTL son 5 V DC.

o Niveles Lógicos TTL

o En el estudio de los circuitos lógicos, existen cuatro especificaciones lógicos

diferentes: VIL, VIH, VOL y VOH.

- En los circuitos TTL, VIL es la tensión de entrada válida para el rango 0 a 0.8 V que

representa un nivel lógico 0 (BAJO). El rango de tensión VIH representa la tensiones válidas

de un 1 lógico entre 2 y 5 V. El rango de valores 0.8 a 2 V determina un funcionamiento no

predecible, por lo tanto estos valores no son permitidos. El rango de tensiones de salida

VOL, VOH se muestra en la figura 1.

o

Fig.1 Rango de Tensiones de Entrada y Salida

- Configuraciones de Salida en las Compuertas TTL

Las compuertas TTL tienes tres tipos de configuraciones de salida:

Salida de Colector Abierto.

Salida de Poste Totémico.

Salida de Tres Estados.

Compuerta con Salida de Colector Abierto

La compuerta básica TTL fue una modificación DTL. La figura de la compuerta citada

se muestra en la figura 2.

Laboratorio de Circuitos Digitales - EPIMMEYM Quinto Semestre UCSM 2023

Fig. 2 Compuerta NAND TTL de colector abierto

- La resistencia externa RL debe conectarse para que la salida hale hacia el nivel alto,

cuando el transistor Q3 está en corte.

- Si cualquiera de los niveles lógicos de entrada es cero, la juntura base-emisor en Q1 se

polariza directamente. Por consiguiente, la tensión en la base Q1 es igual a:

- 0.2 V(Tensión de entrada) + 0.7(VbeQ1) = VbQ1 = 0.9 V

- El transistor Q3 comienza a conducir cuando la suma de las caídas de tensión de VbcQ1,

VbeQ2 y VbeQ3 sean superiores a 1.8 V. Como la tensión en VbQ1 es 0.9.V, el transistor

Q3 queda en estado de corte. Por lo tanto, sí se conecta una resistencia al colector, la

tensión de salida será un 1 lógico.

- Si todos los niveles lógicos de entrada son 1, los transistores Q2 y Q3 se saturan debido

a que la tensión en la base de Q1 es superior a la suma de las caídas de tensión VbcQ1,

VbeQ2 y VbeQ3. Entonces el estado de salida es igual a cero lógico (0).

Compuerta con Salida de Tipo Totémico (Totem Pole)

- Las compuertas se caracterizan por tener una impedancia de salida determinada. Esta

impedancia se compone de una resistencia más una capacitancia. La capacitancia se

carga exponencialmente de bajo a alto según la constante de tiempo RC, cuando el

transistor de salida pasa de bajo a alto. La diferencia entre una compuerta de colector

abierto y una de tipo totémico radica en el transistor Q4 y el diodo D1.

Fig. 3 Compuerta TTL de salida tipo totémico

Ing. Sergio Mestas R. Arequipa 2023

Laboratorio de Circuitos Digitales - EPIMMEYM Quinto Semestre UCSM 2023

- La salida es baja cuando Q2 y Q3 se encuentran en saturación como en la compuerta

de colector abierto. La ecuación siguiente expresa el valor de la tensión en el colector

de Q2:

- 0.7(VbeQ3) + 0.2 V(VceQ2) = VcQ2 = 0.9 V

- Como F = VceQ3 = 0.2 V, el transistor Q4 está en corte por:

- 0.6 V(VbeQ4) + 0.6 V(VD1) < 0.11 V(VcQ2 ó VbQ4)

- Ya que VcQ2 = VbQ4 . Por lo tanto Q4 está en corte. El diodo se coloca para provocar

una caída en el lazo y asegurar el corte de Q4 con Q3 saturado.

- En una transición de estado lógico 1 en la salida por causa de cambio en la entrada a 0,

los transistores Q2 y Q3 se cortan. En este caso, la salida se mantiene un instante de

tiempo baja debido a que el voltaje en el condensador no puede cambiar

instantáneamente.

En el momento que Q2 entra en corte, Q4 conduce por el voltaje conectado a su base

a través de la resistencia de 1.6 KW. El transistor Q4 se satura momentáneamente por

la corriente exigida por el condensador, incrementándose el voltaje de acuerdo a una

constante de tiempo RC. El proceso anterior es rápido por la baja resistencia equivalente

entre 130 KW, la resistencia de saturación del transistor y la resistencia del diodo. Por

consiguiente, la transición de un valor lógico bajo a uno alto es más rápida. En la medida

de acumulación de carga a la salida, el voltaje de salida la corriente por el transistor Q4

disminuye, por lo que éste pasa a la región activa. Entonces, el voltaje de salida es: F

= 5 - 0.6 V(VbeQ4) - 0.6 V(VD1) = 3.6 V

FAMILIA CMOS.

- Cuando se emplean dispositivos CMOS y TTL, juntos, es usual que el voltaje de

alimentación sea de 5 V para que una sola fuente de alimentación de 5 V proporcione

VDD para los dispositivos CMOS y VCC para los TTL. Si los dispositivos CMOS funcionan

con un voltaje superior a 5V para trabajar junto con TTL se deben de tomar medidas

especiales.

- VOLTAJE DE ALIMENTACIÓN: Las series 4000 y 74C funcionan con valores de VDD,

que van de 3 a 15 V, por lo que la regulación del voltaje no es un aspecto crítico. Las

series 74HC y 74RCT funcionan con un menor margen de 2 a 6 V.

- Cuando las salidas CMOS manejan sólo entradas CMOS, los niveles de voltaje de la

salida pueden estar muy cercanos a 0V para el estado bajo, y a VDD para el estado alto.

Esto es el resultado directo de la alta resistencia de entrada de los dispositivos CMOS,

que extrae muy poca corriente de la salida a la que está conectada.

VOL (max) 0v

VOH (min) VDD

VIL (max) 30% VDD

VIH (min) 70% VDD

- Los requerimientos de voltaje en la entrada para dos estados lógicos se expresa como

un porcentaje del voltaje de alimentación, tal y como se expresa en la tabla adjunta.

o De esta forma, cuando un CMOS funciona con VDD = 5 V, acepta voltaje de entrada

menor que VIL(máx) = 1.5 V como BAJO, y cualquier voltaje de entrada mayor que

VIH (mín) = 3.5 V como ALTO.

- NIVELES DE VOLTAJE.

Ing. Sergio Mestas R. Arequipa 2023

Laboratorio de Circuitos Digitales - EPIMMEYM Quinto Semestre UCSM 2023

- Se denomina ruido a "cualquier perturbación involuntaria que puede originar un cambio

no deseado en la salida del circuito." El ruido puede generarse externamente por la

presencia de escobillas en motores o interruptores, por acoplo por conexiones o líneas

de tensión cercanas o por picos de la corriente de alimentación. Los circuitos lógicos

deben tener cierta inmunidad al ruido la cual es definida como "la capacidad para tolerar

fluctuaciones en la tensión no deseadas en sus entradas sin que cambie el estado de

salida". Los fabricantes establecen un margen de seguridad para no sobrepasar los

valores críticos de tensión conocido como MARGEN DE RUIDO.

- En la Figura 4, tenemos los valores críticos de las tensiones de entrada y salida de una

puerta lógica y los márgenes de ruido a nivel alto y bajo.

Fig.4 Valores Críticos de E/S

III. INFORME PREVIO:

a) Cuáles son las principales características eléctricas (alimentación, entrada y salida) de un

circuito integrado y una puerta lógica.

b) Explicar las diferencias tipos de familias TTL: LS, HC, L y C

c) Explique las diferencias entre las tecnologías TTL y CMOS.

d) Mención un integrado en tecnología CMOS para las puertas lógicas AND, OR, NOT, NAND y

NOR.

e) Como medimos corriente en la entrada o salida de una puerta lógica.

IV. MATERIALES Y EQUIPOS

Fuentes de Alimentación.

Osciloscopio.

Multímetro.

Protoboard, cables de conexión.

01 Potenciómetros de 50Kohm

08 Leds

04 Resistencias de 1K.

04 Resistencias de 330.

02 Resistencias de 10k.

02 Dip switch de 4 posiciones.

CI. TTL: 74LS00, 74LS02, 74LS04, 74LS08, 74LS32, 74LS14. CI CMOS: 4001,4011

V. PROCEDIMIENTO

Ing. Sergio Mestas R. Arequipa 2023

Laboratorio de Circuitos Digitales - EPIMMEYM Quinto Semestre UCSM 2023

Preparando el circuito integrado

1. Coloque correctamente el circuito integrado sobre el protoboard.

2. Verifique que el circuito este correctamente alimentado.

3. Con un multímetro mide el voltaje en las patillas correspondientes.

4. En el caso del integrado que se muestra a continuación Vcc (patilla 14) y GND (patilla 7).

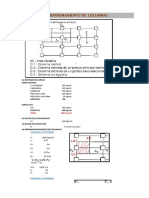

Medición de Umbral de Voltaje de Entrada

5. Implementar los circuitos de la figura 1 y siga los pasos indicados:

6. Conecte el multímetro en función voltímetro a la entrada como a la salida de la puerta

lógica.

Ing. Sergio Mestas R. Arequipa 2023

Laboratorio de Circuitos Digitales - EPIMMEYM Quinto Semestre UCSM 2023

7. Subir la tensión en la entrada desde 0V, y cuando el LED cambie de estado, anotar en la

casilla (¿VIHmin o VILmax?).

8. Ahora bajar la tensión en la entrada desde 5V, y cuando el LED cambie de estado, anotar

en la casilla (¿VIHmin o VILmax?).

9. Busque estos valores en el Datasheet del C.I. en el manual o en Internet, y complete la

tabla.

C. Integrado:

Valores Medido Teórico

VILmax 1 0.8

VIHmin 1.615 2

VOLmax 0.627 0.5

VOHmin 2 2.7

10. Repita los pasos para los otros circuitos integrados (1 de la familia TTL y 1 de la familia

CMOS) y anote en tablas distintas.

Medición de IIL, IIH, VOH, VOL, IOH y IOL.

11. Arme el circuito la figura 2.

Ing. Sergio Mestas R. Arequipa 2023

Laboratorio de Circuitos Digitales - EPIMMEYM Quinto Semestre UCSM 2023

12. Conecte un circuito de una o dos entradas y mantenga el punto [C] en la parte superior y

mida y anote en una tabla los valores respectivos.

13. Cambie el punto [C] a la parte inferior y mida y anote en una tabla los valores respectivos.

14. Repita los pasos anteriores para otro circuito integrado

Tiempo de Propagación.

15. Armar el siguiente circuito de la figura 3

Ing. Sergio Mestas R. Arequipa 2023

Laboratorio de Circuitos Digitales - EPIMMEYM Quinto Semestre UCSM 2023

16. Conecte como entrada el generador de funciones.

17. A la entradas y salida conecte un osciloscopio.

18. Comparar con el osciloscopio las dos señales y calcular el tiempo de propagación, buscar

en el Datasheet ese valor anotar en la tabla para cada compuerta utilizada:

Medido Teórico

Tp 0.00A 13.1mA

Ing. Sergio Mestas R. Arequipa 2023

Laboratorio de Circuitos Digitales - EPIMMEYM Quinto Semestre UCSM 2023

VI. CUESTIONARIO FINAL:

1. Fundamentar como se forman los materiales para compuertas lógicas TTL y CMOS

• Compuertas TTL: Las compuertas TTL usan transistores del tipo bipolar por lo que están

dentro de las familias lógicas bipolares. Dentro de la familia TTL, encontramos varias

series: TTL de baja potencia (serie 74L00), con menor consumo de energía, ideal para

aplicaciones en las cuales las disipaciones de potencia es más critica que la velocidad;

TTL de alta velocidad (serie 74H00), con velocidad de conmutación mucho más rápida

con un retardo promedio de propagación de 6ns, pero la velocidad aumentada se logra

a expensas de una disipación mayor de potencia; TTL Schotty (serie 74S00), la cual

tiene la mayor velocidad dentro de la familia TTL. Compuertas CMOS: En su nombre lo

dice, es un semiconductor complementario de óxido metálico, utilizados para

aplicaciones de conmutación, tienen una alta velocidad y bajo consumo de electricidad,

algunas diferencias con la familia TTL, son que los TTL necesitan voltajes de

alimentación de 5 V, mientras que los CMOS de 3 a 15 V, para los TTL se utilizan

transistores bipolares, mientras que los CMOS utilizan transistores MOSFET, y por

último los CMOS tienen menor consumo de energía y menor velocidad que las

compuertas de la familia TTL.

2. 2) ¿Por qué no coinciden los valores medidos y el datasheet?

• Los valores no coinciden debido a errores que se presentan en la práctica, errores como

un error en el instrumento de medición, en este caso el multímetro, además que los

valores del datasheet son valores referenciales.

3) Cuáles son las características que determinan la máxima condición de operación, máxima

velocidad y menor consumo de una familia de compuertas de CI

• Una de las características más importantes es que maneja la información en binario,

es decir, valores de “1” y “0”, estas combinaciones pueden darnos otras características,

como las estáticas: tensiones de entrada y salida, corrientes de entrada y salida, FANIN

y FANOUT, márgenes de ruido y la potencia disipada; y características dinámicas:

retardo de propagación y los tiempos de subida y bajada.

Ing. Sergio Mestas R. Arequipa 2023

Laboratorio de Circuitos Digitales - EPIMMEYM Quinto Semestre UCSM 2023

4) Que se entiende por corriente de source y corriente de sink.

• Source y sink son términos que se utilizan para definir el control de flujo de corriente

directa en una carga, source proporciona el voltaje necesario para el circuito o carga,

mientras que sink proporciona la conexión a tierra necesaria para el circuito o para la

carga.

• En este circuito se muestra una salida digital tipo sinking, la carga se conecta a tierra.

En este circuito se muestra una salida digital tipo sourcing, la carga se eleva para recibir

voltaje.

5) Indicar en que aplicaciones prácticas en donde se usan las compuertas TTL y CMOS

• Aplicaciones compuerta TTL: Se utilizan en microprocesadores, como el 8X300, de

Signetics, la familia 2900 de AMD y otros; en memorias RAM; en memorias PROM; y

en Programmable Array Logic (PAL), consistente en una PROM que interconecta las

entradas y cierto número de puertas lógicas.

• Aplicaciones compuerta CMOS: Se utilizan en numerosas área de electrónica, además

de sus aplicaciones en microprocesadores y almacenamiento, se utilizan también para

relojes digitales, en el campo de la electrónica de navegación, en cámaras digitales y

espectrómetros; su alta tecnología, alta resistencia, larga vida útil y bajos requisitos

energéticos hacen que las compuertas CMOS sean indispensables en dispositivos

modernos.

Ing. Sergio Mestas R. Arequipa 2023

Laboratorio de Circuitos Digitales - EPIMMEYM Quinto Semestre UCSM 2023

VII. CONCLUSIONES Y OBSERVACIONES

Emita al menos cinco sus conclusiones y observaciones de la experiencia

• Los parámetros más importantes de las puertas lógicas son la entrada, la salida y la

función lógica que realizan. Las entradas y salidas pueden ser de diferentes tipos, como

alto o bajo voltaje, 1 o 0 lógico, verdadero o falso, etc.

• Otra característica importante de las puertas lógicas es su tiempo de retardo, que es

el tiempo que tarda la salida en cambiar después de que la entrada cambia. Este

parámetro es crítico para el diseño de circuitos digitales de alta velocidad.

• Las puertas lógicas también tienen un nivel de ruido máximo, que es la cantidad de

ruido que pueden soportar en las entradas antes de que se produzcan errores en la

salida. Este parámetro es importante para garantizar que los circuitos digitales sean

robustos y confiables.

• El consumo de energía es otro parámetro importante de las puertas lógicas,

especialmente en los dispositivos móviles y las baterías. Las puertas lógicas de baja

potencia consumen menos energía y son ideales para aplicaciones que requieren un

bajo consumo de energía.

• Las compuertas lógicas son los dispositivos electrónicos más sencillos que existen, pero

al mismo tiempo son los más utilizados en la actualidad.

VIII. BIBLIOGRAFIA:

Digital Guide Ionos. (08 de Diciembre de 2021). ¿Qué es CMOS? Obtenido de https://

www.ionos.mx/digitalguide/servidores/know-

how/cmos/#:~:text=La%20tecnolog%C3%ADa%

20CMOS%20se%20utiliza,de%20la%20electr%C3%B3nica%20de%20navegaci%C3%B3n.

Nieto, I. (23 de Enero de 2015). Aplicaciones del Circuito TTL. Obtenido de https://

es.slideshare.net/ivanieto/aplicaciones-del-circuito-ttl

Salas, R. (25 de Septiembre de 2021). Cursos Electrónica Industrial y PLC. Obtenido de

https:// cursosindustriales.blogspot.com/2021/09/reglas-de-diseno-parte-3-conceptos-

de.html

Universidad Politécnica de Madrid. (s.f.). CIRCUITOS DIGITALES INTEGRADOS

COMERCIALES. Obtenido de

https://www.cartagena99.com/recursos/alumnos/apuntes/TC%202019_20%20Tema

%203.pdf

Ing. Sergio Mestas R. Arequipa 2023

También podría gustarte

- Practica #3 Control Motores Simulación Cade SIMUDocumento26 páginasPractica #3 Control Motores Simulación Cade SIMUBrandon Romero Alfaro100% (9)

- Chura Mollo Rafael.Documento17 páginasChura Mollo Rafael.Jean Carlos Chura MolloAún no hay calificaciones

- Reglamento Interno de TránsitoDocumento41 páginasReglamento Interno de TránsitoGheghel Gutierrez Huaman91% (11)

- 1º Prueba PlacasDocumento5 páginas1º Prueba PlacasBenjamin Zuñiga AlvaradoAún no hay calificaciones

- TesisDocumento103 páginasTesisLewis Raul Poma RojasAún no hay calificaciones

- El Ci 555 Temporizador y Gen FrecuenciaDocumento12 páginasEl Ci 555 Temporizador y Gen Frecuenciaenriquevazquez27Aún no hay calificaciones

- PirometalurgiaDocumento15 páginasPirometalurgiaalexander beltranAún no hay calificaciones

- Circuito Integrado 555Documento5 páginasCircuito Integrado 555Ruben Patricio AvilaAún no hay calificaciones

- 1.2 Circuitos de DisparoDocumento12 páginas1.2 Circuitos de DisparoEdgar IsmaelAún no hay calificaciones

- Manual 555Documento27 páginasManual 555Raúl Rocha100% (2)

- Geología y GeotecniaDocumento282 páginasGeología y GeotecniaMIGUEL GONZALEZAún no hay calificaciones

- Guia Practica 1 2024Documento8 páginasGuia Practica 1 2024Marcelo Azpilcueta RubinaAún no hay calificaciones

- Informe Digitales 1 PabloDocumento20 páginasInforme Digitales 1 Pabloanthony RomeroAún no hay calificaciones

- Guia Practica 1Documento9 páginasGuia Practica 1Eduardo Jesús Sucno HerenciaAún no hay calificaciones

- Guia Práctica 1Documento7 páginasGuia Práctica 1Esteban MontesAún no hay calificaciones

- Informe 1 SistemasDocumento13 páginasInforme 1 SistemasSALIM MONTIELAún no hay calificaciones

- LAB01CDDocumento11 páginasLAB01CDJose OlazabalAún no hay calificaciones

- Guias CeiiDocumento6 páginasGuias CeiiAlejandro Valdivia OrtegaAún no hay calificaciones

- Informe 1 Circuitos DigitalesDocumento18 páginasInforme 1 Circuitos DigitalesJose Carlos Fabian Mamani VilcapazaAún no hay calificaciones

- Familias TTL y CmosDocumento14 páginasFamilias TTL y CmosDiana OlivaresAún no hay calificaciones

- Familas TTL y CmosDocumento20 páginasFamilas TTL y CmosXavi Mak100% (1)

- Miguel ValecillosDocumento13 páginasMiguel Valecillosjahv_2000Aún no hay calificaciones

- MULTIVIBRADORES, El CD4541 y El CD4047 - V-2012-1 - PDFDocumento14 páginasMULTIVIBRADORES, El CD4541 y El CD4047 - V-2012-1 - PDFtutesamAún no hay calificaciones

- Tecnología TTLDocumento6 páginasTecnología TTLMarioAún no hay calificaciones

- INFORME PREVIO N2 UtrillaDocumento12 páginasINFORME PREVIO N2 UtrillaKaren Peña ReyesAún no hay calificaciones

- Resumen Familias LogicasDocumento14 páginasResumen Familias LogicasRichard MarinAún no hay calificaciones

- Practica Temporizador 555Documento15 páginasPractica Temporizador 555Jesús BañosAún no hay calificaciones

- Trabajo Circuitos DigitalesDocumento16 páginasTrabajo Circuitos DigitalesjaimeAún no hay calificaciones

- Familia DTLDocumento3 páginasFamilia DTLHenry LazoAún no hay calificaciones

- Borrador Caracteristicas de Las Familias LogicasDocumento13 páginasBorrador Caracteristicas de Las Familias LogicasSilvana GetialAún no hay calificaciones

- Familia Lógica de Circuitos IntegradosDocumento47 páginasFamilia Lógica de Circuitos IntegradosKaren Johanna Ramos PazAún no hay calificaciones

- Informe Previo de Astables y MonoestablesDocumento29 páginasInforme Previo de Astables y MonoestablesmiltonAún no hay calificaciones

- Familia Lógica TTLDocumento5 páginasFamilia Lógica TTLJosé Luis eAún no hay calificaciones

- Tema 10 - Familias Logicas TTLDocumento9 páginasTema 10 - Familias Logicas TTLRaul LopezAún no hay calificaciones

- Sesion 02 - Familias LogicasDocumento36 páginasSesion 02 - Familias LogicasWilliam Yoel CcalloAún no hay calificaciones

- Circuitos Digitales Familia Lógica TTLDocumento7 páginasCircuitos Digitales Familia Lógica TTLalvaro charrisAún no hay calificaciones

- Tecnicas DigitalesDocumento25 páginasTecnicas DigitalesHector VallejosAún no hay calificaciones

- Multivibrador Astable y MonoestableDocumento4 páginasMultivibrador Astable y MonoestableVANESSA JAZMIN MORA MARTINEZAún no hay calificaciones

- Compuertas Logicas Laboratorio 1Documento9 páginasCompuertas Logicas Laboratorio 1Cristian GomezAún no hay calificaciones

- Codificacion de Circuitos TTL CmosDocumento4 páginasCodificacion de Circuitos TTL CmosBrisa Aldana MartinezAún no hay calificaciones

- RDS310 S1Documento9 páginasRDS310 S1Herlan CamposAún no hay calificaciones

- Timer Electronico RegulableDocumento4 páginasTimer Electronico RegulableEmanuel MepAún no hay calificaciones

- Familia TTL y CmosDocumento8 páginasFamilia TTL y CmosCristian Calcina TurpoAún no hay calificaciones

- Laboratorio 1-PrevioDocumento15 páginasLaboratorio 1-Previoleslie1906Aún no hay calificaciones

- Laboratorio DigitalesDocumento15 páginasLaboratorio DigitalesPalmer DionicioAún no hay calificaciones

- Semaforo Con Moc y TriacDocumento13 páginasSemaforo Con Moc y TriacSantiago Villacres0% (1)

- Capacidad de Carga de La Familia TTL - Presentacion - Digital - Grupo - 3Documento16 páginasCapacidad de Carga de La Familia TTL - Presentacion - Digital - Grupo - 3rxaviervaAún no hay calificaciones

- Resumen Grupo6Documento42 páginasResumen Grupo6Santiago BuitragoAún no hay calificaciones

- T1 MPJDocumento6 páginasT1 MPJUlises PeñuelasAún no hay calificaciones

- Lab Oratorio TimerDocumento11 páginasLab Oratorio TimerPiero Fiorentini SanchezAún no hay calificaciones

- Circuitos de DisparoDocumento17 páginasCircuitos de DisparoYrbyng Pb100% (1)

- 8-Compuerta Real ShortDocumento4 páginas8-Compuerta Real ShortMiguel Esteban MartinezAún no hay calificaciones

- Labo 1 Previo de DigitalesDocumento15 páginasLabo 1 Previo de Digitalesabel isaac huaytalla cotrinaAún no hay calificaciones

- Lab Diseño 1Documento7 páginasLab Diseño 1Juls FloresAún no hay calificaciones

- Informe Previo 4 Circuitos DigitalesDocumento13 páginasInforme Previo 4 Circuitos DigitalesMiguel Ivan DiazAún no hay calificaciones

- Multivibrador Astable Con Un 555Documento7 páginasMultivibrador Astable Con Un 555Meza Puchoc JeanAún no hay calificaciones

- CVF Electronica PotenciaDocumento8 páginasCVF Electronica PotenciaJesúsAún no hay calificaciones

- (LTC) Práctica 06Documento15 páginas(LTC) Práctica 06Alejandro A. MárquezAún no hay calificaciones

- DigitalesDocumento14 páginasDigitalesChristian LímacoAún no hay calificaciones

- Preinforme 5Documento7 páginasPreinforme 5Francisco PefaurAún no hay calificaciones

- Informe Final Nº1Documento25 páginasInforme Final Nº1greg1505Aún no hay calificaciones

- AplicacionesDocumento14 páginasAplicacionesEfrain RdzAún no hay calificaciones

- Sol Lab 1Documento22 páginasSol Lab 1Michael PomaAún no hay calificaciones

- R LB 3Documento12 páginasR LB 3OnlyJim Rojas PajarAún no hay calificaciones

- Guia Practica 5 2024Documento6 páginasGuia Practica 5 2024Marcelo Azpilcueta RubinaAún no hay calificaciones

- 4 Simplificacion de Funciones 2024Documento24 páginas4 Simplificacion de Funciones 2024Marcelo Azpilcueta RubinaAún no hay calificaciones

- Informe Previo 3 Marcelo Azpilcueta RubinaDocumento4 páginasInforme Previo 3 Marcelo Azpilcueta RubinaMarcelo Azpilcueta RubinaAún no hay calificaciones

- 1 Sistemas Digitales 2024Documento60 páginas1 Sistemas Digitales 2024Marcelo Azpilcueta RubinaAún no hay calificaciones

- FLaboratorios de Circuitos Eléctricos N1Documento14 páginasFLaboratorios de Circuitos Eléctricos N1Marcelo Azpilcueta RubinaAún no hay calificaciones

- Cuestionario PrevioDocumento3 páginasCuestionario PrevioMarcelo Azpilcueta RubinaAún no hay calificaciones

- FDocumento12 páginasFMarcelo Azpilcueta RubinaAún no hay calificaciones

- Prueba de Entrada Mecánica de Fluidos 2024-1Documento2 páginasPrueba de Entrada Mecánica de Fluidos 2024-1Marcelo Azpilcueta RubinaAún no hay calificaciones

- PipiDocumento4 páginasPipiMarcelo Azpilcueta RubinaAún no hay calificaciones

- AvrqerewqreqreqqereqeDocumento3 páginasAvrqerewqreqreqqereqeMarcelo Azpilcueta RubinaAún no hay calificaciones

- AfafdadDocumento2 páginasAfafdadMarcelo Azpilcueta RubinaAún no hay calificaciones

- Hoja Excel CasaDocumento31 páginasHoja Excel CasaWalon Orosco QuispeAún no hay calificaciones

- Fracturador - Yurimaguas PDFDocumento14 páginasFracturador - Yurimaguas PDFmantenimiento PalmaceiteAún no hay calificaciones

- Comparacion de Sistemas OperativosDocumento1 páginaComparacion de Sistemas OperativosJfilms GtAún no hay calificaciones

- Memoria Descriptiva GeneralDocumento28 páginasMemoria Descriptiva General73792588Aún no hay calificaciones

- Os 2069782 Motor Blower 2hpDocumento4 páginasOs 2069782 Motor Blower 2hpwillyAún no hay calificaciones

- Reactor de Tanque AgitadoDocumento3 páginasReactor de Tanque AgitadoRaquelAún no hay calificaciones

- E.T. Reservorio 70M3Documento41 páginasE.T. Reservorio 70M3DianetItmaAún no hay calificaciones

- Bombas Centrifugas - Capacitacion Mantenimiento CV3171 Petroperu TalaraDocumento73 páginasBombas Centrifugas - Capacitacion Mantenimiento CV3171 Petroperu TalaraAlberto Ismael100% (1)

- Terraje DescripcionDocumento1 páginaTerraje DescripcionJessi Jenny PezuaAún no hay calificaciones

- Animacion LucesDocumento9 páginasAnimacion LucesEl Vnico X SiempreAún no hay calificaciones

- Guia de Practica N°8 Nodos PDFDocumento4 páginasGuia de Practica N°8 Nodos PDFMARCO ANTONIO GALARZA TAPIAAún no hay calificaciones

- Ptocnx 3344737Documento5 páginasPtocnx 3344737Raúl Renato Gutarra CamposAún no hay calificaciones

- Clase 2 Terminaciones y EncuentrosDocumento34 páginasClase 2 Terminaciones y EncuentrosGerald Sepulveda SilvanniAún no hay calificaciones

- Presupuesto Cartagena Estabilización-ApusDocumento32 páginasPresupuesto Cartagena Estabilización-ApusMICHAEL ALVARADO CAMPOSAún no hay calificaciones

- CAP 4. EnzimasDocumento52 páginasCAP 4. EnzimasCarlos Paul TitoAún no hay calificaciones

- Informe Proctor Modificado y Cono y Arena. PavimentosDocumento26 páginasInforme Proctor Modificado y Cono y Arena. PavimentosFELIPE PINILLA CABRERAAún no hay calificaciones

- Uñas GelDocumento4 páginasUñas Gelmarycarmona80Aún no hay calificaciones

- Actividad 1Documento4 páginasActividad 1Antonio Ayala Ramos0% (1)

- CORREASDocumento5 páginasCORREASFloyd MenaAún no hay calificaciones

- Mega ConstruccionesDocumento5 páginasMega ConstruccionesKevin JoseAún no hay calificaciones

- Especificaciones TecnicasDocumento145 páginasEspecificaciones TecnicasJOEMAR30Aún no hay calificaciones

- Requisitos para ManliftDocumento1 páginaRequisitos para ManliftBrankAún no hay calificaciones

- Pets-Chi-05-16 R&i Caja Reductora (Pto) y Grupo de Bombas - Perforadora Pit Viper Modelo 351Documento14 páginasPets-Chi-05-16 R&i Caja Reductora (Pto) y Grupo de Bombas - Perforadora Pit Viper Modelo 351karla rivera brañezAún no hay calificaciones

- Plan de Mejoramiento Grado 10 QuimicaDocumento6 páginasPlan de Mejoramiento Grado 10 QuimicaRicaurte De Soacha E UAún no hay calificaciones