Documentos de Académico

Documentos de Profesional

Documentos de Cultura

CD PR11 Decodificadores

Cargado por

Ayrin LinogeTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

CD PR11 Decodificadores

Cargado por

Ayrin LinogeCopyright:

Formatos disponibles

Circuitos Digitales Práctica 11.

Decodificadores

PRÁCTICA 11. DECODIFICADORES

Objetivo: el alumno diseñará e implementará en un FPGA de la tarjeta BASYS o BASYS2

de Digilent, un circuito decodificador de 2 a 4 utilizando la arquitectura flujo de datos de

VHDL y lo integrará con el circuito decodificador de BCD a 7 segmentos.

Material y equipo utilizado:

1 Computadora Personal

1 Tarjeta BASYS, o BASYS 2

1 Cable USB para tarjeta BASYS

Introducción

En la práctica 9 el alumno diseñó un decodificador de BCD a 7 segmentos para manejar

los visualizadores de la tarjeta BASYS. En esta práctica se diseñará un decodificador de

2 a 4, con el propósito de habilitar cada uno de los visualizadores de manera

independiente. Además, utilizará el componente decodificador de BCD a 7 segmentos

para mostrar en los visualizadores un número decimal correspondiente al código binario

que tenga en la entrada.

Como se mencionó en la práctica 9, los cuatro visualizadores comparten los mismos

segmentos, pero cada visualizador se habilita de manera independiente con las señales

que están conectadas a los ánodos de cada visualizador, AN0, AN1, AN2 y AN3, ver figura

11.1 Los transistores PNP funcionan como interruptores controlados. Cuando hay un

nivel bajo en la resistencia, se polariza el transistor y se une el emisor con el colector

cerrando el circuito para que el voltaje de 3.3V energice a los visualizadores.

Figura 11. 1 Sección del diagrama de BASYS 2.

Un decodificador tiene n entradas que representan un código binario y 2n salidas, cada

salida representa un número decimal. Por ejemplo, si en la entrada se tiene el código 102

Maribel Gómez Franco S2-2016 1

Circuitos Digitales Práctica 11. Decodificadores

entonces se activa la salida 2. Un decodificador se utiliza principalmente en situaciones

donde se requiere seleccionar o habilitar de manera individual diferentes dispositivos,

como en el caso de los visualizadores, donde se tienen cuatro de ellos pero que es

necesario habilitarlos de manera independiente para que puedan mostrar diferentes

números decimales en cada uno de ellos.

En esta práctica, el alumno diseñará un decodificador de 2 a 4, y posteriormente,

agregará el decodificador de BCD a 7 segmentos diseñado en la práctica 9, para manejar

los visualizadores de la tarjeta BASYS.

Procedimiento

Primera parte. Simulación del decodificador de 2 a 4 en Multisim.

1. En este punto, verificará el funcionamiento de un decodificador de 2 a 4 en el

simulador.

2. El decodificador de 2 a 4 que utilizará es el circuito integrado 74LS139N, este circuito

incluye dos decodificadores. Este componente tiene dos señales de entrada, una señal

de habilitación activa en nivel bajo, y cuatro salidas activas en nivel bajo. En la

sección de resultados y conclusiones dibuje el símbolo lógico de este decodificador.

3. En el Multisim, construya el circuito mostrado en la figura 11.2 para verificar el

funcionamiento del decodificador 74LS139N. Salve el archivo agregando tres iniciales.

3.1. Es recomendable utilizar los dip-switch y paquetes de resistencias para que su

circuito quede más ordenado.

VCC

5.0V VCC

5.0V

S11

U1

~1G VCC

1A ~2G

1B 2A

1Y0 2B

1Y1 2Y0

1Y2 2Y1

1Y3 2Y2

GND 2Y3

74LS139N

R7

1kΩ R1

330Ω Y3 Y2 Y1 Y0

Figura 11. 2 Circuito de prueba del decodificador de 2 a 4.

Maribel Gómez Franco S2-2016 2

Circuitos Digitales Práctica 11. Decodificadores

4. Elabore la tabla de verdad o de funcionamiento del decodificador 2 a 4 74LS139N,

registre esta información en la sección de resultados y conclusiones. En el Multisim

puede obtener la información de operación del circuito en el modelo del componente:

4.1. Seleccione el decodificador 74LS139N y presione dos veces el botón izquierdo del

ratón o presione una vez el botón derecho del ratón para que aparezca y/o

seleccione el menú de propiedades.

4.2. En la pestaña Value seleccione la opción Edit model.

4.3. En la ventada Edit Model se muestra la tabla de funcionamiento del circuito.

4.4. Cierre las ventanas.

Segunda parte. Diseño del decodificador de 2 a 4 utilizando VHDL

1. Descripción del problema.

Diseñe un decodificador de 2 a 4. Considere el nivel lógico que se requiere para habilitar

las líneas AN0-AN3 de los visualizadores de la tarjeta BASYS. El tipo de arquitectura que

se utilizará en este diseño es por flujo de datos utilizando la declaración when-else.

Utilice como salida los LEDs para verificar su funcionamiento.

2. Diseño en VHDL

2.1. Diseño de la entidad. En la sección de resultados y conclusiones, escriba el código

que define la entidad del decodificador de 2 a 4.

2.2. Defina un nuevo proyecto. Al nombre del archivo agregue sus iniciales o número de

matrícula, por ejemplo Practica11_XXX o decodificadores_XXX.

2.2.1.1. Agregue un archivo fuente, Project>New Source, seleccione VHDL

Module. Escriba la información solicitada por el programa de acuerdo a la

entidad que acaba de definir.

2.3. En la declaración de la arquitectura, después del begin utilice la declaración when-

else del VHDL para describir el funcionamiento del decodificador. En la sección de

resultados y conclusiones, escriba el código que define la arquitectura del

decodificador de 2 a 4.

2.4. Sintetice su diseño, Synthesize-XST.

3. Simulación

3.1. Genere el archivo de prueba, Project>New Source seleccione VHDL test bench.

Utilice el mismo código que ha utilizado para generar las señales de entrada en

las prácticas anteriores, pero en esta sección sólo requiere dos entradas.

3.2. Simule su diseño y verifique que funcione correctamente.

3.3. Salve el archivo del diagrama de tiempos.

4. Asignación de terminales

4.1. Genere y edite el archivo tipo ucf, para asignar las terminales del FPGA a los

puertos. Project> NewSource> Implement Constraints.

Maribel Gómez Franco S2-2016 3

Circuitos Digitales Práctica 11. Decodificadores

4.2. En el panel de diseño, seleccione el archivo fuente y en el panel de procesos

seleccione “Implement Design” o “Implement Top Module”, en este punto

ISE hace el mapeo y la asignación de terminales.

5. Generación del archivo de programación del FPGA

5.1. En el panel de procesos presione el botón derecho del ratón sobre “Generate

Programming File” elija propiedades y en la ventana que aparece seleccione

“Startup Options”. Asegúrese de seleccionar en FPGA Start-Up Clock la opción

JTAG Clock (por omisión es CCLK).

5.2. En el panel de procesos seleccione “Generate Programming File”, para crear el

archivo .bit, el cual se descargará al FPGA de la tarjeta Basys de Digilent. Este

archivo se almacena en la carpeta del proyecto.

6. Configuración y programación de la tarjeta Basys de Digilent

6.1. Conecte la tarjeta Basys de Digilent a cualquier puerto USB disponible de su

computadora. Ejecute el programa Digilent Adept.

6.2. Agregue el archivo tipo bit creado por ISE, el cual se localiza en la carpeta del

proyecto, seleccione Program para descargar el código tipo bit hacia el FPGA.

7. Verificación

Configure los interruptores de la tarjeta BASYS para comprobar el funcionamiento del

circuito. En la tabla 11.2 de la sección de resultados y conclusiones registre esta

información.

Tercera parte. Simulación del decodificador de 2 a 4 y del decodificador de

BCD a 7 segmentos en Multisim.

1. En el Multisim utilizará el decodificador 7447N para activar los segmentos de cuatro

visualizadores conectados en paralelo y utilizará el decodificador 74LS139N para

controlar cuatro transistores que habilitarán de forma independiente los cuatro

visualizadores, ver figura 10.3. Este circuito es similar a la implementación que

realizará en la tarjeta BASYS.

2. En la sección de resultados y conclusiones dibuje el diagrama de conexiones de los

dos decodificadores, los cuatros visualizadores y los cuatro transistores.

3. En el Multisim, construya el diseño de su circuito. Salve el archivo agregando tres

iniciales, en la hoja de trabajo anote los nombres de los integrantes del equipo.

4. Elabore la tabla de verdad o de funcionamiento de su diseño, registre esta información

en la sección de resultados y conclusiones.

4.1. Seleccione el decodificador 7447N y presione dos veces el botón izquierdo del

ratón o presione una vez el botón derecho del ratón para que aparezca y/o

seleccione el menú de propiedades.

4.2. En la pestaña Value seleccione la opción Edit model.

4.3. En la ventada Edit Model se muestra la tabla de funcionamiento del circuito.

4.4. Cierre las ventanas.

Maribel Gómez Franco S2-2016 4

Circuitos Digitales Práctica 11. Decodificadores

VCC

VCC

5.0V

5.0V

U1

VCC ~1G R4 Q1

VCC ~2G 1A

2A 1B 2N3906

5.0V 2B 1Y0

2Y0 1Y1

2Y1 1Y2 Q2

2Y2 1Y3

2Y3 GND 2N3906

74LS139N Q3

S12 10kΩ

2N3906

Q4

2N3906

U3 U4 U5 U6

CA CA CA CA

R1 R2

1kΩ 1kΩ

AB CDE FGH A B CD E FGH A B CD E FGH A B CD E FGH

R3

VCC

U2

5.0V

7 13

1 A OA 12

2 B OB 11

6 C OC 10

S10 D OD 9

3 OE 15

5 ~LT OF 14

4 ~RBI OG

~BI/RBO

7447N

150Ω

VCC

R11

1kΩ 5.0V

S11

R7

1kΩ

Figura 11. 3 Circuito de integración de los decodificadores.

Cuarta parte. Integración del decodificador de BCD a 7 segmentos con el

decodificador de 2 a 4.

1. Descripción del problema.

Integre en un proyecto los dos circuitos decodificadores. En este diseño se tienen como

entrada un código binario de cuatro bits el cual se convertirá a decimal y se mostrará en

los visualizadores, y además se necesitan otros dos interruptores para seleccionar el

visualizador en el que se quiere mostrar el número decimal.

2. Determine el número de entradas y salidas.

2.1. Dibuje la caja negra, considerando sólo las entradas y salidas de su proyecto, este es

el diagrama equivalente a la entidad, que sólo incluye los dispositivos externos como

son los interruptores y visualizadores. Registre esta información en la sección de

resultados y conclusiones.

2.2. Dentro de la caja negra (entidad), dibuje los dos decodificadores (componentes) y

determine cómo deben ser las conexiones. Registre esta información en la sección de

resultados y conclusiones.

Maribel Gómez Franco S2-2016 5

Circuitos Digitales Práctica 11. Decodificadores

2.3. Identifique si se necesitan señales internas.

3. Diseño del proyecto decodificadores en el FPGA

3.1. Cree un nuevo proyecto, al nombre agréguele tres iniciales o número de

matrícula.

3.2. Configure el dispositivo de acuerdo a la tarjeta BASYS que utilice para la

realización de la práctica.

3.3. Copie los archivos del decodificador de BCD a 7 segmentos y el decodificador de

2 a 4 con extensión vhd a la carpeta del nuevo proyecto.

3.4. Seleccione Project>New Source>VHDL Module para agregar la entidad del

archivo fuente en VHDL. Asigne un nombre al archivo .

3.4.1. Escriba el código de la entidad en la sección de resultados y conclusiones.

3.4.2. En la ventana del módulo VHDL registre las señales de entrada y salida

de la entidad.

3.5. En este proyecto llamará a los dos componentes ya creados.

a) Seleccione Project>Add Source agregue el archivo VHD del decodificador de BCD

a 7 segmentos que diseñó en la práctica 9.

b) Seleccione Project>Add Source agregue el archivo VHD del decodificador de 2 a

4 que diseñó en la segunda parte de esta práctica.

c) Asegúrese de que el archivo de este proyecto esté configurado como Top Design.

3.6. Diseño de la arquitectura.

3.6.1. Declare el componente decodificador de BCD a 7 segmentos que diseñó en

la práctica 9. Puede copiar la entidad completa y reemplazar la palabra entity

por component.

3.6.2. Declare el componente decodificador de 2 a 4 diseñó en la tercera parte de

esta práctica. Puede copiar la entidad completa y reemplazar la palabra

entity por component.

3.6.3. Después del begin, debe especificar la manera en que se van a conectar

los componentes, la declaración debe ser de la siguiente manera:

a. asigne una etiqueta de identificación a los componentes seguido de dos puntos

:,

b. enseguida escriba el nombre de su componente tal y como lo declaró en la

entidad,

c. después va la palabra reservada PORT MAP para declarar las conexiones de

los decodificadores, entre paréntesis debe escribir las terminales

correspondientes a la entidad de su proyecto, y debe seguir el orden de las

señales tal y como se declararon en la entidad de los componentes.

4. Síntesis e implementación del diseño

El diseño se tiene que sintetizar e implementar para verificar si hay errores y corregirlos

antes de ejecutar una simulación funcional o de descargar el archivo en el dispositivo.

Maribel Gómez Franco S2-2016 6

Circuitos Digitales Práctica 11. Decodificadores

4.1. Seleccione el archivo principal de esta práctica.

4.2. En el panel de procesos seleccione Synthesize-XST, para sintetizar el diseño. Si

se generan errores es necesario corregirlos, y volver a sintetizar hasta que el

diseño sea el correcto.

5. Creación del archivo de prueba para el proyecto decodificadores

Seleccione Project>New Source para agregar el archivo de prueba en VHDL que se

utilizará para la simulación. Asigne un nombre al archivo. Asegúrese de que la opción

Add to Project está seleccionada, de lo contrario tendrá que agregar el archivo

manualmente.

Seleccione el archivo VHD con el cual se asociará el archivo de prueba. Seleccione Next,

en este momento el ISE genera una plantilla para crear las señales de entrada para la

simulación. Debe generar las señales de las líneas de selección del decodificador y del

dato de entrada BCD.

6. Simulación del proyecto decodificadores

En la ventana de diseño seleccione la opción de simulación, asegúrese de seleccionar en

jerarquía el archivo de prueba creado. En el panel de proceso, seleccione Behavioral

Check Syntax, si no hay errores esta opción se pone en verde, indicando que el archivo

es correcto. Seleccione Simulate Behavioral Model para ejecutar el simulador ISim.

Analice el diagrama de tiempos generado por ISim, y asegúrese de que su diseño funciona

adecuadamente.

7. Implementación y verificación de funcionamiento del proyecto decodificadores

7.1. Asignación de terminales

a. Genere y edite el archivo tipo ucf, para asignar las terminales del FPGA a los

puertos. Process> NewSource> Implement Constraints.

b. En el panel de diseño, seleccione el archivo fuente y en el panel de procesos

seleccione “Implement Design” o “Implement Top Module”, en este punto ISE

hace el mapeo y la asignación de terminales, ver figura 1.

7.2. Generación del archivo de programación del FPGA

a. En el panel de procesos presione el botón derecho del ratón sobre “Generate

Programming File” elija propiedades y en la ventana que aparece seleccione

“Startup Options”. Asegúrese de seleccionar en FPGA Start-Up Clock la opción

JTAG Clock (por omisión es CCLK).

b. En el panel de procesos seleccione “Generate Programming File”, para crear el

archivo .bit, el cual se descargará al FPGA de la tarjeta Basys de Digitent. Este

archivo se almacena en la carpeta del proyecto.

7.3. Configuración y programación de la tarjeta Basys de Digilent

a. Conecte la tarjeta Basys de Digilent a cualquier puerto USB disponible de su

computadora. Ejecute el programa Digilent Adept.

Maribel Gómez Franco S2-2016 7

Circuitos Digitales Práctica 11. Decodificadores

b. Agregue el archivo tipo bit creado por ISE, el cual se localiza en la carpeta del

proyecto, seleccione Program para descargar el código tipo bit hacia el FPGA.

8. Verificación

Configure los interruptores de la tarjeta BASYS para comprobar el funcionamiento del

circuito. En la tabla 10.4 de la sección de resultados y conclusiones registre esta

información.

Revisión de práctica

Los dos proyectos de VHDL, decodificador de 2 a 4 y decodificadores requieren revisión

y firma.

Subir al aula virtual los archivos de simulación en Multisim y los dos proyectos generados

en Xilinx, en la carpeta correspondiente.

Referencias

Maribel Gómez Franco. Apuntes de la materia Circuitos Digitales. Año 2013. Cd. Juárez,

Ch. Universidad Autónoma de Ciudad Juárez.

Stephen Brown y Zvonko Vranesic. “Fundamentals of Digital Logic with VHDL Design”.

Second Edition. Ed. McGrawHill USA, 2005.

Tocci, Ronald. “Sistemas Digitales Principios y Aplicaciones”. Sexta edición. Ed. Prentice

Hall, México, 1996.

Floyd, T.L. “Fundamentos de Sistemas Digitales”. Ed. Prentice Hall. Sexta edición,

Madrid, 1997.

Lab 3 “Programming Combinational Logic on Basys FPGA Board” Manual EE120A Logic

Design University of California – Riverside.

Digital Circuit Design Using Xilinx ISE Tools.

Digilent Basys Board Reference Manual.

www.digilent.com;

www.xilinx.com

Maribel Gómez Franco S2-2016 8

Circuitos Digitales Práctica 11. Decodificadores

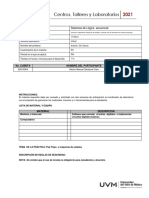

REPORTE

Integrantes:

Matrícula Nombre

Fecha de revisión: Fecha de entrega:

Revisó: Grupo:

Evaluación

Criterio Puntuación máxima Puntuación obtenida

Revisión 30%

Procedimiento 30%

Preguntas 15%

Conclusiones 5%

Anexos:

Simulación Multisim 10%

Proyecto Xilinx 10%

Calificación

Maribel Gómez Franco S2-2016 9

Circuitos Digitales Práctica 11. Decodificadores

Resultados y conclusiones

Primera parte

1. Símbolo lógico del decodificador de 2 a 4, 74LS139N, incluya la lógica de operación

de las señales de habilitación y salida.

2. Tabla de funcionamiento del decodificar de 2 a 4, 74LS139N.

Tabla 11.1 Tabla de funcionamiento del decodificador de 2 a 4.

Maribel Gómez Franco S2-2016 10

Circuitos Digitales Práctica 11. Decodificadores

Segunda parte. Diseño de un decodificador de 2 a 4 en VHDL

1. Escriba el código que define a la entidad del decodificador de 2 a 4.

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

2. Escriba el código que define a la arquitectura del decodificador de 2 a 4.

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

3. Escriba el código del archivo UCF del decodificador de 2 a 4.

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

Maribel Gómez Franco S2-2016 11

Circuitos Digitales Práctica 11. Decodificadores

4. Configure las señales de entrada para verificar el funcionamiento de su diseño. En la

primera columna de la tabla 3 escriba las combinaciones de las señales de entrada,

y en la segunda columna registre el nivel lógico de los LEDs.

Entrada Salidas

Tabla 11.2 Verificación de funcionamiento del decodificador de 2 a 4.

Tercera parte. Simulación del decodificador de 2 a 4 y del decodificador de

BCD a 7 segmentos en Multisim.

1. Diagrama de conexiones de los dos decodificadores, los cuatro visualizadores y los

cuatro transistores.

Maribel Gómez Franco S2-2016 12

Circuitos Digitales Práctica 11. Decodificadores

2. Tabla de verdad del proyecto decodificadores.

Entradas Deco 2 a 4 Entradas Deco BCD a 7 V3 V2 V1 V0

Tabla 11.3 Tabla de verdad del proyecto decodificadores.

Cuarta parte. Integración del decodificador de BCD a 7 segmentos con el

decodificador de 2 a 4.

1. Dibuje la caja negra, considerando sólo las entradas y salidas de su proyecto.

1.1. Dentro de la caja negra (entidad), dibuje los dos decodificadores (componentes) y

determine cómo deben ser las conexiones.

Maribel Gómez Franco S2-2016 13

Circuitos Digitales Práctica 11. Decodificadores

2. Escriba el código que define a la entidad del proyecto decodificadores.

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

______________________________________________________________________________________

3. Tabla de funcionamiento del proyecto decodificadores. En la tercera columna escriba

el número decimal que se muestra en el visualizador seleccionado por el

decodificador.

Entradas Deco 2 a 4 Entradas Deco BCD a 7 V3 V2 V1 V0

Tabla 11.4 Tabla de funcionamiento del proyecto decodificadores.

Preguntas

1. ¿Para qué se utiliza la entidad?

2. ¿Para qué se utiliza la arquitectura?

Maribel Gómez Franco S2-2016 14

Circuitos Digitales Práctica 11. Decodificadores

3. ¿Para qué se utiliza el archivo con extensión ucf?

4. ¿Qué tipo de visualizador utiliza cualquiera de las tarjetas BASYS?

5. ¿Con qué nivel lógico habilitó las salidas del decodificador de 2 a 4? ¿Por qué?

6. Describa cómo se utiliza la arquitectura estructural.

Conclusiones por integrante

Maribel Gómez Franco S2-2016 15

También podría gustarte

- Control neuronal y difuso para sistemas fotovoltaicosDe EverandControl neuronal y difuso para sistemas fotovoltaicosAún no hay calificaciones

- Simulación de circuitos electrónicos con OrCAD® PSpice®De EverandSimulación de circuitos electrónicos con OrCAD® PSpice®Aún no hay calificaciones

- CD PR11 DecodificadoresDocumento15 páginasCD PR11 DecodificadoresSamuel Larrinaga MoranAún no hay calificaciones

- Decodificador 5 a 32 con módulos 74154Documento23 páginasDecodificador 5 a 32 con módulos 74154Juan CarlosAún no hay calificaciones

- Universidad Tecnol Gica de El Salvador PDFDocumento20 páginasUniversidad Tecnol Gica de El Salvador PDFBrayan ValienteAún no hay calificaciones

- Práctica 2Documento6 páginasPráctica 2Julio A. PadillaAún no hay calificaciones

- Kedi U2 A2 Yybm PDFDocumento6 páginasKedi U2 A2 Yybm PDFIsmael ChoixAún no hay calificaciones

- Practica 6 Administrador 7segmentoDocumento5 páginasPractica 6 Administrador 7segmentoIan CaballeroAún no hay calificaciones

- Practica-Contador de 0-7 VHDLDocumento13 páginasPractica-Contador de 0-7 VHDLR He MaAún no hay calificaciones

- Practica 7. Convertidores DA, AD y Controlador PIDDocumento12 páginasPractica 7. Convertidores DA, AD y Controlador PIDDavidWebsterAún no hay calificaciones

- Manual de Usuario PIC PROGRAMMER Electronilab - Co - PDFDocumento22 páginasManual de Usuario PIC PROGRAMMER Electronilab - Co - PDFPedro GarciaAún no hay calificaciones

- Practica 2 Sumador Restador de 2 Numeros Con 5 BitsDocumento12 páginasPractica 2 Sumador Restador de 2 Numeros Con 5 BitsRoberto Daniel Sanchez Hernandez50% (2)

- Kedi U2 A2 ErsrDocumento14 páginasKedi U2 A2 ErsrYo no fuíAún no hay calificaciones

- PIC Entrenador 40Documento5 páginasPIC Entrenador 40Cristian Garcia AlarcònAún no hay calificaciones

- Informe de Micros Contador Descendente Del 9 Al 0Documento10 páginasInforme de Micros Contador Descendente Del 9 Al 0Alex AndradeAún no hay calificaciones

- Convertidor BCD códigoDocumento4 páginasConvertidor BCD códigoKaren LópezAún no hay calificaciones

- Práctica Introducción A Los PLDDocumento15 páginasPráctica Introducción A Los PLDAlex RMAún no hay calificaciones

- Diseño lógico de decodificadores para display de 7 segmentosDocumento12 páginasDiseño lógico de decodificadores para display de 7 segmentosKeen Brayan Huaraca CalderonAún no hay calificaciones

- Laboratorio de Electrónica Digital - Parctica 2 Fecha de NacimientoDocumento14 páginasLaboratorio de Electrónica Digital - Parctica 2 Fecha de NacimientoRomina OropezaAún no hay calificaciones

- Display de 7 segmentos y reloj digitalDocumento14 páginasDisplay de 7 segmentos y reloj digitalIruy MartinezAún no hay calificaciones

- Practica No 5 LAB PIC18F MPLABX 2019Documento5 páginasPractica No 5 LAB PIC18F MPLABX 2019Ader Hariel Treminio MontoyaAún no hay calificaciones

- Programador PICs Enigma USBDocumento7 páginasProgramador PICs Enigma USBRaul MonroyAún no hay calificaciones

- DECODIFICADORESDocumento9 páginasDECODIFICADORESYajaira Yaguapaz VeraAún no hay calificaciones

- Trabajo IndividualDocumento9 páginasTrabajo IndividualAxelAún no hay calificaciones

- LABORATORIO 1 Manejo de Puertos DigitalesDocumento10 páginasLABORATORIO 1 Manejo de Puertos Digitalesmax trAún no hay calificaciones

- LABORATORIO 2 ATMEGA Puerto AnalógicoDocumento7 páginasLABORATORIO 2 ATMEGA Puerto AnalógicoReynaldo Conde Canqui100% (1)

- Decodificadores y circuitos combinacionalesDocumento6 páginasDecodificadores y circuitos combinacionalesManuel Campos BorrasAún no hay calificaciones

- Lab 04 Circuitos Digitales UNMSMDocumento7 páginasLab 04 Circuitos Digitales UNMSMBrandon RH ErickBraddAún no hay calificaciones

- Lab07 ConversionAD PIC18F4550Documento22 páginasLab07 ConversionAD PIC18F4550Fabrizio Santiago Amaya CanchumantaAún no hay calificaciones

- Informe Previo 4Documento4 páginasInforme Previo 4MiguelAngelArapa100% (1)

- Práctica 1Documento5 páginasPráctica 1Jorge Miguel Barajas BustamanteAún no hay calificaciones

- AvrDocumento15 páginasAvrOmar BarrionuevoAún no hay calificaciones

- Practica 1 - 2do ParcialDocumento5 páginasPractica 1 - 2do ParcialHéctor SandovalAún no hay calificaciones

- ADC PIC 16F877A MikroBasic 40carDocumento8 páginasADC PIC 16F877A MikroBasic 40carIván Ivanov100% (1)

- CUESTIONARIO PREVIO N°5 (QUINTANA, JOHN)Documento16 páginasCUESTIONARIO PREVIO N°5 (QUINTANA, JOHN)John QuintanaAún no hay calificaciones

- ProyectoDocumento11 páginasProyectoAnonymous IhhGYMAún no hay calificaciones

- Microcontrolador Dspic VoltimetroDocumento6 páginasMicrocontrolador Dspic VoltimetroChristian QCAún no hay calificaciones

- Postinforme 5 EdisonA CarlosC KincinioI AlexPDocumento7 páginasPostinforme 5 EdisonA CarlosC KincinioI AlexPEdison Abado AnccoAún no hay calificaciones

- Practica U1 Equipo#11Documento25 páginasPractica U1 Equipo#11KIMBERLY JANETH VERDUZCO ACOSTAAún no hay calificaciones

- Mostrar Valores en LCD Con ArduinoDocumento2 páginasMostrar Valores en LCD Con ArduinoMC. Rene Solis R.100% (1)

- Práctica 1 Led IntermitenteDocumento10 páginasPráctica 1 Led IntermitenteJavier CamachoAún no hay calificaciones

- Informe #4Documento2 páginasInforme #4Duo Doble AAún no hay calificaciones

- Como Hacer Un PCB (Reporte)Documento16 páginasComo Hacer Un PCB (Reporte)Dario Sebastian Lemus SandovalAún no hay calificaciones

- Entrenador y Tarjeta de Adquisición de Datos Con El PIC 18F2550 y LabviewDocumento8 páginasEntrenador y Tarjeta de Adquisición de Datos Con El PIC 18F2550 y LabviewFranklin Bustinza MacedoAún no hay calificaciones

- Contador de DecadasDocumento12 páginasContador de Decadasjose manuel sotoAún no hay calificaciones

- Clase 2.2 - Assembler - Practica - 1Documento11 páginasClase 2.2 - Assembler - Practica - 1brandonAún no hay calificaciones

- Estación Meteorológica - Sensor Si7021, Placa Mini Microcontroladora ESP8266 Wemos D1, Nokia 5510 84 - 48 LCDDocumento7 páginasEstación Meteorológica - Sensor Si7021, Placa Mini Microcontroladora ESP8266 Wemos D1, Nokia 5510 84 - 48 LCDAndres Rosano TabarezAún no hay calificaciones

- Arduino Mega Controller Con Esp8266 OkDocumento12 páginasArduino Mega Controller Con Esp8266 OkAlexisHernandezAún no hay calificaciones

- Decodificador 7 SegmentosDocumento9 páginasDecodificador 7 SegmentosCESAR DURANAún no hay calificaciones

- Tutorial Pickit2 v2.6Documento19 páginasTutorial Pickit2 v2.6Daɳɳy ElSamAún no hay calificaciones

- Fundamentosdecircuitosdigitales 2 ListoDocumento38 páginasFundamentosdecircuitosdigitales 2 Listojvicec8260Aún no hay calificaciones

- DecoDocumento7 páginasDecoJeimss MoraAún no hay calificaciones

- Modelo de Informe 2 UrpDocumento12 páginasModelo de Informe 2 UrpMARTIN ALONSO HINOJOSA CASTROAún no hay calificaciones

- Guia 2Documento26 páginasGuia 2Kenide ArroyoAún no hay calificaciones

- Práctica 3 Microcontroladores FernandoDocumento20 páginasPráctica 3 Microcontroladores FernandoJulio100% (1)

- Manual de Usuario SDM Board R5 v1.50Documento14 páginasManual de Usuario SDM Board R5 v1.50jairoAún no hay calificaciones

- Decodificador BCD A 7 Segmentos 2009Documento6 páginasDecodificador BCD A 7 Segmentos 2009Rosario Trejo CerinoAún no hay calificaciones

- Compilador C CCS y Simulador Proteus para Microcontroladores PICDe EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICCalificación: 2.5 de 5 estrellas2.5/5 (5)

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Iit 2Documento34 páginasIit 2Ayrin LinogeAún no hay calificaciones

- Guerra de ReformaDocumento7 páginasGuerra de ReformaAyrin LinogeAún no hay calificaciones

- Modelo Apa para Presentacion de TareasDocumento3 páginasModelo Apa para Presentacion de TareasAyrin LinogeAún no hay calificaciones

- Maquina UniversalDocumento11 páginasMaquina UniversalAyrin LinogeAún no hay calificaciones

- Cuestionario Mecanico!Documento6 páginasCuestionario Mecanico!Ayrin LinogeAún no hay calificaciones

- Plan de Negocio FORMATODocumento15 páginasPlan de Negocio FORMATOAyrin LinogeAún no hay calificaciones

- Formato para La Presentación de Proyectos D.E.Documento1 páginaFormato para La Presentación de Proyectos D.E.Ayrin LinogeAún no hay calificaciones

- Plan de Negocio-InicioDocumento2 páginasPlan de Negocio-InicioAyrin LinogeAún no hay calificaciones

- Ejercicios de Estructuras Selectivas Compuestas y Múltiples.Documento7 páginasEjercicios de Estructuras Selectivas Compuestas y Múltiples.Luis CarbajalAún no hay calificaciones

- El cine como recurso educativoDocumento5 páginasEl cine como recurso educativoAndreaAún no hay calificaciones

- Experimento de CargadorDocumento10 páginasExperimento de CargadorGraecia Leges Miriam Butrón GallegosAún no hay calificaciones

- Reparación de orejas rotas en cucharónDocumento4 páginasReparación de orejas rotas en cucharónAndree Ayma NuñezAún no hay calificaciones

- Ejercicios Linux - 02Documento11 páginasEjercicios Linux - 02PEREZ RIVAS YESSICAAún no hay calificaciones

- Pronosticos Basados en Factores de Tendencia y EstacionalesDocumento3 páginasPronosticos Basados en Factores de Tendencia y EstacionalesMiguel DelgadoAún no hay calificaciones

- SandroDocumento21 páginasSandroErik Moreno LunaAún no hay calificaciones

- Aguaymanto DeshidratadoDocumento48 páginasAguaymanto DeshidratadoJhovany Ysabel Morales TorresAún no hay calificaciones

- Ética y Servicio PúblicoDocumento8 páginasÉtica y Servicio PúblicoPeggy Peggy MuñozAún no hay calificaciones

- Desempleo JuvenilDocumento4 páginasDesempleo Juvenilfrancisco espinozaAún no hay calificaciones

- Salazar GMC SDDocumento116 páginasSalazar GMC SDBaul CitoAún no hay calificaciones

- Gestión Logística Aduanal21Documento14 páginasGestión Logística Aduanal21lynette Núñez PortilloAún no hay calificaciones

- Modelo de 1er Examen Sistemas Contables Carla KranevitterDocumento3 páginasModelo de 1er Examen Sistemas Contables Carla KranevitterEly ClaureAún no hay calificaciones

- Modificatoria Ley 29783Documento18 páginasModificatoria Ley 29783Alejandro Herrera CerquenAún no hay calificaciones

- Procedimiento de Uso Cuidado y Mantenimiento de Patin HidraulicoDocumento7 páginasProcedimiento de Uso Cuidado y Mantenimiento de Patin HidraulicoKaren EstradaAún no hay calificaciones

- Sistema de Gestion de Recursos HumanosDocumento39 páginasSistema de Gestion de Recursos HumanosSTEPHANNY100% (1)

- SO - 023-Procedimiento Trabajos en Caliente-V01Documento31 páginasSO - 023-Procedimiento Trabajos en Caliente-V01Claudia DiazAún no hay calificaciones

- Tesis PLAN DE MANTENIMIENTO PREVENTIVODocumento172 páginasTesis PLAN DE MANTENIMIENTO PREVENTIVOjgcm8585% (40)

- Carta Presentacion y Tarifas Sra JoannaDocumento2 páginasCarta Presentacion y Tarifas Sra JoannaPaula ArbelaezAún no hay calificaciones

- Amalgamas DentalesDocumento10 páginasAmalgamas DentalesRous Luna TurpoAún no hay calificaciones

- 3 Interes CompuestoDocumento53 páginas3 Interes CompuestoJorge Martinez50% (4)

- GLOSARIO GeNERALDocumento175 páginasGLOSARIO GeNERALyustinAún no hay calificaciones

- RA10 Act4 Instrucciones Evaluacion EA1Documento4 páginasRA10 Act4 Instrucciones Evaluacion EA1FRANCO ALBERTO VALENZUELA ACEVEDOAún no hay calificaciones

- Carta Gantt-HitosDocumento16 páginasCarta Gantt-HitosCarlos Javier CartesAún no hay calificaciones

- Aplicación de Medicamento EnfermeriaDocumento7 páginasAplicación de Medicamento EnfermeriaJesus Alberto Rodríguez PortilloAún no hay calificaciones

- Calculo Factor de CaidaDocumento1 páginaCalculo Factor de CaidaFrancisco ValenzuelaAún no hay calificaciones

- Economía y mercadosDocumento11 páginasEconomía y mercadosalfredoAún no hay calificaciones

- 12-Notas de Concepto para Entender Mejor El Estado, Las Políticas Públicas Y Gestión - CAF-2017 FinalDocumento32 páginas12-Notas de Concepto para Entender Mejor El Estado, Las Políticas Públicas Y Gestión - CAF-2017 FinalCarlos Javier EstradaAún no hay calificaciones

- Citaciones Norma APA 7Documento16 páginasCitaciones Norma APA 7yesica vegaAún no hay calificaciones

- Sistemas de Automatización S6Documento9 páginasSistemas de Automatización S6MelAún no hay calificaciones