Documentos de Académico

Documentos de Profesional

Documentos de Cultura

2023 TP5 - Familias Logicas

Cargado por

Leo PereiraDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

2023 TP5 - Familias Logicas

Cargado por

Leo PereiraCopyright:

Formatos disponibles

TÉCNICAS DIGITALES I (PLAN 2023)

TRABAJO PRÁCTICO Nro. 5

Familias Lógicas

1) Calcular cuantas compuertas AND SN74LS08 (serie 74LS) pueden estar cargadas simultáneamente de:

a) Una compuerta AND SN74LS08 (serie 74LS).

b) Una compuerta AND 74ACT08 (serie 74ACT).

c) Una compuerta AND MC74HC08 (serie 74HC).

d) Una compuerta AND HEF4081B (serie 4000B) alimentada con 5V.

Nota: se deberán consultar la hoja de datos del fabricante para poder realizar los cálculos.

X CI1: SN74LS08

CI2: SN74LS08

CIn: SN74LS08

2) Para los distintos casos del problema 1), calcular los márgenes de inmunidad contra el ruido utilizando:

a) Las formulas genéricas para el cálculo de inmunidad al ruido, tanto para TTL como para CMOS,

explicadas en clase.

b) Los valores indicados en las hojas de datos.

3) Una familia lógica llamada "A" que se alimenta con +5V, posee las siguientes características

VOHmín = 2.2V VOLmáx = 0.9V

VIHmín = 1.8V VILmáx = 1.1V

IOHmáx = -1 mA IOLmáx = 10 mA

IIHmáx = 500uA IILmáx = -2 mA

Pd = 60mW Factor de mérito = 120

pJ

a) Calcular su fan-out, sus márgenes de inmunidad contra el ruido, y su tiempo de propagación

b) Determinar, justificando, si existe compatibilidad entre una salida de una compuerta "A" y la entrada

de una TTL de la serie 74LS.

c) Determinar, justificando, si existe compatibilidad entre la salida de una compuerta TTL de la serie

74LS y una entrada de una compuerta "A"

d) En los casos encontrados compatibles en los puntos b) y c), calcular el fan-out y el margen de

inmunidad contra el ruido.

4) Si las 2 compuertas son de tecnología CMOS, alimentadas con 5 V (VDD) y el circuito que utilizará la

función Y require un ‘0’ = 0V y un ‘1’ = 12V; indicar:

a) Valor de Z.

b) Configuración de salida de la compuerta NAND y del Inversor.

c) Es factible la construcción del circuito y de ser factible cual es el

valor de la tensión +V.

Confeccionó Pág. 1 Año: 2023

Ing. Ramos, Fernando

Ing. Nassipián, R.V.

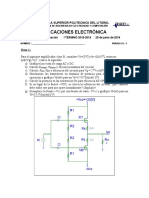

TÉCNICAS DIGITALES I (PLAN 2023)

TRABAJO PRÁCTICO Nro. 5

Familias Lógicas

5) Diseñar con compuertas universales un convertidor de Aiken a BCD Natural, pero:

a) Implementarlo tratando de minimizar el número de circuitos integrados necesarios con

compuertas CMOS de la serie MC de ON Semiconductor.

b) Estimar el tiempo de propagación del circuito resultante.

6) Los siguientes circuitos (A y B) utilizan el retardo que produce el inversor para dar a su salida un pulso de

duración igual a dicho retardo, cuando se presenta a la entrada un determinado frente. Dar las formas de

onda, suponiendo que ingresa una señal cuadrada, e indicar que tipo de frente (ascendente o descendente)

reconocen. Suponer que el período de la onda cuadrada es mucho mayor que el retardo del inversor.

2

1

Cto. A 3 U3A

U2B

4 3

1

Cto. B

3

U4A

5 U2C

6 2

7) Para un inversor CMOS, suponga que VDD = 3,3V; CL = 50 pF; CPD = 18 pF; y la frecuencia de

trabajo es de 95 MHz. Calcule:

a) Calcule la disipación de potencia de un inversor. Justifique la respuesta.

b) Si se asume que un chip industrial que contiene el equivalente de 10.000 inversores (similares a

los descriptos) y que como máximo el 22 % de los inversores cambia valores en un instante

específico y el resto permanece en ‘0’ o en ‘1’, Calcule la potencia disipada por el chip.

c) Se diseño para alimentar al componente una fuente de alimentación que suministra 3,3 V y su

potencia máxima es de 160 W. Dicha fuente es apropiada para funcionar con el IC en la condición

del punto b? Justifique la respuesta.

Confeccionó Pág. 2 Año: 2023

Ing. Ramos, Fernando

Ing. Nassipián, R.V.

TÉCNICAS DIGITALES I (PLAN 2023)

TRABAJO PRÁCTICO Nro. 5

Familias Lógicas

OPCIONALES

1) Dado el circuito de la figura que utiliza compuertas TTL de la serie LS, calcular el valor máximo y

mínimo de la resistencia de carga R sabiendo que las compuertas de colector abierto tienen una

corriente de fuga Icex de 250 uA.

+VCC

R

1 3

U5A

2 12

6 11

4 13 U5D

U5B

5

1

8 3

9 U5C U6A

10

2

Viendo el gráfico:

a) ¿Cúantos circuitos integrados se están utilizando?

b) ¿Podría deducir de cuántos pines son dichos integrados?

c) ¿Porqué no aparece el pin 8 del U5?.

2) Para una compuerta NAND CD4011 (4-NAND de 2 entradas) cuya tensión de alimentación VDD =

10 V y cuyos datos se dan más abajo, se pide:

a) Calcular la Potencia Dinámica suponiendo que el CL = 50 pF y la frecuencia de trabajo es de

1MHZ. Si disminuyó la frecuencia, que ocurre con la Potencia Dinámica.

b) Calcular el Tiempo de Propagación (tp), suponiendo siempre CL = 50 pF.

c) Si construye un inversor con integrados CD4011, cual será el tiempo de Propagación. Justificar.

d) Si construye una compuerta OR, utilizando solo integrados CD 4011, cuál es la Potencia

Dinámica del circuito y su tiempo de Propagación.

Confeccionó Pág. 3 Año: 2023

Ing. Ramos, Fernando

Ing. Nassipián, R.V.

TÉCNICAS DIGITALES I (PLAN 2023)

TRABAJO PRÁCTICO Nro. 5

Familias Lógicas

3) Un famoso diseñador lógico decidió abandonar la enseñanza y hacer fortuna con la licencia del

circuito que se encuentra más abajo. Se pide :

a) Etiquete las entradas y salidas del circuito con los nombres más apropiados para el mismo .

b) Explique el funcionamiento del circuito.

Confeccionó Pág. 4 Año: 2023

Ing. Ramos, Fernando

Ing. Nassipián, R.V.

También podría gustarte

- UNM2021-TD1-TP5 - Familias LogicasDocumento4 páginasUNM2021-TD1-TP5 - Familias LogicasAriel Eduardo FariasAún no hay calificaciones

- UNLaM2020 IntSistDig TP5 - Familias LogicasDocumento4 páginasUNLaM2020 IntSistDig TP5 - Familias LogicasGabrielSoteloDuarteAún no hay calificaciones

- TP05-Familias Logicas 2019Documento5 páginasTP05-Familias Logicas 2019gabrielAún no hay calificaciones

- TP Area DigitalesDocumento10 páginasTP Area DigitalesCelesteCebedioAún no hay calificaciones

- LAB 3 503 Li 2021Documento7 páginasLAB 3 503 Li 2021Moisés MartínAún no hay calificaciones

- Practica Experimental N°03 - Carga y Descarga de Un CondensadorDocumento9 páginasPractica Experimental N°03 - Carga y Descarga de Un CondensadorOrlandoChirinosAún no hay calificaciones

- ExamDocumento50 páginasExamEduardo TexisAún no hay calificaciones

- Laboratorio 5-BDocumento6 páginasLaboratorio 5-BYONAR ESTEBAN GELPUD POTOSIAún no hay calificaciones

- Práctica #1 ETN606Documento1 páginaPráctica #1 ETN606Gonzalo GrimaldiAún no hay calificaciones

- Fís 225, Exámen Final HDocumento2 páginasFís 225, Exámen Final Hroque bretonAún no hay calificaciones

- Feb 05Documento10 páginasFeb 05Sasuke BacusAún no hay calificaciones

- Feb 00Documento10 páginasFeb 00Sasuke BacusAún no hay calificaciones

- Sistemas Logicos - 2 - Guia de PracticosDocumento23 páginasSistemas Logicos - 2 - Guia de PracticosPieroAún no hay calificaciones

- Guía EjerciciosDocumento2 páginasGuía EjerciciosEddie Marin50% (2)

- Práctica CircuitosDocumento5 páginasPráctica CircuitosNero BoanergesAún no hay calificaciones

- Taller 5 - Inversores (1-2023)Documento3 páginasTaller 5 - Inversores (1-2023)Pokemo DelsoldevastadoAún no hay calificaciones

- Informe 3Documento8 páginasInforme 3Rolando Choque CahuanaAún no hay calificaciones

- Examen MicrocontroladoresDocumento6 páginasExamen MicrocontroladoresKathiam JaretAún no hay calificaciones

- PARCIAL1 (Solcucion)Documento11 páginasPARCIAL1 (Solcucion)Jhon LlachoAún no hay calificaciones

- PARCIAL1 (Solcucion)Documento11 páginasPARCIAL1 (Solcucion)Jhon Llacho100% (1)

- Informe 1 - Grupo 04 - ViernesDocumento11 páginasInforme 1 - Grupo 04 - ViernesSergio Andres Bernal TorresAún no hay calificaciones

- 2 Parcial - Introd Siste Digitales - 2 - 7 - 2019 - TNDocumento2 páginas2 Parcial - Introd Siste Digitales - 2 - 7 - 2019 - TNGabriel Sotelo0% (1)

- Lab Opamp 2Documento4 páginasLab Opamp 2Anonymous ekB7qEsdAún no hay calificaciones

- Astables y Monostables Informe Final 2Documento13 páginasAstables y Monostables Informe Final 2Erick Alvarez CastañedaAún no hay calificaciones

- ContadorDocumento8 páginasContadorAkku NattoralikAún no hay calificaciones

- Electronica IIDocumento6 páginasElectronica IIMEKArotAún no hay calificaciones

- Caracteristicas de Las Compuertas TTL y CmosDocumento6 páginasCaracteristicas de Las Compuertas TTL y CmosMario Asuaje100% (1)

- Informe de Laboratorio 3 Circuitos Multivibradores MonoestablesDocumento6 páginasInforme de Laboratorio 3 Circuitos Multivibradores MonoestablesDavid Ajhuacho IncaAún no hay calificaciones

- CE3 Lab2Documento9 páginasCE3 Lab2Jhosep Jeanpool Valdez LuqueAún no hay calificaciones

- PARCIAL1 (Solucion)Documento15 páginasPARCIAL1 (Solucion)Samantha Janet Valdivia PangoAún no hay calificaciones

- CEA Lab2Documento11 páginasCEA Lab2Shanella ChallcoAún no hay calificaciones

- Practica 3Documento9 páginasPractica 3Claudia AlmanzaAún no hay calificaciones

- Guía de Laboratorio Convertidor BOOSTDocumento5 páginasGuía de Laboratorio Convertidor BOOSTWilson AndrésAún no hay calificaciones

- Memoria de Calculo ElctricoDocumento5 páginasMemoria de Calculo ElctricoyecodeAún no hay calificaciones

- Laboratorio 5 Etn 601 I 2016Documento7 páginasLaboratorio 5 Etn 601 I 2016Daniel AguilarAún no hay calificaciones

- Informe Laboratorio BJT Zonas de OperaciónDocumento13 páginasInforme Laboratorio BJT Zonas de OperaciónErick Jesús Rodríguez DávilaAún no hay calificaciones

- Practica 6 PDFDocumento8 páginasPractica 6 PDFLuis Angel UgarteAún no hay calificaciones

- Informe de Laboratorio N°2Documento6 páginasInforme de Laboratorio N°2Karlos QuiquiaAún no hay calificaciones

- Practica #5 - Gráfica Del Transistor BJTDocumento5 páginasPractica #5 - Gráfica Del Transistor BJTMax OrnelasAún no hay calificaciones

- Prob de RCDocumento9 páginasProb de RCHéctor Peña SaavedraAún no hay calificaciones

- Practica 1 Sincronas Ime FescDocumento8 páginasPractica 1 Sincronas Ime FescDiego RGAún no hay calificaciones

- Lab 6 503 Ii 2020Documento7 páginasLab 6 503 Ii 2020Liz Mar CieloAún no hay calificaciones

- Ae Deber 5 1t 2022espaciadoDocumento11 páginasAe Deber 5 1t 2022espaciadoGilberto VeraAún no hay calificaciones

- Segunda Practica Calificada de Electronica de Potencia C4 - 5to A 2020-1Documento6 páginasSegunda Practica Calificada de Electronica de Potencia C4 - 5to A 2020-1Yordi AlvitrezAún no hay calificaciones

- Sep 03Documento9 páginasSep 03Sasuke BacusAún no hay calificaciones

- Practica1DDsem2020 IIDocumento3 páginasPractica1DDsem2020 IIJhon CaceresAún no hay calificaciones

- 2.3. Prepa PWM BUCKDocumento3 páginas2.3. Prepa PWM BUCKSelena CarrilloAún no hay calificaciones

- 1565966071ejercicios Ii 2019 Etn 503Documento35 páginas1565966071ejercicios Ii 2019 Etn 503Jhan KanamaAún no hay calificaciones

- Laboratorio de Circuitos Digitales 2Documento19 páginasLaboratorio de Circuitos Digitales 2Fidel PalmaAún no hay calificaciones

- Sep 01Documento10 páginasSep 01Sasuke BacusAún no hay calificaciones

- Circuitos Electronicos 2019Documento10 páginasCircuitos Electronicos 2019Carlos Angel Bartra VillanuevaAún no hay calificaciones

- TareaDocumento13 páginasTareaDouglas Daniel Pincay QuimiAún no hay calificaciones

- Diseño de Un Amplificador de Pequeña Señal Con Transistor BJT PDFDocumento10 páginasDiseño de Un Amplificador de Pequeña Señal Con Transistor BJT PDFJorge L. Merchán100% (1)

- Banco de Preguntas - Electrónica Analógica Iii - 2do - Parcial - EstudiantesDocumento3 páginasBanco de Preguntas - Electrónica Analógica Iii - 2do - Parcial - Estudiantesfer poloAún no hay calificaciones

- Segundo Lab 2019 C V3ADocumento3 páginasSegundo Lab 2019 C V3ACRISTIAN ANDRES TOBAR ECHEVERRYAún no hay calificaciones

- Ejercicios Propuestos - Tercer Parcial PDFDocumento5 páginasEjercicios Propuestos - Tercer Parcial PDFAbdielJimenezAlarconAún no hay calificaciones

- Ejercicios Propuestos - Tercer Parcial PDFDocumento5 páginasEjercicios Propuestos - Tercer Parcial PDFJosue VivasAún no hay calificaciones

- 100 Circuitos de Potencia con SCRs y TriacsDe Everand100 Circuitos de Potencia con SCRs y TriacsCalificación: 3 de 5 estrellas3/5 (5)

- 100 circuitos de shields para arduino (español)De Everand100 circuitos de shields para arduino (español)Calificación: 3.5 de 5 estrellas3.5/5 (3)

- 04 - Sintesis de Circuitos Combinacionales - UNLaM - v3pptDocumento53 páginas04 - Sintesis de Circuitos Combinacionales - UNLaM - v3pptLeo PereiraAún no hay calificaciones

- 05 - Familias Logicas - UNLaM - v5pptDocumento72 páginas05 - Familias Logicas - UNLaM - v5pptLeo PereiraAún no hay calificaciones

- 03 - Algebra de Boole - UNLaM - v4pptDocumento39 páginas03 - Algebra de Boole - UNLaM - v4pptLeo PereiraAún no hay calificaciones

- 02 - Codigos - UNLaM - v3pptDocumento63 páginas02 - Codigos - UNLaM - v3pptLeo PereiraAún no hay calificaciones

- 2023 TP1 - Sistemas de NumeracionDocumento5 páginas2023 TP1 - Sistemas de NumeracionLeo PereiraAún no hay calificaciones

- 2023 TP4 - Circuitos CombinacionalesDocumento6 páginas2023 TP4 - Circuitos CombinacionalesLeo PereiraAún no hay calificaciones

- 2023 TP3 - Algebra de BooleDocumento7 páginas2023 TP3 - Algebra de BooleLeo PereiraAún no hay calificaciones

- 2023 TP2 - CodigosDocumento5 páginas2023 TP2 - CodigosLeo PereiraAún no hay calificaciones

- Informe Practica 3 SD Gerardo RodriguesDocumento26 páginasInforme Practica 3 SD Gerardo RodriguesGerardo Rodrigues FlammiaAún no hay calificaciones

- Circuitos TTL Electra Nica Teora A y Pra CticaDocumento72 páginasCircuitos TTL Electra Nica Teora A y Pra Cticapoetaenator100% (1)

- CUESTIONARIO PREVIO N°5 (QUINTANA, JOHN)Documento16 páginasCUESTIONARIO PREVIO N°5 (QUINTANA, JOHN)John QuintanaAún no hay calificaciones

- LAIT302 - U4 - EA - Apellido Paterno - NombreDocumento7 páginasLAIT302 - U4 - EA - Apellido Paterno - NombreHugo Alberto Ortiz AnayaAún no hay calificaciones

- UNEFA S2-2013 TLC 32125 Familias Logicas by Dayyanet DiazDocumento9 páginasUNEFA S2-2013 TLC 32125 Familias Logicas by Dayyanet DiazdayyanetAún no hay calificaciones

- Practica 2 DigitalDocumento5 páginasPractica 2 DigitalEddu BPAún no hay calificaciones

- Informe Final de Laboratorio #1Documento16 páginasInforme Final de Laboratorio #1Carlos Ernesto Flores AlbinoAún no hay calificaciones

- Cuestionario 2Documento9 páginasCuestionario 2Cristian GuanoquizaAún no hay calificaciones

- Chip Nuevo 2021Documento10 páginasChip Nuevo 2021edwin mendozaAún no hay calificaciones

- AmplificadorDocumento4 páginasAmplificadorjose esquiviaAún no hay calificaciones

- Memoria RAMDocumento2 páginasMemoria RAMfer bautistaAún no hay calificaciones

- RESUMEN Lectura 1 - Introducción Al Funcionamiento de Un MicroordenadorDocumento17 páginasRESUMEN Lectura 1 - Introducción Al Funcionamiento de Un MicroordenadorArielAún no hay calificaciones

- Circuitos CombinacionalesDocumento15 páginasCircuitos CombinacionalesAiram PeñaAún no hay calificaciones

- Tic TrabajoDocumento6 páginasTic TrabajosabelaAún no hay calificaciones

- Chipset ArquitecturaDocumento14 páginasChipset ArquitecturaJuan UmbertoAún no hay calificaciones

- Memoria EstaticaDocumento14 páginasMemoria EstaticaPAPOFULEAún no hay calificaciones

- Microcontrolador PIC16F84Documento7 páginasMicrocontrolador PIC16F84Ezequiel VelasquezAún no hay calificaciones

- Prácticas Digital Croclip 1Documento6 páginasPrácticas Digital Croclip 1David Alegre ExpósitoAún no hay calificaciones

- Microprocesadores CuestionarioDocumento11 páginasMicroprocesadores CuestionarioGastón GallegosAún no hay calificaciones

- Diapositiva #6 - Flip-FlopsDocumento11 páginasDiapositiva #6 - Flip-FlopsRoger PrzAún no hay calificaciones

- Club Saber Electrónica - Electrónica DigitalDocumento84 páginasClub Saber Electrónica - Electrónica DigitalSwami Salas Rosado100% (1)

- Miguel Velasquez Guzman 8 A JUAN XXIIIDocumento2 páginasMiguel Velasquez Guzman 8 A JUAN XXIIIJOHN ALVAREZAún no hay calificaciones

- Clases UNIDAD 01 Micros - 23 - IIDocumento28 páginasClases UNIDAD 01 Micros - 23 - IIAlan Mendoza AlvarezAún no hay calificaciones

- Instruciones Microcontroladores Avr en Español)Documento36 páginasInstruciones Microcontroladores Avr en Español)Javier Sanchez Mojica100% (13)

- Sesión 01Documento21 páginasSesión 01Jhonatan Tesèn SanchezAún no hay calificaciones

- Jerarquía de MemoriaDocumento45 páginasJerarquía de MemoriaJose MartinezAún no hay calificaciones

- Layout de Transistores MosDocumento15 páginasLayout de Transistores MosLio TizAún no hay calificaciones

- Circuito de Tres Estados Buffer 74173Documento5 páginasCircuito de Tres Estados Buffer 74173Henry PurunAún no hay calificaciones

- Sist-Digitales Lab 1 (Unac)Documento5 páginasSist-Digitales Lab 1 (Unac)Carlos MonsalveAún no hay calificaciones

- Capítulo 3: Superescalares: 1 (Ejercicios de Clase)Documento58 páginasCapítulo 3: Superescalares: 1 (Ejercicios de Clase)Adrian OrielAún no hay calificaciones