Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Estudio de Flip Flop

Cargado por

argie27Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Estudio de Flip Flop

Cargado por

argie27Copyright:

Formatos disponibles

2011

Laboratorio de electrnica digital

Grupo 2

LOGICA SECUENCIAL Estudio dE flip flop

24/06/2011

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

MANTENIMIENTO ELECTRONICO E INSTRUMENTACION INDUSTRIAL (110291)

LABORATORIO DE ELECTRONICA DIGITAL

ESTUDIO DE FLIP FLOP

INTEGRANTES: ARMANDO ESTRADA GONZALEZ MARLON MEJIA GONZALEZ FREDDY BARRERA REINALDO RIVERA ELVIS AVILA AVILA CATHY LEE GRAU MARTHA SUAREZ PROFESOR: EFRAIN

SENA

CENTRO PARA LA INDUSTRIA PETROQUIMICA

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

MARCO TEORICO CIRCUITOS SECUENCIALES Un sistema secuencial se caracteriza por que las variables de salida (unos o ceros Lgicos), en un determinado instante, dependen de la variables de entrada (unos o ceros) en ese instante y del valor que en el instante anterior tuvieran las propias variables de salida. Son sistemas capaces de memorizar cierta informacin de lo sucedido con anterioridad en un determinado momento, y utilizar esta informacin, con juntamente con una combinacin lgica de sus entradas, para determinar el futuro estado del sistema considerado.

Un sistema secuencial est compuesto de dos partes bien diferenciadas: - Una parte de almacenamiento de informacin. - Una red combinacional que va a generar las rdenes de control del sistema. Los trminos y nomenclatura propia de los sistemas secuenciales son: - Qt: valor de la salida en un instante de tiempo (t). - Qt-1: valor de la salida en un instante de tiempo anterior (t-1). - Xt: valor de la entrada X en un instante de tiempo (t). - Yt: valor de la entrada Y en un instante de tiempo (t). Dentro de los circuitos secuenciales se pueden encontrar dos tipos: Sistemas secuenciales asncronos y sistemas secuenciales sncronos. Los sistemas secuenciales asncronos poseen la caracterstica de que los cambios en las seales de salida se producen en el mismo instante en que se modifican las seales de entrada.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

En los sistemas secuenciales sncronos es necesaria la existencia de una seal particular, llamada de sincronismo, para que las variables de entrada modifiquen las seales de salida. BIESTABLES: Los biestables son circuitos combinacionales capaces de conservar indefinidamente su salida en uno de los dos estados lgicos mientras no exista una orden de cambio. La orden de cambio o de disparo es generada por el sistema combinacional de control. Esta caracterstica de retencin de la seal de salida, hace que el biestable sea la clula elemental en la formacin de memorias. Los biestables se agrupan en varios bloques dependiendo de factores tales como: - Tipos de entradas. - Tipo de seal de sincronismo. Una seal de sincronismo es una seal de onda Cuadrada que marca la pauta temporal de sincronizacin del sistema secuencial. Dependiendo de la seal de entrada los tipos de biestable son: - Biestable R -S. - Biestable J - K. - Biestable D. - Biestable T. Dependiendo de la seal de sincronismo los tipos de biestables son: - Asncronos: Son aquellos biestables que no disponen de seal de sincronismo o de reloj. Los tipos de biestables asncronos son: - Biestable asncrono R - S. - Biestable asncrono J - K. - Biestable asncrono D. - Biestable asncrono T. - Sncronos: Son biestables que tienen seal de sincronismo o de reloj. Esta seal va a sincronizar los cambios en la seal de salida. Dependiendo del tipo de seal de sincronismo de que disponga el biestable existen las siguientes clases de biestables sncronos: - Activados por nivel: - Activados por flanco en la seal de sincronismo - Activados por nivel El cambio de nivel lgico en la seal de sincronismo habilita a la seal de entrada para que cambie la seal de salida. Por ejemplo, un biestable sncrono activado por nivel lgico (cero lgico o uno lgico) cambia la seal de salida en el instante en que la seal de sincronismo pasa de valer cero a valer uno lgico, o viceversa. Biestables sncronos activados por nivel son: LOGICA SECUENCIAL Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

- Biestable sncrono activo por nivel R - S. - Biestable sncrono activo por nivel J - K. - Biestable sncrono activo por nivel D. - Biestable sncrono activo por nivel T. - Activados por flanco en la seal de sincronismo: El flanco de cualquier seal es la zona de seal que est situada en la transicin de un nivel lgico a otro.

Si el cambio se produce de nivel alto (uno lgico) a nivel bajo (cero lgico), el flanco es denominado de bajada. Si por el contrario el cambio se produce de nivel bajo a nivel alto, el flanco es denominado de subida. Biestables activados por flanco son: - Biestable activado por flanco J - K. - Biestable activado por flanco R - S - Biestable activado por flanco D. - Biestable activado por flanco T. Los biestables ms usados en electrnica suelen ser todos aquellos que disponen de seal de sincronismo o de reloj. Los biestables sncronos, que disponen de seal de sincronismo, van a ser tratados con ms profundidad en el presente captulo. BIESTABLES SINCRONOS: Se caracterizan porque slo se permiten cambios en la salida cuando la seal de sincronismo est al nivel correcto (activo por nivel), o en el flanco adecuado (activo por flanco) y se denominan biestables sncronos porque funcionan bajo modo sncrono, es decir, bajo un seal de sincronismo. El modo de funcionamiento sncrono tiene dos importantes ventajas sobre el funcionamiento bajo modo asncrono las cuales son: - Permite que los cambios en el sistema se realicen slo cuando se tenga la seguridad de que las diferentes seales que actan sobre l estn presentes. LOGICA SECUENCIAL Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

- El ruido electrnico, o las seales que provocan interferencias, solamente tienen la posibilidad de actuar en los tiempos marcados por la seal de sincronismo. Las partes de que se compone un biestable sncrono son las siguientes:

- Preset: seal de puesta a 1. Si en el terminal preset tenemos un nivel alto (1 lgico), la salida Q pasa a valer nivel alto. - Clear: seal de puesta a 0. Si en el terminal clear tenemos un nivel alto (1 lgico), la salida Q pasa a valer nivel bajo. - Clk: seal de sincronismo o de reloj. Es la que marca los tiempos de cambio en la seal de salida. - Entradas X Y: son las entradas lgicas del circuito secuencial. - Salida Q: seal resultante o de salida del circuito secuencial. - Salida Q : seal de salida negada (si Q = 1 entonces Q = 0). En el caso de que las seales de PRESET y CLEAR estn al mismo tiempo a nivel alto, no actuar ninguna de las dos seales. Dentro de los biestables sncronos existen bsicamente tres tipos o clases, segn su modo de disparo o de sincronizacin que son: - Modo Nivel: un cambio en la salida de estos biestables slo est permitido mientras la entrada de reloj permanezca en un determinado nivel (bajo o alto), dependiendo del biestable de que se trate. En este modo el biestable se llama Latch. - Modo Balanza o Toggle: los datos de la entrada se toman en el flanco de subida de la seal de reloj y se hacen efectivos en la salida en el flanco de bajada de la seal. En este modo el biestable es denominado Flip-Flop. - Modo Edge o Flanco: los datos de entrada se toman en un determinado flanco y su presentacin en la salida se efecta en el mismo flanco. En este modo tambin se denomina al biestable Flip-Flop.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

BIESTABLE D ACTIVO POR NIVEL (LATCH) Un latch es un biestable que funciona con una seal de sincronizacin activa por nivel.

Este biestable dispone de: - Seal de sincronizacin (E): es la que marca, al nivel adecuado, cundo se pueden permitir cambios en la salida. - Seal de entrada (D): es el dato de entrada y puede ser o 1 o 0 lgicos. - Seal de salida (Q): es el dato de salida y puede ser 1 o 0 lgicos. - Seal de salida inversa (Q): es el valor lgico inverso de la salida Q. - Seal de preset (PRE): seal asncrona que cuando est a nivel alto pone la salida Q a nivel alto, independientemente de cmo est la entrada D. - Seal de clear (CLR): seal asncrona que cuando est a nivel alto pone la salida Q a nivel bajo, independientemente de cmo est la entrada D. Todos los biestables tienen una tabla de funcionamiento (tabla de verdad) que relaciona las distintas seales de entrada y control, con la salida Q. La tabla de verdad de un biestable D es la siguiente:

Estas tablas se leen por filas de arriba a abajo y dentro de cada fila se lee de izquierda a derecha. Por ejemplo, la primera fila de esta tabla quiere decir que independientemente del estado de la entrada D (smbolo X), cuando la seal de sincronizacin E vale cero lgico, la salida Q es la misma que en el instante anterior (Qt-1). LOGICA SECUENCIAL Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

Cuando la entrada de sincronismo E est a nivel alto, la salida Q seguir en todo momento los valores de la entrada. Cuando E est a nivel bajo la salida Q es la misma que en el instante anterior, es decir, es Qt-1. Las seales de control tienen prioridad sobre el resto de las seales del circuito. Si la seal de CLEAR est a nivel alto, la salida ser cero independientemente del resto de las seales.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

BIESTABLE SINCRONO J-K ACTIVO POR FLANCO ( M/S) El biestable J-K sncrono activo por flanco es un biestable que tiene dos entradas de datos, denominadas J y K, y tiene una seal de sincronismo (onda cuadrada) que permite cambios en la salida cuando existan flanco (subida o bajada dependiendo del biestable) en ella.

La descripcin de cada patilla o terminal del biestable es la siguiente: - Seal de sincronizacin (CLK): en este terminal acta la seal de reloj (onda cuadrada), cuyos flancos marcan la zona donde puede haber cambios en la salida Q. - Seales de entrada (J y K): la combinacin de 0 y 1 en estos dos terminales determina el valor lgico de la salida. - Seal de salida (Q): esta seal es la salida del dato que puede ser 0 1 lgicos. - Seal de salida inversa (Q): es el valor lgico inverso a la salida Q. - Seal de preset (PRS): seal asncrona que cuando esta a nivel alto pone la salida Q a nivel alto independientemente de cmo estn las entradas J y K. - Seal de clear (CLR): seal asncrona que cuando est a nivel alto pone la salida Q a nivel bajo independientemente de cmo estn las entradas J y K.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

En este laboratorio de electrnica digital, conoceremos ms a fondo la estructura y funcionamiento de los flip flop; RS, JK, D y T. con el uso de compuertas ANDOR-NOR. Para esta prctica se obtuvieron con anterioridad los implementos ya previamente listados en el laboratorio, por lo cual en el grupo de trabajo se formulo el mtodo para resolver la actividad para luego realizar la conclusin de que se aprendi de todo esta nueva practica de laboratorio. Con la ayuda de la red, se consultara temas que no se han tenido claro y que aun no se conocen y el programa ISIS o (proteus) se simularan todos los circuitos con cada una de las compuertas para verificar por medio de este si la practica en Protoboards con todos los implementos estar funcionando como se simulara y en caso de no ser as se consultara con otras fuentes y se ratificara si esta correcto.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

INTRODUCCION Desde muchas pocas pasadas el hombre ha jugado y maniobrado con la energa a su mximo favor, con tal de sacarle el mayor provecho y aplicacin a muchos campos de la ciencia, uno de esas grandes aplicaciones es direccionado a todas las ramas de la electrnica. Y en este caso especifico a la digital en el uso de compuertas para disear circuitos secuenciales flip flop con capacidad de memoria. Este circuito secuencial es una de las partes de muchos circuitos que estn incorporados a grandes prototipos. El principal ingrediente para que este circuito funcione es una seal cuadrtica o pulso de energa con flancos negativos y positivos que varan en el tiempo o el retardo natural asociados al trabajo de las compuertas lgicas en una implementacin. Para la realizacin de este laboratorio lo ms importante que se debe destacar es la comprensin de cada tipo de flip flop, su implementacin y la onda o seal de salida que genera cada circuito secuencial.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

SOLUCION DE LABORATORIO.

1. DIAGRAMA DE ESTADOS DE LOS FLIP PLOP:

FLIP FLOP (SR);

Q=1

-Q=0

S 0 1

R 0 0 S 0 1 R

S 0 0 0 1

FLIP FLOP (JK); J K 1 1 0 1

Q=1

-Q=0

J K J K 0 1 1 0 0 1 J K 0 1 1 LOGICA SECUENCIAL 1 0 0 1 0 1 1

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

D FLIP FLPOP (D); 1

Q=1

-Q=0

D 1 D 0

D 0

FLIP FLOP (T); T 1 0 0 1

Q=1

-Q=0

T 0 1 1 T 1 0

T 1

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

OBJETIVOS

Obtener

las tablas de verdad de los Flip Flop: RS, D, JK y T. las diferencias entre un Flip-Flop y un latch de tipo D. Observar el efecto del reloj en los Flip Flop temporizados y la sincrona de entrada salidas.

Identificar

Componentes del laboratorio

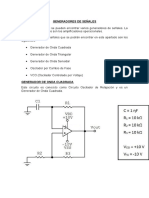

ACTIVIDADES PREVIAS Realice los diagramas de estados de los flip flops tipo RS, JK, D y T. Investigar los diagramas esquemticos de los CIs utilizados en estas prcticas, as como sus tablas de verdad. Para la segunda parte, traer implementado con el CI 7476, el circuito generador de combinaciones de la figura 1.

Figura 1.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

DESARROLLO DE LA PRCTICA. PRIMERA PARTE: Celdas bsicas con compuertas Celda bsica RS Implemente el circuito de la figura. Colocando LEDS a las salidas, polarizados mediante resistencias de 220 .

Obtenga la tabla de verdad caracterstica y anote los resultados en la tabla NOTA: Verifique siempre las condiciones iniciales.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

Qt 0 0 0 0 1 1 1 1

R 0 0 1 1 0 0 1 1

S 0 1 0 1 0 1 0 1

Qt+1 0 1 0 x 1 1 0 x

Qt+1 1 0 1 x 0 0 1 x

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

Celda bsica RS temporizada

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

Modifique el circuito anterior para obtener el circuito de la figura.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

Qt 0 0 0 0 1 1 1 1 e

Obtenga la tabla de verdad, para este circuito. Simule el pulso de reloj con el interruptor CLK. Anote los resultados en la tabla. Compare las dos tablas: Cul es la diferencia? Concluya. CLK = 0 CLK = 1 R S Qt+1 Qt+1 Qt+1 Qt+1 Estado anterior Estado anterior 0 1 0 0 Estado anterior Estado anterior 1 0 0 1 Estado anterior Estado anterior 0 1 1 0 Estado anterior Estado anterior * * 1 1 Estado anterior Estado anterior 1 0 0 0 Estado anterior Estado anterior 1 0 0 1 Estado anterior Estado anterior 0 1 1 0 Estado anterior Estado anterior * na 1 1

CONCLUSION; Pude observar que cuando la seal de reloj (CLK) LA ponemos en un estado lgico bajo (0) la tabla siempre me va a mostrar la salida anterior. Si el resultado anterior fue (1) y pongo la seal clk en bajo, no importa que combinacin realice en sus entradas la tabla siempre me va a mostrar (1) en este caso. FlipFlop D activado por nivel (latch) Modifique el circuito anterior para obtener el latch tipo D de la figura. Conecte sus entradas como se indica y coloque LEDS a las salidas, polarizados mediante resistencias de 220 .

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

Obtenga la tabla de verdad caracterstica, teniendo cuidado de establecer en el circuito las condiciones iniciales correctas. Anote los resultados en la tabla. CLK 0 0 0 0 1 1 1 1 Qt 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 Qt+1 Estado anterior Estado anterior Estado anterior Estado anterior 0 1 0 1 Qt+1 Estado anterior Estado anterior Estado anterior Estado anterior 1 0 1 0

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

Invierta las entradas D y CLK y repita el paso 6. Analice y concluya.

CLK 0 0 0 0 1 1 1 1 Qt 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 Qt+1 Estado anterior Estado anterior Estado anterior Estado anterior 1 1 1 1 Qt+1 Estado anterior Estado anterior Estado anterior Estado anterior 0 0 0 0

Conclusin: Observando las tablas y realizando el cambio de CLK con D, se concluye que cuando el valor de Q=1 y cuando D=0, permanece el estado anterior=1; y si Q=0 y D=0 permanece en el estado anterior =0. Dando como conclusin que siempre que la seal de reloj o CLK en ste caso D se hace igual a cero (D=0), muestra el Estado Anterior explicado en el primer ejercicio de conclusin. La conclusin que se pudo obtener al momento de invertir las entradas de CLK y D, fue que el estado de memoria y el estado siguiente Qn+1 era la respuesta contraria al momento de invertir las entradas.

SEGUNDA PARTE: Circuitos integrados Flip-Flops y latchs. Latch D y Flip-Flop D

Los conceptos de latch y Flip-Flop a veces son tomados (errneamente) como sinnimos. La principal diferencia radica en que un latch responde al nivel (ya sea alto o bajo) de una seal de reloj, mientras que un Flip-Flop solo lo hace nicamente en las transiciones (ascendentes o descendentes). 8. Con los CIs 74LS74 y 74LS75, implemente el circuito mostrado en la figura, verificando que las seales asncronas se conectan correctamente.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

9. Aplique con el generador una seal TTL de 10 KHz y con la ayuda del osciloscopio, elabore el diagrama de tiempo que contenga las salidas del generador (entradas D, E y CLK) y las salidas Qs del latch y del Flip-Flop. Dibjelas en hojas cuadriculadas.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

Flip-Flop JK 10. Con el CI 7476 implemente el FlipFlop tipo JK mostrado en la figura . Conecte las entradas clear y preset en estado alto.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

11. Con ayuda del osciloscopio, realice un diagramas de tiempo con CLK, J, y Q; dibuje en papel cuadriculado. NOTA: Recuerde verificar en estos circuitos, la presencia de los flancos y no el pulso.

12. Intercambie las entradas J y K realice un nuevo diagrama de tiempos. Analice y Concluya.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

Conclusin; Que la seal de salida no solo depende de la seal clk o (pulso de reloj) FlipFlop Tipo T 13. Interconecte las dos entradas J y K del circuito de las figura anterior, para convertirlo en un FlipFlop tipo T, y conecte esta entrada a la salida B del generador de combinaciones.

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

14. Con el nuevo circuito, obtenga el diagrama de tiempos.

15. Invierta las entradas T y CLK y obtenga un nuevo diagrama de tiempo. Analice y Concluya

LOGICA SECUENCIAL

Estudio de flip flop

LABORATORIO DE ELECTRONICA DIGITAL

24 de junio de 2011

LOGICA SECUENCIAL

Estudio de flip flop

También podría gustarte

- Circuitos Logicos Flip-FlopDocumento47 páginasCircuitos Logicos Flip-FlopFreddy's Beltran OficialFb100% (1)

- Flip FlopsDocumento14 páginasFlip FlopsPaqco Suarex100% (1)

- Timer 555Documento8 páginasTimer 555JhodiskiLGAún no hay calificaciones

- Bus de Campo en Comunicacion IndustrialDocumento11 páginasBus de Campo en Comunicacion Industrialanon_9714Aún no hay calificaciones

- Flip FlopDocumento70 páginasFlip FlopCarlosLPAún no hay calificaciones

- Aplicaciones Flip FlopDocumento6 páginasAplicaciones Flip FlopRosa Sinchí50% (6)

- 10 BiestablesDocumento45 páginas10 BiestablesFERMINAún no hay calificaciones

- Puertos de Entrada y SalidaDocumento55 páginasPuertos de Entrada y SalidaJuanfer PCAún no hay calificaciones

- Control DC Basado en Matlab PDFDocumento16 páginasControl DC Basado en Matlab PDFNoe Muñoz QuitoAún no hay calificaciones

- Fuentes ConmutadasDocumento16 páginasFuentes ConmutadasJavierAún no hay calificaciones

- Manejo de LCD 16x2Documento12 páginasManejo de LCD 16x2Diego Segoviano GarciaAún no hay calificaciones

- LatchesDocumento9 páginasLatchesFabio LópezAún no hay calificaciones

- Detector de Fugas en Capacitores ElectroliticosDocumento14 páginasDetector de Fugas en Capacitores ElectroliticosEfrain ConriquezAún no hay calificaciones

- Curso MikrobasicDocumento9 páginasCurso MikrobasicEdson RodasAún no hay calificaciones

- Microcontroladores PIC18F4550.Documento15 páginasMicrocontroladores PIC18F4550.Gabriel Acevedo lopezAún no hay calificaciones

- Temporizador 555Documento30 páginasTemporizador 555AlejandroGallardoAún no hay calificaciones

- Diseño Digital SemáforoDocumento3 páginasDiseño Digital SemáforomariadignoraAún no hay calificaciones

- Circuito Monoestable Con 555Documento5 páginasCircuito Monoestable Con 555Mario PellegrinoAún no hay calificaciones

- Analizador Logico 2019-LivianoDocumento97 páginasAnalizador Logico 2019-LivianoVictor Santana GomezAún no hay calificaciones

- Reporte Practica Flip FlopsDocumento18 páginasReporte Practica Flip FlopsChamín AlcántaraAún no hay calificaciones

- Comunicación Serial Con PICDocumento15 páginasComunicación Serial Con PICjbrunobAún no hay calificaciones

- Labview PracticasDocumento37 páginasLabview PracticasManuel ForvAún no hay calificaciones

- Contador de Dos (2) DigitosDocumento9 páginasContador de Dos (2) DigitosPAPOFULEAún no hay calificaciones

- Luces Secuenciales Reversibles Con 16 LedsDocumento9 páginasLuces Secuenciales Reversibles Con 16 LedsRuben Hernandez100% (1)

- Flip FlopDocumento9 páginasFlip FlopCarlosAndresMirandaHernandesAún no hay calificaciones

- Generadores de SeñalesDocumento21 páginasGeneradores de SeñalesStefany LizethAún no hay calificaciones

- Multiplexores, Demultiplexores, Sumadores y RestadoresDocumento5 páginasMultiplexores, Demultiplexores, Sumadores y RestadoresDaniel Quesada Bejarano100% (1)

- Análisis de La Respuesta Transitoria y EstacionariaDocumento27 páginasAnálisis de La Respuesta Transitoria y EstacionariaAlfredo Gil Velasco100% (1)

- Clase 7 Digitales Circuitos SecuencialesDocumento41 páginasClase 7 Digitales Circuitos SecuencialesgermanAún no hay calificaciones

- 2.inversion de GiroDocumento6 páginas2.inversion de GiroJoseph Romero VelizAún no hay calificaciones

- Microcontrolador McuDocumento4 páginasMicrocontrolador McunelsdainAún no hay calificaciones

- Estructura Interna de Un PLCDocumento10 páginasEstructura Interna de Un PLCRoblero LopezAún no hay calificaciones

- Electronica Digital - 6a - Contador - Ascendente-Descendente PDFDocumento22 páginasElectronica Digital - 6a - Contador - Ascendente-Descendente PDFCarlos HernandezAún no hay calificaciones

- Aprender Facil, MicrocontroladoresDocumento71 páginasAprender Facil, MicrocontroladoresRanghel SotoAún no hay calificaciones

- ATMega 328 PDocumento20 páginasATMega 328 PRoman ClarkAún no hay calificaciones

- Varios CircuitosDocumento30 páginasVarios CircuitosteoarevaloAún no hay calificaciones

- Práctica 8 Latches y Flip FlopsDocumento4 páginasPráctica 8 Latches y Flip FlopsRay GzzAún no hay calificaciones

- Componentes ElectronicosDocumento12 páginasComponentes ElectronicosSebastianAún no hay calificaciones

- ComparadoresDocumento3 páginasComparadoresSERGIO ALEJANDRO BOLANOS RAMIREZAún no hay calificaciones

- Manual de Practicas ATMega 8535Documento61 páginasManual de Practicas ATMega 8535JUAN DIAZ MAMANIAún no hay calificaciones

- MosfetDocumento8 páginasMosfetCarmen Perez MendozaAún no hay calificaciones

- Sensores Capacitivos e InductivosDocumento8 páginasSensores Capacitivos e InductivosRockerBassMan16Aún no hay calificaciones

- El Generador de SeñalesDocumento9 páginasEl Generador de SeñalesZacarias Mellado AyalaAún no hay calificaciones

- Lab - Flip FlopDocumento7 páginasLab - Flip Flopomar0sandoval0timanaAún no hay calificaciones

- Diseño e Implementación de Un Convertidor DC-DC Tipo Buck en Lazo AbiertoDocumento8 páginasDiseño e Implementación de Un Convertidor DC-DC Tipo Buck en Lazo Abiertohhryc7Aún no hay calificaciones

- FlipflopsDocumento32 páginasFlipflopsCarlosRuizAún no hay calificaciones

- LABORATORIO Eo No7 Contador 2016Documento10 páginasLABORATORIO Eo No7 Contador 2016Darren DurandAún no hay calificaciones

- Informe Dado ElectronicoDocumento3 páginasInforme Dado ElectronicoPaul Romero RieraAún no hay calificaciones

- Hoja Ejercicios 2 - Rele Zelio 2Documento6 páginasHoja Ejercicios 2 - Rele Zelio 2Marcelo Adrian Quintana GutierrezAún no hay calificaciones

- Lab.1 Circuitos Resistivos Serie ParaleloDocumento13 páginasLab.1 Circuitos Resistivos Serie ParalelomatematicafimeAún no hay calificaciones

- Manual PIC16F84Documento21 páginasManual PIC16F84Michael Lopez100% (1)

- Modulo de TemperaturaDocumento120 páginasModulo de TemperaturaluisAún no hay calificaciones

- Sensor Óptico CNY70Documento19 páginasSensor Óptico CNY70Juan GuevaraAún no hay calificaciones

- Detector de Cruce Por Cero Con Amplificador OperacionalDocumento5 páginasDetector de Cruce Por Cero Con Amplificador OperacionalIsmael SuarezAún no hay calificaciones

- Investigación Temario - Tema 1 MicrocontroladoresDocumento21 páginasInvestigación Temario - Tema 1 MicrocontroladoresDaniel GomezAún no hay calificaciones

- Puertas LogicasDocumento18 páginasPuertas LogicasBadass OverPowerAún no hay calificaciones

- Compuertas LogicasDocumento7 páginasCompuertas LogicasJordanPozoAún no hay calificaciones

- Circuitos Combinacionales y SecuancialesDocumento39 páginasCircuitos Combinacionales y SecuancialesJosé Miguel AvalosAún no hay calificaciones

- Basculas Sincronas y AsincronasDocumento11 páginasBasculas Sincronas y Asincronastitominas7511Aún no hay calificaciones

- Filtro adaptativo: Mejora de la visión por computadora mediante filtrado adaptativoDe EverandFiltro adaptativo: Mejora de la visión por computadora mediante filtrado adaptativoAún no hay calificaciones

- Data Sheet CD 4029Documento4 páginasData Sheet CD 4029AndyGarciaAún no hay calificaciones

- Practicas Circuitos DIgitales-Luis UrdanetaDocumento102 páginasPracticas Circuitos DIgitales-Luis UrdanetaLuis D. Urdaneta G.100% (3)

- Practica 3Documento7 páginasPractica 3Joss JossrAún no hay calificaciones

- Maquinas MooreDocumento35 páginasMaquinas MooreDaniel GuerraAún no hay calificaciones

- Modulo Tecnologico Ci 555Documento6 páginasModulo Tecnologico Ci 555Ronald CruzAún no hay calificaciones

- Memoria Estatica y DinamicaDocumento6 páginasMemoria Estatica y DinamicaDiego FrancisAún no hay calificaciones

- Informe Final 7 Analisis Sistemas SecuencialesDocumento7 páginasInforme Final 7 Analisis Sistemas SecuencialesMigvel Angel Soncco XDAún no hay calificaciones

- Práctica N° 1 SD2Documento7 páginasPráctica N° 1 SD2alva_jraAún no hay calificaciones

- Registros FinalDocumento8 páginasRegistros Finalceleste claroAún no hay calificaciones

- TEMPORIZADOR 555 Analogica 2Documento5 páginasTEMPORIZADOR 555 Analogica 2Saiid Hdez CAún no hay calificaciones

- Circuitos Lógicos Práctica 4 Flip FlopsDocumento8 páginasCircuitos Lógicos Práctica 4 Flip FlopsAlejandro StaveleyAún no hay calificaciones

- Practica 8Documento37 páginasPractica 8Renato Beltran CaceresAún no hay calificaciones

- Laboratorio N3Documento21 páginasLaboratorio N3Erik Samanez GalianoAún no hay calificaciones

- Flip Flop Tipo DDocumento4 páginasFlip Flop Tipo DJorge Quechol Montalvo100% (1)

- Proyecto CafeteraDocumento10 páginasProyecto Cafeteraeliseo rodea100% (2)

- Evaluacion Sumativa II Lab. Redes Electricas, Practica N°1 y N°2 Franko ManganielloDocumento20 páginasEvaluacion Sumativa II Lab. Redes Electricas, Practica N°1 y N°2 Franko ManganielloIsaac MonterreyAún no hay calificaciones

- LAB8Documento6 páginasLAB8Sarah CahuanaAún no hay calificaciones

- EL Latch y El Flip-FlopDocumento24 páginasEL Latch y El Flip-Flopjosesito92Aún no hay calificaciones

- Lenguaje BDFDocumento8 páginasLenguaje BDFroyercahuiAún no hay calificaciones

- Inf 4 Flip FlopDocumento8 páginasInf 4 Flip FlopEmilio Daniel Villalba LozanoAún no hay calificaciones

- SISTEMAS-DIGITALES - TEMA 7 - Circuitos - Secuenciales - BásicosDocumento24 páginasSISTEMAS-DIGITALES - TEMA 7 - Circuitos - Secuenciales - BásicosPabloAún no hay calificaciones

- Tipos de DiodosDocumento12 páginasTipos de DiodosAlex Sandoval Prado100% (1)

- Capitulo - I Biestables RSDocumento8 páginasCapitulo - I Biestables RSAlejandro AguirreAún no hay calificaciones

- CLASE VIRTUAL 5 de ELECTRÓNICA DIGITALDocumento33 páginasCLASE VIRTUAL 5 de ELECTRÓNICA DIGITALjhon caceres100% (1)

- 14-Registros y ContadoresDocumento12 páginas14-Registros y Contadoreswemy92Aún no hay calificaciones

- Ejercicios para ResolverDocumento10 páginasEjercicios para ResolverKevin ContrerasAún no hay calificaciones

- Anteproyecto de La Ruleta DigitalDocumento11 páginasAnteproyecto de La Ruleta DigitalmartinAún no hay calificaciones

- Circuito Secuencial Sincrono Puerta AutomaticaDocumento7 páginasCircuito Secuencial Sincrono Puerta Automaticajunmech100% (2)

- Digitales2 Lab 1Documento5 páginasDigitales2 Lab 1Erick VillanuevaAún no hay calificaciones

- Lab10 Dispos Mendoza Rosales C15 4 CDocumento11 páginasLab10 Dispos Mendoza Rosales C15 4 CJairo Hans Cardenas MauricioAún no hay calificaciones