0% encontró este documento útil (0 votos)

583 vistas10 páginasEjercicios para Resolver

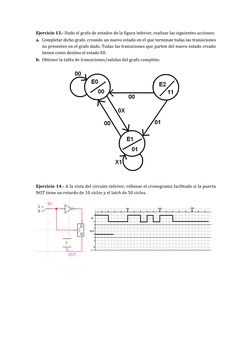

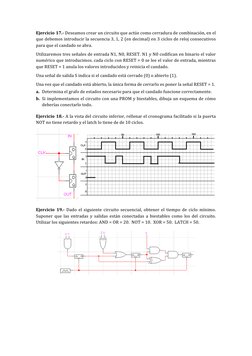

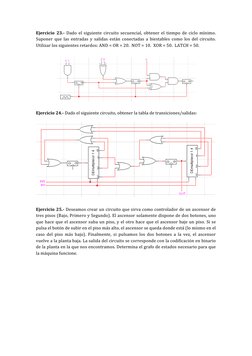

Este documento presenta 7 ejercicios sobre circuitos lógicos secuenciales. El primer ejercicio explica que las puertas añadidas a la entrada de un latch D tienen como objetivo completar el latch D a partir de un latch SR más simple. El segundo ejercicio pide completar un cronograma de salida para dos flip-flops conectados en serie. Y el tercer ejercicio contiene preguntas sobre tipos de circuitos secuenciales y cálculos de tiempos de ciclo.

Cargado por

Kevin ContrerasDerechos de autor

© © All Rights Reserved

Nos tomamos en serio los derechos de los contenidos. Si sospechas que se trata de tu contenido, reclámalo aquí.

Formatos disponibles

Descarga como PDF, TXT o lee en línea desde Scribd

0% encontró este documento útil (0 votos)

583 vistas10 páginasEjercicios para Resolver

Este documento presenta 7 ejercicios sobre circuitos lógicos secuenciales. El primer ejercicio explica que las puertas añadidas a la entrada de un latch D tienen como objetivo completar el latch D a partir de un latch SR más simple. El segundo ejercicio pide completar un cronograma de salida para dos flip-flops conectados en serie. Y el tercer ejercicio contiene preguntas sobre tipos de circuitos secuenciales y cálculos de tiempos de ciclo.

Cargado por

Kevin ContrerasDerechos de autor

© © All Rights Reserved

Nos tomamos en serio los derechos de los contenidos. Si sospechas que se trata de tu contenido, reclámalo aquí.

Formatos disponibles

Descarga como PDF, TXT o lee en línea desde Scribd