Documentos de Académico

Documentos de Profesional

Documentos de Cultura

S03 00200 BT2 Alp01

Cargado por

LucíaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

S03 00200 BT2 Alp01

Cargado por

LucíaCopyright:

Formatos disponibles

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

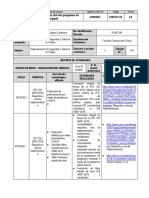

BLOQUE TEMÁTICO 2

TÍTULO DE LA ACTIVIDAD: CÓDIGO:

Tutorial de captura y simulación BT2_ALP1

GRUPO FECHA:

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

85

MODALIDAD: Laboratorio TIPO: Presencial DURACIÓN:

minutos

CALENDARIO: Tercera Sesión REQUISITOS:

CRITERIO DE ÉXITO: Aplicación del ciclo de captura y simulación de un sistema combinacional simple

ROLES:

HABILIDADES

SOCIALES:

REFLEXIÓN DE

GRUPO:

TIEMPO DEDICADO: No procede CALIFICACIÓN: [entre No procede

0 y 10 puntos]

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1: Tutorial de captura y simulación

ÍNDICE

INTRODUCCIÓN AL TUTORIAL DE CAPTURA Y SIMULACIÓN ....................................... 3

Normas para la realización del tutorial .............................................................................. 3

Creación de un proyecto de Trabajo ................................................................................. 3

Captura del esquema de un circuito digital ....................................................................... 4

Simulación de un circuito digital ........................................................................................ 4

Definición de pruebas de simulación en circuitos combinacionales .................................. 5

Simulación ........................................................................................................................ 5

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Verificación de resultados ................................................................................................. 7

TUTORIAL DE CAPTURA Y SIMULACIÓN ......................................................................... 9

Introducción. Entornos de CAD Electrónico ...................................................................... 9

EL ENTORNO DE CAD QUARTUS II .................................................................................10

Introducción .....................................................................................................................10

Realización de simulaciones ............................................................................................10

Gestión de diseños ..........................................................................................................11

CREACIÓN DE UN PROYECTO DE TRABAJO .................................................................12

Introducción .....................................................................................................................12

Iniciando la aplicación QUARTUS II .............................................................................13

Finalización de una sesión de trabajo ..........................................................................14

La Herramienta de Ayuda ................................................................................................15

Proyectos en el entorno QUARTUS II ..............................................................................16

Ficheros de diseño y ficheros auxiliares .......................................................................16

Creación de un proyecto en QUARTUS II ....................................................................18

CAPTURA DEL ESQUEMA DE UN CIRCUITO DIGITAL ...................................................23

La captura de esquemas..................................................................................................23

Chequeo de las reglas de diseño .....................................................................................32

El compilador ...................................................................................................................33

El proceso de compilación ............................................................................................33

Configuración del compilador .......................................................................................34

SIMULACIÓN DE UN CIRCUITO DIGITAL .........................................................................35

El editor de formas de onda .............................................................................................35

El simulador lógico ...........................................................................................................41

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1: Tutorial de captura y simulación

INTRODUCCIÓN AL TUTORIAL DE CAPTURA Y SIMULACIÓN

Normas para la realización del tutorial

El objetivo de esta actividad es que asimile el ciclo de operaciones a realizar para

capturar y simular circuitos digitales simples utilizando el entorno de CAD QUARTUS II

Web Edition de ALTERA, adquiriendo al mismo tiempo un conjunto mínimo de habilidades

para el manejo de las herramientas de dicho entorno.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Para conseguir este objetivo deberá seguir las instrucciones del tutorial que

encontrará en este documento como Anexo I y, cuando resulte necesario, consultar con el

profesor las dudas, curiosidades o problemas que puedan surgir durante su realización.

La actividad se realiza por parejas, por lo que resulta conveniente que los miembros

de la misma vayan alternando el manejo del PC durante la realización de las diferentes

tareas que componen el tutorial.

El tutorial se basa en un ejemplo guiado y tiene tres partes: creación de un proyecto,

captura del esquemático de un circuito y simulación funcional del circuito capturado.

Creación de un proyecto de Trabajo

Incluye, además de la creación de proyectos, una presentación del software, las

instrucciones para arrancar y salir del entorno, una descripción de la herramienta de ayuda

incluida en el software y la presentación del ejemplo en que se basa el tutorial. Ocupa la

primera parte del tutorial, hasta la página 22.

1. Comience a realizar el tutorial y complete las operaciones indicadas hasta la página

22.

2. Es muy importante que haya aprendido:

a. Las operaciones que hay que realizar para crear un proyecto de trabajo.

b. Las consecuencias de la creación de un proyecto de trabajo: creación de un

directorio donde se almacenan todos los ficheros relacionados con el

desarrollo de un sistema digital.

c. Dónde se ubican los proyecto de trabajo: en un directorio de su cuenta que se

crea durante la operación de creación del proyecto.

Si tiene alguna duda en relación con estas cuestiones, recurra a su profesor de

laboratorio.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1: Tutorial de captura y simulación

Captura del esquema de un circuito digital

Las tareas relacionadas con la descripción de un circuito digital simple mediante un

esquema gráfico se describen entre las páginas 23 y 33 del tutorial.

1. Complete las operaciones del tutorial relativas a la realización de esquemas de

circuitos.

2. Es muy importante que haya aprendido:

a. Cómo se crea un fichero de captura de esquemas.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

b. Cómo se emplazan los símbolos de los operadores lógicos (puertas)

necesarios para construir el esquema del circuito.

c. Cómo se dibujan los hilos de conexión entre los terminales de los símbolos.

d. Cómo se salvan los cambios en el esquema del circuito.

e. Por qué y cómo se chequea el cumplimiento de las reglas de construcción de

un circuito.

f. Si tiene alguna duda en relación con estas cuestiones, recurra a su profesor

de laboratorio.

Simulación de un circuito digital

El propósito de la simulación de un circuito es verificar que su funcionamiento se

corresponde con el deseado, para comprobar que no se han cometido errores durante el

proceso de diseño y construcción de su modelo lógico. El objetivo último de la simulación

es minimizar la probabilidad de que se realice a una materialización hardware del circuito

con errores de diseño lógico, porque:

1. Es mucho más fácil y rápido detectar y analizar este tipo de errores en una

simulación que en el prototipo hardware de un sistema.

2. Cuando se realizan pruebas sobre un prototipo hardware puede haber problemas de

funcionamiento derivados de la propia construcción del prototipo, que mezclados

con errores en el diseño lógico, si no se ha realizado una buena simulación del

circuito, pueden dificultar extraordinariamente la depuración del sistema.

El diseñador de una simulación debe conocer con precisión el funcionamiento que

espera observar como resultado de la simulación, con el objeto de poder detectar

discrepancias entre el funcionamiento esperado y los resultados de la simulación que

pongan de manifiesto errores de diseño.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1: Tutorial de captura y simulación

Antes de realizar una simulación es necesario analizar el circuito para determinar el

conjunto de pruebas que se consideran suficientes para verificar su funcionamiento. Esta

tarea tiene una complejidad proporcional a la del circuito que se desea simular: en circuitos

simples resulta muy sencilla, mientras que en sistemas complejos puede suponer un

esfuerzo mucho mayor que el del propio diseño del circuito.

Sólo en el caso de circuitos muy simples es posible realizar simulaciones en las que

se prueban todas las posibles condiciones de funcionamiento, es decir, realizar

simulaciones exhaustivas. Por ejemplo, el número de combinaciones diferentes que

pueden darse en la entrada de un circuito combinacional es 2 N, donde N es el número de

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

bits de entrada: si un circuito combinacional tiene 4 bits de entrada, una simulación en la

que se prueben las 16 combinaciones distintas que pueden formarse es fácilmente

realizable; si, en cambio, el circuito tuviera un número mucho mayor de entradas no sería

viable realizar una simulación exhaustiva –tal prueba en un circuito con 64 entradas (un

sumador de 32 bits, por ejemplo), requeriría de la realización de una simulación con más

de un trillón de combinaciones diferentes de entrada: en estos casos hay que seleccionar

inteligentemente el conjunto de combinaciones que permiten alcanzar una seguridad

suficiente sobre el correcto funcionamiento del circuito.

El ciclo de simulación comprende las siguientes tareas:

1. Definición de las pruebas de simulación (definición de los vectores de test).

2. Ejecución de la simulación.

3. Verificación de resultados.

Definición de pruebas de simulación en circuitos combinacionales

La verificación de circuitos combinacionales simples, aquellos cuya especificación

puede realizarse mediante una tabla de verdad completa y no resumida, puede realizarse

mediante una simulación exhaustiva, en la que se pruebe la respuesta del circuito a todas

las posibles combinaciones de entrada. En el caso de que se trate de circuitos complejos –

con más de 5 entradas- debe realizarse una selección de un conjunto suficiente de

combinaciones que prueben los distintos modos de operación del circuito.

Simulación

Para ejecutar una simulación es necesario:

1. Generar un modelo del circuito bajo prueba ejecutable por el simulador.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1: Tutorial de captura y simulación

2. Materializar las pruebas de simulación definidas en un formato ejecutable por el

simulador.

3. Ejecutar la simulación.

La generación del modelo del circuito y la ejecución de la simulación son realizadas

automáticamente por herramientas de CAD y no requieren otra intervención del diseñador

más que la orden de ejecución de la operación. La materialización de las pruebas que

componen el test del circuito requiere un trabajo de edición en un formato gráfico o textual.

En el entorno QUARTUS II:

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

1. La generación del modelo de simulación puede ordenarse una vez que se ha

chequeado su esquema.

2. La edición de las pruebas de test se debe realizar una vez generado el modelo de

simulación.

3. La simulación se debe ejecutar tras editar las pruebas de simulación.

La herramienta del entorno QUARTUS II que permite editar pruebas de simulación

es el editor de formas de onda (Simulation Waveform Editor), un editor gráfico que

dispone de comandos que facilitan la generación de patrones de test. A la hora de editar

las pruebas de test de circuitos combinacionales:

1. Calcule el tiempo total de simulación, de acuerdo con la siguiente fórmula:

Tiempo de simulación = Nº de combinaciones de test × Duración de cada combinación

2. En el editor de formas de onda, añada todas las entradas y salidas del circuito y:

a. Agrupe las diferentes entradas y salidas por separado y colóquelas en un

orden que facilite la verificación de los resultados.

b. Agrupe los buses y seleccione bases numéricas de representación que

faciliten la verificación de resultados.

En resumen, para realizar una simulación en el entorno QUARTUS II hay que

realizar, por orden, las siguientes operaciones:

1. Generar con el compilador un modelo de simulación del circuito.

2. Definir con una herramienta de diseño gráfico los estímulos de prueba del circuito.

3. Ejecutar una simulación.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1: Tutorial de captura y simulación

Verificación de resultados

Una vez ejecutada la simulación deberá verificar que los resultados de la misma

coinciden con los esperados. En el entorno QUARTUS II los resultados de la simulación se

representan gráficamente en el fichero de edición de formas de onda.

Si detecta errores de funcionamiento:

1. Analice la operación del circuito para los casos en los que se producen errores.

2. Una vez detectados los errores de diseño, corríjalos y modifique el esquema del

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

circuito.

3. Debe comprobar que el circuito modificado funciona correctamente; para ello:

a. Genere el modelo de simulación para el nuevo circuito.

b. Ordene la ejecución de una nueva simulación (en la que se utilizará el mismo

fichero de pruebas de test).

c. Verifique que el circuito funciona correctamente –si no es así, repita el

proceso.

Las tareas necesarias para realizar la simulación funcional de un circuito se

describen a partir de la página 35.

1. Complete las operaciones del tutorial relativas a la realización de simulaciones.

2. Es muy importante que haya aprendido:

a. Cómo se genera el modelo de simulación de un circuito.

b. Cómo se crea un fichero de edición de formas de onda.

c. Cómo se emplazan las entradas y salidas del circuito en el fichero de edición

de formas de onda.

d. Cómo se define el tiempo de simulación.

e. Que conozca los comandos básicos que permiten definir las combinaciones

de entrada.

f. Que conozca el procedimiento para definir la base numérica de

representación del valor de buses.

g. Cómo se ordena la ejecución de una simulación.

Si tiene alguna duda en relación con estas cuestiones, recurra a su profesor de

laboratorio.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018 © 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

TUTORIAL DE CAPTURA Y SIMULACIÓN

Introducción. Entornos de CAD Electrónico

La secuencia de operaciones que es necesario llevar a cabo para la realización de

un sistema a partir de unas determinadas especificaciones constituye lo que se suele

denominar, genéricamente, ciclo de diseño. El conjunto de operaciones y su

secuenciamiento depende de las metodologías y tecnologías que se vaya a utilizar en cada

caso. Las herramientas de CAD (Diseño Asistido por Computador), son utilidades software

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

que ayudan al ingeniero en las tareas del ciclo de diseño que pueden ser realizadas

automáticamente. La difusión y popularización de los ordenadores y del software, asociada

a la reducción de costes que han sufrido en los últimos años, ha hecho posible que el uso

de entornos software de CAD esté hoy al alcance de gran número de profesionales y

estudiantes.

En el campo del diseño electrónico digital, el uso de entornos de CAD es, además

de una ayuda valiosísima, un elemento imprescindible para el acceso a la realización de

sistemas electrónicos empleando las tecnologías más modernas: PLDs, FPGAs y ASICs.

Los entornos de CAD electrónico actuales son capaces de realizar la mayor parte de las

tareas del ciclo de diseño, dejando al diseñador la misión de especificar correctamente los

sistemas, las pruebas de validación de los mismos, y, naturalmente, el manejo del propio

entorno de CAD.

Los entornos de CAD electrónico integran distintos tipos de herramientas, además

de otras más sofisticadas, es habitual disponer de las siguientes:

Editores gráficos (capturas de esquemas) y de texto (para la elaboración de

especificaciones con lenguajes de descripción hardware, HDLs) que facilitan la

especificación del diseño,

Simuladores que permiten verificar el correcto comportamiento de las

especificaciones y los circuitos realizados (simuladores lógicos, analizadores de

tiempos), y

Herramientas de Place & Route que facilitan la realización física del diseño en

una determinada tecnología (planos de tarjetas de circuito impreso, ficheros de

programación de PLDs o FPGAs, etc.).

Para que las herramientas que componen el entorno de CAD puedan comunicarse

entre sí y llevar a cabo, de manera automática, las tareas necesarias para el desarrollo de

los diseños, debe existir una determinada organización de la información que es específica

de cada entorno y del sistema operativo del ordenador que se esté utilizando. Esta

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

organización de la información puede ser controlada, normalmente, mediante una serie de

utilidades que son, también, parte integrante del entorno de CAD.

En este texto se ofrece un tutorial para la realización de simulaciones lógicas en el

entorno QUARTUS II –desarrollado por ALTERA, uno de los principales fabricantes de

dispositivos lógicos programables, como herramienta CAD para el diseño con sus

productos. Se ha escogido como herramienta de apoyo para este curso de iniciación por

su sencillez y porque ALTERA, además, proporciona versiones de uso libre de este

entorno para aplicaciones industriales y docentes.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

EL ENTORNO DE CAD QUARTUS II

Introducción

Las herramientas que integran el entorno QUARTUS II pueden clasificarse, de acuerdo

con sus funciones, en los siguientes grupos:

1. Herramientas de especificación de diseños: captura de esquemas y editores de

texto.

2. Herramientas para la verificación de diseños: Una herramienta gráfica para la

especificación de los vectores de test de los diseños y la visualización de

resultados, un simulador lógico y un analizador de tiempos.

3. Herramientas para el procesamiento de los diseños: El compilador y el

procesador de mensajes.

4. Herramientas de programación de dispositivos: El programador y el hardware

de programación asociado.

Dado el propósito de este texto, la captura de circuitos y la realización de simulaciones

lógicas, sólo se utilizará la herramienta de captura de esquemas, el compilador, el

procesador de mensajes, un editor de formas de onda y el simulador lógico.

Realización de simulaciones

El nombre que reciben los diseños en el entorno QUARTUS II es el de proyectos

(projects). La simulación lógica de un diseño comprende la serie de operaciones que se

detallan a continuación:

1. Especificación del diseño lógico: Consiste en la descripción del comportamiento

del circuito mediante la creación de un fichero de diseño y su edición utilizando la

captura de esquemas.

10

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

2. Generación del modelo de simulación del circuito: Consiste en la generación,

por medio del compilador, de un modelo del circuito capturado ejecutable por el

simulador, capaz de representar en la simulación el funcionamiento que tendría el

hardware.

3. Verificación del diseño lógico: La simulación lógica sirve para comprobar la

adecuación del diseño a las especificaciones de funcionamiento. En el proceso de

simulación se ven involucrados el compilador, para generar un modelo de

simulación del circuito, el editor de formas de onda, para generar los vectores de

test y visualizar los resultados de la simulación, y, por último, el simulador lógico,

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

que ejecuta la simulación.

Gestión de diseños

Las tareas descritas anteriormente requieren la cooperación de dos o más herramientas

del entorno; la ejecución de una simulación se realiza sobre un modelo lógico generado

por el compilador al que se aplican vectores de test especificados en el editor de forma de

onda. El entorno QUARTUS II gestiona automáticamente la interacción entre las

herramientas a través del concepto de proyecto. Un proyecto está almacenado en un

directorio del ordenador, comprende los ficheros de diseño y un conjunto de ficheros

auxiliares. Las herramientas del entorno - exceptuando los editores - procesan siempre los

ficheros correspondientes al proyecto de trabajo actual. El entorno QUARTUS II

proporciona una serie de utilidades para la gestión de los proyectos con el fin de facilitar el

desarrollo de las tareas que componen el ciclo de diseño en el entorno QUARTUS II.

11

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

CREACIÓN DE UN PROYECTO DE TRABAJO

Introducción

Para aprender a capturar circuitos lógicos, y a manejar las distintas herramientas

implicadas en el proceso, se va a realizar un ejemplo guiado con un circuito muy sencillo.

En la Figura 1 puede observarse el esquema del circuito, que sirve, como fácilmente

puede deducirse, para detectar cuando dos combinaciones de dos bits son iguales.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 1: Esquema del circuito a realizar

En el desarrollo guiado del ejemplo se utilizan las convenciones que se señalan a

continuación.

1. Las acciones dirigidas que deben ser realizadas para completar el tutorial van

precedidas del texto “Realice las siguientes operaciones:”. Antes de ejecutarlas,

lea atentamente todos los pasos que describen el procedimiento completo.

2. Cuando el desarrollo de una acción requiera la utilización del teclado del ordenador

y sea preciso pulsar más de una tecla se indicara de la siguiente manera: Tecla1 +

Tecla2.

3. A lo largo del texto se encontrarán explicaciones teóricas que aparecen enmarcadas

y sombreadas. Las notas aclaratorias y observaciones aparecen también

encuadradas pero sin sombrear.

12

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Iniciando la aplicación QUARTUS II

Realice las siguientes operaciones:

1.- Inicie la aplicación QUARTUS II en Windows.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 2: QUARTUS II en el menú de inicio de Windows

Observe que se abre la ventana del entorno, que, a partir de aquí, denominaremos

QUARTUS II Manager o ventana principal. Su aspecto es el de la Figura 3.

Figura 3: QUARTUS II manager

13

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

La ventana principal dispone de un conjunto de menús, algunos de los cuales también

están disponibles al activar las aplicaciones del entorno, y de una serie de iconos que dan

acceso a distintas herramientas y utilidades. Además contiene una barra de estado,

situada en la parte inferior de la ventana, que muestra el comando que ejecuta la opción

de un menú o del icono sobre el que esté situado el cursor del ratón. Los programas de

aplicación del entorno QUARTUS II son accesibles por medio de los menús Processing y

Tools y algunos de ellos, además, a través de los iconos de la ventana principal. Cuando

se ejecuta una aplicación, se abre una pestaña o una ventana de trabajo que puede

iconizarse o mantenerse abierta junto con otras, pudiendo activarse la que se desee

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

pulsando el ratón sobre la ventana o pestaña correspondiente. Además, algunas

aplicaciones - las que realizan algún tipo de procesamiento - pueden ejecutarse al mismo

tiempo que se está trabajando con los editores.

Finalización de una sesión de trabajo

Cuando desee cerrar el entorno QUARTUS II, debe activar la opción Exit en el

menú File.

14

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

La Herramienta de Ayuda

Antes de continuar con el desarrollo del diseño, va a presentarse una utilidad del entorno

QUARTUS II que puede servir de apoyo al desarrollo del tutorial: la herramienta de ayuda.

La ayuda del entorno QUARTUS II proporciona toda la información relevante acerca de

las herramientas básicas y de las librerías del entorno. Puede resultar muy útil para

ampliar el conocimiento sobre las herramientas y procedimientos que se utilizan durante

las simulaciones o para los alumnos que estén interesados en conocer y utilizar otras

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

capacidades y herramientas del sistema.

El menú de ayuda siempre está presente en la ventana principal del entorno. Los

submenús de ayuda de interés para usted son los siguientes.

Search: Activa una herramienta de búsqueda de temas de ayuda relacionados con un

texto introducido por el usuario, búsqueda por contenidos y acceso a foros. Suele

utilizarse como último recurso cuando han fallado otros métodos para acceder a la

información.

Message List: Informa sobre las posibles causas y sugiere posibles acciones a llevar a

cabo frente a los mensajes que pueden presentar las herramientas de QUARTUS II.

Devices and adapters: Presenta una lista de los dispositivos del fabricante Altera y

enlaza con información más detallada de sus dispositivos.

Getting starter tutorial: Contiene videos sobre el uso de las aplicaciones del entorno

PDF tutorial: Podrá encontrar pdfs de introducción al ciclo de diseño para los usuarios de

los lenguajes de descripción hardware VHDL y Verilog.

Tips and Tricks: Muestra consejos y trucos sobre diseño y el uso de las herramientas de

QUARTUS II. Esta ayuda se muestra dentro de una pestaña en el QUARTUS II Manager.

Altera on the Web: Contienen enlaces interesante para el diseñador que utiliza

QUARTUS II y productos de Altera.

15

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Proyectos en el entorno QUARTUS II

La primera tarea que hay que ejecutar para realizar un diseño en el entorno QUARTUS II

es la definición del proyecto de trabajo actual, el cual servirá de referencia a las

herramientas del entorno para buscar los ficheros que deben procesar y/o conocer el

directorio donde se debe almacenar el resultado del procesamiento.

Antes de indicar el procedimiento para la especificación del proyecto de trabajo, se

presentarán algunas nociones básicas sobre los proyectos en el entorno QUARTUS II.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Ficheros de diseño y ficheros auxiliares

Un proyecto está constituido por un conjunto de ficheros almacenados en directorios. Los

ficheros pueden clasificarse en dos categorías: ficheros de diseño y ficheros auxiliares.

Un fichero de diseño es un fichero gráfico o de texto, creado con un editor del entorno

QUARTUS II. Estos ficheros contienen la especificación lógica de los diseños que pueden

ser procesados por el compilador para generar modelos de simulación y/o ficheros de

programación de dispositivos (ficheros que sirven para que un chip fabricado por ALTERA

se configure con el circuito que se ha diseñado). El compilador puede procesar

automáticamente distintos tipos de ficheros que se identifican por una determinada

extensión. En este curso se van a utilizar únicamente ficheros realizados con la captura de

esquemas del entorno. Su extensión es bdf (block design file).

Los ficheros auxiliares son los que están asociados a un proyecto QUARTUS II sin formar

parte del diseño, pudiendo ser, en algunos casos, editables por el usuario; entre ellos se

encuentran todos los ficheros de salida de las aplicaciones del entorno (exceptuando, por

supuesto, los ficheros de diseño). Hay ficheros auxiliares que son generados

automáticamente por las aplicaciones, mientras que otros sólo se crean bajo

requerimiento del usuario.

Una de las características de QUARTUS II es que es un entorno muy flexible, en el

sentido de que normalmente hay varias formas de hacer cada una de las tareas y su

aspecto es muy configurable. En este tutorial se utilizará el entorno con la configuración

por defecto, y únicamente se hará referencia a un modo de efectuar cada tarea, aunque

puedan existir más.

La Figura 4 muestra el aspecto de la ventana principal de QUARTUS II. En ella

pueden distinguirse cinco zonas distintas:

16

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

1. Navegador de proyectos. En ella puede realizar tareas relativas al proyecto, como

ver y editar los ficheros que lo componen, ver las entidades que lo forman, etc.

2. Ventana de tareas. En esta ventana se muestra el progreso de las tareas o

procesos del flujo de diseño que se estén ejecutando.

3. Ventana de mensajes. Aquí se muestran los mensajes que las distintas

herramientas generan. Las pestañas en su parte inferior permiten ver todos los

mensajes o filtrarlos según su categoría (informativos, avisos, errores…).

4. Zona de visualización y edición. En esta zona es donde se muestra el contenido

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

de los ficheros que se están editando, de los informes que se están viendo, etc.

Permite trabajar con varios ficheros a la vez, usando un sistema de pestañas en la

parte superior similar a que utilizan las versiones modernas de los navegadores

web.

5. Barras de menú y de herramientas. Todas las funciones de QUARTUS II son

accesibles a través de los menús, y las que se usan con más frecuencia tienen

también un botón en la barra de herramientas. Además de los menús típicos de

cualquier aplicación, hay menús para operaciones relacionadas con la gestión de

proyectos (Project), para gestión de configuración del dispositivo o de las

herramientas de QUARTUS II (Assignments), para lanzar las distintas tareas del

flujo de diseño (Processing) y para lanzar diversas herramientas auxiliares (Tools).

1

4

2

3

Figura 4: Zonas de la ventana principal de QUARTUS II

17

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Creación de un proyecto en QUARTUS II

Realice las siguientes operaciones:

1. En el menú “File” de QUARTUS II seleccione la entrada “New Project Wizard…”

(véase la Figura 5).

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 5: Acceso al asistente de creación de proyectos

Aparecerá la ventana de introducción del asistente, mostrada en la Figura 6. Esta

ventana simplemente informa de los pasos que componen el proceso. Si no desea que

vuelva a aparecer cuando cree un proyecto puede marcar la casilla “Don’t show me this

introduction again” que aparece en la esquina inferior izquierda.

Figura 6: Ventana de introducción del asistente de creación de proyectos

1. Marque si lo desea la casilla “Don’t show me this introduction again” y haga click

sobre el botón “Next”.

18

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Aparecerá la primera página del asistente de creación de proyectos, mostrada en la

Figura 7. En esta página debe indicar en qué directorio desea ubicar el proyecto, cuál es el

nombre del mismo y cuál es la entidad de nivel superior (lo que habitualmente se conoce

como el top) del diseño.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 7: Primera página del asistente de creación de proyectos (ubicación y nombre del proyecto)

1. En la casilla superior, seleccione el directorio de trabajo en el que desea crear el

proyecto (D:\usuarios\e2_xx\comparador). Puede pulsar el botón “…” a la derecha

de la caja de texto superior (“What is the working directory for this project?”) o

indicar directamente la ruta. Si el directorio no existe se creará.

2. Es extremadamente recomendable ubicar cada proyecto en un directorio separado,

ya que posteriormente se generarán un gran número de ficheros.

3. Introduzca el texto comparador como nombre del proyecto en la siguiente caja de

texto (“What is the name of this project?”). Fíjese en que el nombre del proyecto

se toma automáticamente como nombre de la entidad superior.

4. Pulse el botón “Next”.

Aparecerá la segunda página del asistente (Figura 8). En ella debe indicar qué

ficheros componen el diseño. En este tutorial añadiremos más adelante el fichero donde se

va a capturar el circuito. Ahora, simplemente pulse el botón “Next”.

Figura 8: Segunda página del asistente de creación de proyectos (ficheros de diseño)

19

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

En el caso de tener el fichero ya realizado, los pasos serían los siguientes:

1. Pulse el botón “…” que está situado a la derecha de la caja de texto superior (“File

name:”). Al cerrar la ventana de selección el nombre del fichero (incluyendo la ruta

del directorio que lo contiene) aparecerá en la caja de texto.

2. Pulse el botón “Add”. El fichero aparecerá en el área situada debajo de la caja de

texto.

3. Pulse “Next”.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

La siguiente página del asistente (Figura 9) permite indicar cuál es el dispositivo que

se va a utilizar en el proyecto. QUARTUS II ofrece dos posibilidades para esto: especificar

el dispositivo manualmente o permitir que la herramienta que escoja un dispositivo en

función de las características del circuito digital que se está realizando. Esta última opción

es útil cuando el diseño del circuito digital se realiza antes de haber fijado el hardware en el

que se va a realizar, pero este no es el caso, de modo que utilizaremos el primer método.

Figura 9: Tercera página del asistente de creación de proyectos (selección de dispositivo)

Debe seleccionar el dispositivo EPM3064ALC44-10 de la serie MAX3000A, que es

el que monta la tarjeta SEC-EII. Para ello:

1. Seleccione la familia MAX3000A en el desplegable “Family:”.

20

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

2. Filtre la lista de dispositivos mostrados utilizando el grupo “Show in

‘Available devices’ list” situado en la parte superior derecha de la ventana

para que se muestren únicamente los dispositivos con encapsulado de 44

pines (“Pin count:”) y de grado 10 (“Speed grade:”). Verá que la lista de

dispositivos mostrados se ha reducido a únicamente seis elementos.

3. Seleccione el dispositivo EPM3064ALC44-10. Ponga atención, es fácil

confundirse porque los códigos de dispositivo son muy parecidos entre sí.

4. Pulse “Next”.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

La siguiente ventana (Figura 10) permite seleccionar herramientas de diseño

electrónico automático (EDA, Electronic Design Automation, automatización de diseño

electrónico). QUARTUS II es una herramienta muy completa que cubre prácticamente

todas las etapas del diseño de circuitos digitales, pero existen herramientas especializadas

más potentes para buena parte de estas etapas, y también para algunas otras tareas que

QUARTUS II no realiza. QUARTUS II está preparado para trabajar con algunas de estas

herramientas, y eso es lo que se indica en esta ventana. Como no se van a utilizar en este

momento ninguna de ellas, se pasa esta ventana sin indicar nada.

Figura 10: Cuarta ventana del asistente de creación de proyectos (selección de herramientas)

1. Pulse el botón “Next”.

Finalmente aparece la última ventana del asistente, que muestra un resumen de lo

realizado en las ventanas anteriores, tal como se muestra en la Figura 11.

21

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 11: Última ventana del asistente de creación de proyectos (verificación final)

1. Compruebe que todo es correcto y pulse el botón “Finish”. Si detectara algún error

pulse el botón “Back” hasta volver a la ventana adecuada, corríjalo y repita el

proceso.

Si el proceso de creación del proyecto se ha realizado correctamente, aparecerá en

el Project Navigator según la siguiente figura:

Figura 12: Proyecto visible en el Project Navigator

Una vez finalizada la creación del proyecto, continuaremos con los pasos

necesarios.

22

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

CAPTURA DEL ESQUEMA DE UN CIRCUITO DIGITAL

Una vez definido el proyecto de trabajo, debe especificarse el diseño lógico del circuito

que se desea realizar. Para ello puede recurrirse a dos procedimientos: la creación y

edición de los ficheros de diseño o la importación de ficheros de diseño realizados con

otras herramientas.

En el ejemplo que se va a realizar se utilizará únicamente la captura de esquemas.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

La captura de esquemas

La captura de esquemas del entorno puede activarse al abrir un esquema ya

existente o crear uno nuevo, desde el menú File de la ventana principal del entorno.

En el ejemplo que se está realizando, hay que crear un fichero de diseño gráfico

para editar la descripción del circuito.

Realice las siguientes operaciones:

1. Seleccione, con el botón izquierdo del ratón, la opción File New... en la ventana

principal.

2. En la ventana que se activa (Figura 13), indique que se desea crear un fichero

gráfico seleccionando la opción Block Diagram/Schematic File. Estos ficheros

tendrán la extensión bdf (block diagram file).

Figura 13: Creación de un fichero gráfico nuevo

23

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

3. Pulse el botón OK.

Aparece la pestaña de edición de la captura de esquemas.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 14: Área de captura de esquemas

Las utilidades de edición de la captura de esquemas pueden ser activadas mediante cinco

procedimientos:

1. Desde los menús de la nueva pestaña, que se adaptan siempre a las necesidades

de la herramienta activa. Por este procedimiento se pueden ejecutar todas las

utilidades.

2. Mediante los menús de “pop-up” que se despliegan al activar el botón derecho del

ratón en el área de dibujo; el contenido de estos menús cambia según el ratón se

pulse sobre una zona vacía o sobre un objeto seleccionado.

3. Mediante el teclado del ordenador. La combinación de teclas correspondiente a cada

función se indica en los menús de la ventana principal, junto al nombre de la misma;

por ejemplo, la función de copia de objetos (copy), puede invocarse con la pulsación

simultánea de las teclas Ctrl y C (abreviadamente Ctrl + C).

4. Mediante acciones del ratón. Algunas funciones se realizan, de manera exclusiva o

alternativa, activando el ratón en el contexto adecuado; por ejemplo, una doble

pulsación del botón izquierdo del ratón en un área libre de la hoja de esquemas,

permite seleccionar el símbolo de un módulo de librería que se desee incluir en el

esquema.

24

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Las utilidades de la captura para la elaboración del esquema del circuito se pueden

clasificar, de acuerdo a la funcionalidad que proporcionan, en los siguientes grupos:

1. Utilidades de edición: Tales como copiar, borrar y rotar objetos; se encuentran

agrupadas en el menú Edit.

2. Utilidades para controlar la visualización del esquema: Son funciones que

permiten determinar el tamaño del área de la hoja de esquemas que se visualiza en

la ventana (funciones de zoom), qué parte del esquema se visualiza, así como los

colores empleados en la visualización de los objetos (opciones de configuración).

Las funciones de zoom se encuentran en el menú View, las de configuración en el

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

apartado Options del menú Tools, ambos en la ventana principal, y la función de

pantalla – en las capturas de esquemas se suele llamar pan a la función que permite

mover el área visible de la hoja de dibujo - se controla con las barras de

desplazamiento de ventanas de Windows.

3. Utilidades para el emplazamiento de objetos en el esquema: Permiten elegir los

módulos y primitivas que se emplazan en la hoja de dibujo, la gestión de las librerías

de usuarios, la actualización de símbolos y la creación de hilos y etiquetas de

conexión, así como la definición del estilo de líneas y texto empleados. Se

encuentran agrupadas en el menú superior de la ventana de captura de esquemas.

Además de las funciones anteriores, se dispone de otras utilidades entre las que

destacan las siguientes.

1. Utilidades para la gestión de ficheros: Tales como salvar el fichero activo, abrir

ficheros, imprimir, etc. Se agrupan en el menú File.

2. Utilidades para el “enlace” de la captura con otras herramientas del entorno:

Desde el menú File se pueden ordenar operaciones que requieren la ejecución de

otras herramientas (tomando como referencia, siempre, el fichero de diseño

correspondiente al proyecto de trabajo); por ejemplo, puede ordenarse la compilación

y simulación del esquema (cuando ya exista un fichero con la definición de los

estímulos de test), o la generación automática de un símbolo.

Además, está accesible el contenido del menú Help.

A continuación se va a dibujar el esquema del circuito del ejemplo utilizando algunas

de las funciones descritas anteriormente.

En primer lugar, se van a situar sobre la hoja de dibujo los símbolos de los

dispositivos lógicos necesarios para realizar el circuito.

Realice las siguientes operaciones:

25

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

1. Realice un doble clic, con el botón izquierdo del ratón, sobre una zona libre de la

hoja de dibujo.

2. Aparecerá la ventana de selección de símbolo (Figura 15). Escriba en la casilla

“Name” la palabra XOR. Observe que en la zona de visualización de la ventana

aparece el símbolo de la puerta XOR.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 15: Ventana de selección de símbolo

3. Pulse el botón OK. Observe que aparece una instancia del componente sobre la

hoja de dibujo adjunta al puntero.

4. Coloque el símbolo en el área de captura con un clic del botón izquierdo del ratón.

En el símbolo pueden distinguirse los siguientes elementos:

a. El área de selección, dibujada con trazo discontinuo, limita la zona ocupada por el

símbolo. Al pulsar el botón izquierdo del ratón dentro de esta área se selecciona la

instancia y se resalta, en un determinado color, el perímetro del símbolo.

b. Un dibujo y un nombre que permiten identificar el componente.

c. Un nombre de instancia acompañado de un número (la primera instancia que se

coloca no lleva número), situado en la parte inferior izquierda, que se genera

automáticamente al emplazar el símbolo, que es único, en cada esquema, y sirve

para identificar cada símbolo del circuito. El número de la instancia se va

incrementado a medida que se van incluyendo nuevos símbolos en el dibujo.

26

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Figura 16: Ejemplo de instanciación de símbolos

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Repita el procedimiento anterior para emplazar una puerta NOR de dos entradas,

escribiendo NOR2 en la casilla “Name” (Figura 15).

Figura 17: Instanciación de la puerta NOR de 2 entradas

Como se necesitan dos puertas XOR, se va a copiar la que ya se ha emplazado.

Realice las siguientes operaciones:

1. Seleccione la puerta XOR situando el cursor del ratón sobre su símbolo y pulsando

el botón izquierdo.

2. Pulse las teclas Ctrl + C.

3. Pulse el botón izquierdo del ratón en una zona libre de la hoja.

4. Pulse las teclas Ctrl + V.

Para trabajar más cómodamente, se pueden llevar los símbolos al centro de la hoja

de dibujo.

Realice las siguientes operaciones:

1. Para visualizar la hoja completa, seleccione en el menú View la opción “Fit in

Window” (Figura 18).

27

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Figura 18: Visualización de la hoja completa

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

2. Arrastre el cursor del ratón, con el botón izquierdo pulsado, hasta definir un

rectángulo que comprenda en su interior todos los símbolos. Una vez definido el

rectángulo, suelte el botón izquierdo del ratón.

3. Pulse el botón izquierdo del ratón encima de algunos de los elementos

seleccionados y, sin soltarlo, muévalo hasta el centro de la hoja. Una vez

desplazados los símbolos suelte el botón del ratón.

4. Para recuperar una visualización adecuada de los símbolos, pulse sobre el icono

de la barra de herramientas. Pulsando sobre el botón izquierdo aumentará el

tamaño de la zona visualizada y sobre el botón derecho disminuirá.

5. Pulse la tecla Esc para volver al modo normal de edición.

Figura 19: Emplazamiento inicial de las puertas seleccionadas

A continuación, hay que colocar los símbolos en la posición adecuada para la

realización del circuito - aunque esto, normalmente, suele hacerse en el momento de la

colocación del símbolo (de modo que, si ya están colocados, ignore las siguientes

instrucciones) .

28

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Realice las siguientes operaciones:

1. Pulse el botón izquierdo del ratón sobre el símbolo que desee mover, para

seleccionarlo.

2. A continuación, sitúe el ratón sobre el símbolo y arrástrelo a la posición deseada.

3. Repita las operaciones anteriores hasta obtener una colocación parecida a la de la

Figura 19.

Antes de realizar las conexiones del circuito, hay que situar los símbolos que

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

representan los pines de entrada y salida.

Realice las siguientes operaciones:

1. Repita las operaciones realizadas en la colocación de los símbolos para los pines de

entrada (input) y salida (output). Dibuje uno de cada clase, copie el de entrada,

pues se necesitan cuatro, y muévalos a las posiciones deseadas repitiendo las

operaciones que ya se han descrito.

El circuito deberá tener un aspecto similar al de la Figura 20.

Figura 20: Aspecto del circuito sin cablear

Seguidamente se deben realizar las conexiones del circuito.

29

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Realice las siguientes operaciones:

1. Pulse el icono de la barra de herramientas. El cursor del ratón toma forma de

cruz.

2. Realice las conexiones necesarias para obtener el circuito de la Figura 21, pulsando

el botón izquierdo del ratón en el inicio de cada conexión, y soltándolo en el punto al

que se desea conectar. Si se equivoca en alguna conexión pulse las teclas Ctrl+Z

(Deshacer), o borre el hilo, volviendo al modo normal de funcionamiento (vea el

punto 3 de este procedimiento), y pulsando la tecla Supr.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 21: Aspecto del circuito cableado

3. Cuando haya finalizado, pulse el icono de la barra de herramientas para volver

al modo de funcionamiento normal del ratón.

Por último, hay que poner nombres a los pines.

Realice las siguientes operaciones:

1. Realice una doble pulsación, con el botón izquierdo, en el campo PIN NAME del

símbolo del pin.

2. Con el teclado, escriba el nombre (A1, B1, A0, B0 para los pines de entrada y

A_igual_B, para el de salida), y pulse la tecla Return (Figura 22).

Una vez realizada esta operación, se habrá completado el esquema del circuito. Por

tanto se deberá guardar el fichero.

30

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Realice la siguiente operación:

1. Para salvar el fichero pulse las teclas Ctrl+S.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 22: Circuito definitivo

2. En la ventana que aparece - en la que se le ofrece como nombre por defecto el del

proyecto actual -, pulse el botón OK.

Figura 23: Ventana para salvar el fichero

31

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Chequeo de las reglas de diseño

La herramienta de captura establece una serie de reglas de diseño que se deben cumplir

a la hora de describir los circuitos. Cuando se haya completado el diseño, debe

comprobarse que se atiene a dichas reglas. El cumplimiento de las reglas de diseño es

una condición indispensable para la validación del circuito y el progreso hacia la siguiente

fase del ciclo de diseño, pero no implica que el circuito funcione correctamente -para

efectuar esta comprobación se debe realizar una simulación lógica.

La comprobación de las reglas de diseño en el entorno QUARTUS II es realizada por el

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

compilador del entorno. El resultado del procesamiento de las reglas puede dar lugar a

errores o advertencias que se comunican por medio del procesador de mensajes. El

procesador de mensajes, además de presentar los avisos generados por otras

herramientas del entorno, facilita la obtención de información adicional sobre los mensajes

y la localización de su origen.

El compilador del entorno QUARTUS II está involucrado en varias operaciones dentro del

ciclo de diseño, de entre ellas nos interesan las siguientes:

1. La comprobación de las reglas de diseño del proyecto de trabajo.

2. La generación del modelo de simulación del proyecto de trabajo.

Estas operaciones pueden realizarse separada o simultáneamente, dependiendo de las

circunstancias. Por ejemplo, la primera versión de un esquema suele chequearse

invocando el compilador desde la herramienta de captura, con la opción Analysis &

Elaboration del menú Processing de QUARTUS II; una vez comprobadas las reglas de

diseño, puede ordenarse la ejecución del compilador para generar un modelo de

simulación funcional. Si al simular el circuito se advierte algún error que obliga a la

modificación del diseño, pueden realizarse los cambios necesarios y, directamente, una

compilación en la que, además de comprobar las reglas de diseño, se genere un nuevo

modelo de simulación, simplificando las operaciones a realizar.

Realice las siguientes operaciones:

1. Ordene la verificación de las reglas de diseño Seleccionando la opción Start →

Analisys & Elaboration, , del menú Processing.

2. Aparecerá una nueva pestaña con el nombre Compilation Report. Si ha realizado

correctamente todas las operaciones, el compilador le indicará que no ha detectado

ningún error en el fichero. En caso contrario, corrija el circuito y repita la operación

de chequeo.

3. Cierre la ventana de aviso del compilador pulsando el botón OK.

32

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

4. Eche un vistazo a la pestaña Compilation Report y ciérrela.

Observe que en la ventana de tareas han quedado remarcadas en verde las

operaciones que se han realizado sobre el diseño.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 24: Ventana con las tareas ya realizadas

El compilador

El compilador del entorno QUARTUS II procesa automáticamente los ficheros del proyecto

de trabajo con el fin de completar la operación que el usuario haya ordenado.

La información de entrada del compilador es la contenida en el fichero de captura y en

algunos de los ficheros auxiliares.

El proceso de compilación

El compilador, de forma transparente al usuario, utiliza varias herramientas que sirven

para las siguientes tareas:

1. Analizar las reglas de diseño de los ficheros (gráficos o textuales) que contienen la

descripción del circuito y extrae la información que define las conexiones

jerárquicas entre los módulos del diseño, creando un mapa con la organización del

proyecto.

2. Procesa la información generada para crear una base de datos plana.

3. Se genera un modelo de simulación funcional.

33

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

La ejecución del compilador puede ordenarse desde desde un icono o desde la opción

Start del menú Processing de la ventana principal del entorno. Además, si durante la

ejecución del compilador se genera algún mensaje de aviso o error, éste se muestra en la

ventana de mensajes y, además, se abre una ventana indicando la existencia de errores.

Configuración del compilador

El procesamiento que realiza el compilador puede ser controlado por el usuario mediante

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

una serie de opciones disponibles en los menús de la ventana principal, clasificadas

según su funcionalidad. Las que permiten controlar la generación de modelos de

simulación están incluidas en la opción Settings… del menú Assignment.

Para que el compilador genere modelos de simulación funcional –modelos que

representan el comportamiento lógico ideal del circuito (sin retardos)-, debe seguir siempre

el procedimiento que se detalla a continuación.

Realice las siguientes operaciones:

1. Active el compilador a través de la opción Start → Analisys & Synthesis del menú

Processing, o pulsando las teclas CTRL + K.

2. Aparecerá una nueva pestaña con el nombre Compilation Report. Si ha realizado

correctamente todas las operaciones, el compilador le indicará que la compilación se

ha realizado con éxito. En caso contrario, corrija el circuito y repita la operación de

chequeo.

3. Cuando el compilador le indique que la operación se ha completado con éxito, cierre

la ventana pulsando el botón OK.

4. Para observar el resultado del procesamiento, active la opción Open del menú File,

y observe los ficheros y los diretorios (db, incremental_db y output_files) que se

han creado dentro del directorio del proyecto.

5. Pulse el botón Cancel.

6. Utilice los controles de ventana de Windows para cerrar la pestaña Compilation

Report y la captura de esquemas si lo desea.

34

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

SIMULACIÓN DE UN CIRCUITO DIGITAL

El editor de formas de onda

El editor de formas de onda del entorno QUARTUS II permite definir gráficamente los

vectores de simulación del diseño. Las utilidades específicas del editor de formas de onda

son las siguientes:

1. Funciones para la definición de nodos de simulación: Están contenidas en el

menú Edit. Permiten seleccionar los nodos de entrada, salida e internos que se van

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

a utilizar, definir grupos de nodos o segregar buses.

2. Funciones para la definición de niveles lógicos: Se encuentran en el menú Edit.

Facilitan la definición de formas de onda.

3. Funciones de configuración de edición: Permiten especificar el tamaño (tiempo

total de simulación) del fichero de simulación, la resolución máxima de edición

(duración mínima de un nivel lógico) y algunos otros parámetros. Se encuentran en

el menú Edit.

4. Funciones de visualización: Se encuentran en el menú View. Se dispone de

distintas modalidades de zoom.

Además se puede acceder a las funciones de manejo de ficheros, en el menú File, y a las

contenidas en los menús comunes con el resto de aplicaciones.

Al igual que en la captura de esquemas, se dispone de una barra de herramientas y de un

menú de “pop-up”, desde donde se pueden invocar las operaciones de uso más

frecuente. El editor de formas de onda dispone, además, de un cursor que funciona en

asociación con el ratón y de cuatro campos, que contienen valores numéricos, para la

medida de tiempos sobre las señales que se muestran en pantalla.

El editor de formas de onda puede invocarse desde el menú File.

Realice las siguientes operaciones:

1. Seleccione la opción New…

2. En la ventana New, seleccione del apartado Verification/Debugging Files la opción

University Program VWF y pulse el botón OK (Figura 25).

35

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 25: Opción para abrir el editor de formas de onda

3. Se abrirá la ventana Simulation Waveform Editor que permite la edición de

estímulos. Maximícela (véase la Figura 26).

Los ficheros gráficos de especificación de vectores (estímulos) tienen la extensión

vwf (vector waveform files). Si tuviese la necesidad de abrir un fichero .vwf ya creado,

hágalo desde la opción Open del menú file, seleccionando en la casilla Tipo la opción All

files (*.*) para poder verlo.

Figura 26: Ventana del editor de formas de onda

A continuación, se van a definir los nodos de simulación.

36

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Realice las siguientes operaciones:

1. En el menú Edit, seleccione la opción Insert, y dentro de ésta la opción Insert Node

or Bus…

2. De la nueva ventana Insert Node or Bus, pulse el botón Node Finder…

3. Aparece otra ventana, Node Finder, pulse el botón List. Observe que se listan, en

este caso, los pines de entrada y salida del circuito.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 27: Ventana de selección de nodos

4. Pulse , para pasar todos los nodos a la caja de selección.

5. Pulse el botón OK tanto en la ventana Node Finder como en la ventana Insert

Node or Bus. Los nodos indicados aparecen en la ventana de edición.

Por defecto, el tiempo de definición de los vectores en la ventana de edición es de

un microsegundo. A continuación se muestra el procedimiento para fijar una duración

distinta.

Realice las siguientes operaciones:

1. Active la opción Edit Set End Time...

2. Indique el valor 160 ns.

3. Pulse el botón OK.

Antes de editar el fichero se va a intercambiar la situación de las señales en el editor

de formas de ondas.

37

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Realice las siguientes operaciones:

1. Pulse el botón izquierdo del ratón sobre el icono del nodo A1 y, sin soltarlo,

desplace el cursor izquierdo del ratón hasta situarlo como el primero de la lista;

suelte el botón del ratón.

2. Repita la operación las veces que sean necesarias para ordenar las señales tal y

como aparecen en la Figura 28.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 28: Nodos en el editor de formas de onda

Para terminar con la edición de los vectores, se van a definir los valores lógicos de

los nodos de entrada.

Realice las siguientes operaciones:

1. Active la opción Fit in Window del menú View para visualizar todo el tiempo de

definición de estímulos.

2. Seleccione el nodo A0, situando el cursor del ratón encima del nombre del nodo y

pulsando el botón izquierdo del ratón.

3. Active el icono . Aparecerá la ventana Clock de la Figura 29.

Figura 29

38

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

4. Cambie el periodo a 20ns y pulse el botón OK.

5. Observe que aparece dibujada una señal periódica en el fichero de edición.

6. Repita la operación para A1, pero esta vez el periodo es 40ns. Observe que el valor

seleccionado para periodo sirve para controlar la duración de los niveles lógicos.

7. Repítala de nuevo para B0 y B1, seleccionando periodos de 80ns y 160ns

respectivamente.

El fichero debe quedar con un aspecto como el de la Figura 30. Observe que

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

aparecen las 16 combinaciones posibles de unos y ceros, de forma que la simulación de

este circuito combinacional será completa.

Figura 30: Formas de ondas para la simulación

Puesto que las líneas A1 y A0, por una parte, y B1 y B0, por otra, están asociadas

para codificar una combinación, resulta más cómodo que aparezcan representadas como

un grupo (un bus) en el fichero de edición de formas de onda.

Realice las siguientes operaciones

1. Seleccione la línea A1, pulsando una vez el botón izquierdo del ratón sobre el icono

de la señal.

2. Seleccione además A0 repitiendo la operación, pero manteniendo pulsada la tecla

Ctrl (para que no se deseleccione A1 al seleccionar A0).

3. Pulse el botón derecho del ratón, para que se despliegue el menú de “pop-up”, y

seleccione la opción Grouping →Group... (Figura 31).

39

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Figura 31: Procedimiento de agrupamiento de señales en buses

4. En la ventana que aparece ponga al bus el nombre A, seleccione la base Binario

Natural (Binary) y pulse el botón OK.

5. Repita la operación para formar un grupo con B1 y B0 con el nombre B.

El aspecto final del fichero debe asemejarse al de la Figura 32.

Figura 32: Señales agrupadas en buses

Puede cambiar la base en la que está expresada la información de los buses.

Realice las siguientes operaciones:

1. Pulse sobre alguna de las señales con el botón derecho del ratón para que se

despliegue el menú de “pop-up”, y seleccione la opción Radix y eche un vistazo a

las bases que están disponibles. Las bases que le pueden ser de mayor interés son:

Binario natural (Binary)

40

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

Hexadecimal

Decimal con signo (Signed decimal)

Decimal sin signo (Unsigned decimal)

Para terminar, hay que salvar la edición de las señales. Salve el fichero de estímulos

de simulación, pulsando las teclas Ctrl+S, con el nombre Comparador.

El simulador lógico

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

El simulador lógico del entorno QUARTUS II es capaz de realizar simulaciones

funcionales y con retardos. El simulador toma como entrada, automáticamente, el fichero

que contiene el modelo de simulación del proyecto actual y el fichero de estímulos cuyo

nombre coincida con el del proyecto (extensión vwf). Además, en la propia ventana del

simulador puede indicarse el nombre del fichero de vectores y los tiempos de inicio y

finalización de la simulación.

Realice las siguientes operaciones:

1. Seleccione la opción Run Functional Simulation en el menú Simulation del editor

de formas de onda. Aparecerán dos nuevas ventanas, Simulatión Flow, y una

nueva ventana con el resultado de la simulación, según se muestra en la Figura 33.

La primera de ellas carece de importancia para este curso.

Figura 33: Resultado de la simulación

2. Observe detenidamente el resultado de la simulación y verifique que el resultado de

la simulación se corresponden con el esperado para el circuito del ejemplo.

41

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

Actividad BT2_ALP1 – Anexo I: Tutorial de captura y simulación

El resultado de la simulación no se puede guardar (el fichero que se genera solo

tiene permiso de lectura), por lo que si tuviese que realizar algún cambio debería hacerlo

en el editor de formas de ondas inicial, modificar los estímulos y volver a ordenar una

simulación.

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

42

© 2010-2018 UPM – ETSIST – DTE – ELECTRÓNICA II – Curso 2017-2018

También podría gustarte

- S01_10100_BT1_AINP01Documento2 páginasS01_10100_BT1_AINP01popopopo1.Aún no hay calificaciones

- Catalogo Dip Sae-16 Jun-3 Sep 2022Documento28 páginasCatalogo Dip Sae-16 Jun-3 Sep 2022victorAún no hay calificaciones

- Escuela de Posgrado: Manual I Elaboración Del Proyecto de TesisDocumento42 páginasEscuela de Posgrado: Manual I Elaboración Del Proyecto de Tesishector pillacaAún no hay calificaciones

- Base de Datos 2 Guía Didáctica UPECDocumento58 páginasBase de Datos 2 Guía Didáctica UPECEdii SoonAún no hay calificaciones

- Trabajo ContabilidadDocumento6 páginasTrabajo ContabilidadMelany RicaldeeAún no hay calificaciones

- Anexo B - Chamorro - Parrales - Jhonattan - Alexander - 7756 - Parcial - 1Documento2 páginasAnexo B - Chamorro - Parrales - Jhonattan - Alexander - 7756 - Parcial - 1bradley castilloAún no hay calificaciones

- Silabo Cad II 2021-ParDocumento9 páginasSilabo Cad II 2021-ParMarcelo NeiraAún no hay calificaciones

- Diseño asistido por computador para planes de seguridad laboralDocumento1 páginaDiseño asistido por computador para planes de seguridad laboralMilton ChavezAún no hay calificaciones

- Silabo Motores de Combustión I Epimmem 2021 ParDocumento9 páginasSilabo Motores de Combustión I Epimmem 2021 ParJosé AlvaroAún no hay calificaciones

- Silabo Calculo 1 de Ciclo de Verano 2022 0Documento4 páginasSilabo Calculo 1 de Ciclo de Verano 2022 0maria vilela ramirezAún no hay calificaciones

- 2 Do Cuaderno de Informes Electronica IndustrialDocumento10 páginas2 Do Cuaderno de Informes Electronica IndustrializackosocuAún no hay calificaciones

- Ta 2404 24312 CartografíaDocumento5 páginasTa 2404 24312 CartografíaAJ Mapping SacAún no hay calificaciones

- Silabo - Electronica Fundamental (Teoria)Documento4 páginasSilabo - Electronica Fundamental (Teoria)PAUL ESAU NARVAEZ GILERAún no hay calificaciones

- S01_10200_BT1_AINP02Documento6 páginasS01_10200_BT1_AINP02popopopo1.Aún no hay calificaciones

- Rediseño Mecánica EPNDocumento87 páginasRediseño Mecánica EPNAlex Nicolas QuingaAún no hay calificaciones

- GFPI-F-019 - Formato - Guia - de - Aprendizaje No 1 ElectronicaDocumento13 páginasGFPI-F-019 - Formato - Guia - de - Aprendizaje No 1 Electronicanelson zambranoAún no hay calificaciones