Documentos de Académico

Documentos de Profesional

Documentos de Cultura

3ra Evaluacion 2021-2

Cargado por

Peoto Vallelin0 calificaciones0% encontró este documento útil (0 votos)

6 vistas2 páginasEste documento presenta las instrucciones para la tercera evaluación del curso de Arquitectura de Computadoras. Contiene cuatro problemas que deben resolverse usando el lenguaje VHDL y simularse en Quartus. Cada problema vale 5 puntos y los estudiantes deben enviar una carpeta con su nombre que contenga las soluciones de los problemas antes de la fecha límite al correo indicado.

Descripción original:

0

00.

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoEste documento presenta las instrucciones para la tercera evaluación del curso de Arquitectura de Computadoras. Contiene cuatro problemas que deben resolverse usando el lenguaje VHDL y simularse en Quartus. Cada problema vale 5 puntos y los estudiantes deben enviar una carpeta con su nombre que contenga las soluciones de los problemas antes de la fecha límite al correo indicado.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

6 vistas2 páginas3ra Evaluacion 2021-2

Cargado por

Peoto VallelinEste documento presenta las instrucciones para la tercera evaluación del curso de Arquitectura de Computadoras. Contiene cuatro problemas que deben resolverse usando el lenguaje VHDL y simularse en Quartus. Cada problema vale 5 puntos y los estudiantes deben enviar una carpeta con su nombre que contenga las soluciones de los problemas antes de la fecha límite al correo indicado.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 2

Facultad de Ingeniería

Escuela de Ingeniería Electrónica

3ra Evaluación

SEMESTRE 2021-II

Curso : ARQUITECTURA DE COMPUTADORAS

Grupo : 01

Profesor : Msc. Ing. Raúl Hinojosa Sánchez

Día : Lunes 14 de diciembre de 2020

Hora : 09:40 a 11.20

PROBLEMA 1. (5 ptos)

Arreglar el siguiente código en VHDL y graficar sus ondas empleando un reloj de 10Mhz

Emtity (apellido) is:

port (ck, reset: in bit;

q: bufer integre range 0 to 16);

end (apellido);

architeture diseño of (apellido) is;

begin

process (ck, reset):

begin;

if (reset='1') them q<=0;

else

if (ck' event and ck=”1”) then q=>q+1;

end if:

end if:

end process:

end diseño;

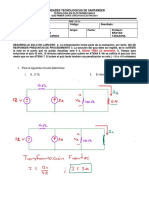

PROBLEMA 2. (5 ptos)

Para el siguiente registro de corrimiento, Halle el programa en VHDL a fin de demostrar su

funcionamiento en las salidas Q3,Q2,Q1,Q0. Si el reloj está programado a 1MHz.

PROBLEMA 3. (5 ptos)

Para el siguiente detector de secuencia tipo Mealy, determinar su funcionamiento mediante

Mealy empleando VHDL

PROBLEMA 4. (5 ptos)

Para el siguiente circuito:

a. Generar su código en VHDL.

b. Hallar su tabla de verdad, en base a los diagramas de tiempo, y compararlo con los diagramas

de tiempo que se van a generar en VHDL

(NO SIMPLIFICAR EL CIRCUITO)

INDICACIONES:

1. CADA PROBLEMA SIMULADO EN EL QUARTUS DEBE DE CONTENER SU APELLIDO

COMO NOMBRE DEL PROYECTO.

2. CREAR UN SOLO UNA CARPETA CON SU NOMBRE Y APELLIDOS Y ANEXAR LAS

SOLUCIONES

ENVIAR SU ARCHIVO EN UNA SOLA CARPETA AL CORREO:

cursos2020urp@hotmail.com

ASUNTO: 3ra Evaluación

También podría gustarte

- Prácticas de redes de datos e industrialesDe EverandPrácticas de redes de datos e industrialesCalificación: 4 de 5 estrellas4/5 (5)

- Activación de un Laboratorio de Telecomunicaciones: Telecomunicaciones y Electrónica, #1De EverandActivación de un Laboratorio de Telecomunicaciones: Telecomunicaciones y Electrónica, #1Aún no hay calificaciones

- 1ra Evaluacion 2021-2Documento3 páginas1ra Evaluacion 2021-2Peoto VallelinAún no hay calificaciones

- Segundo Parcial A2T1 Tarazona Lopez Luis EnriqueDocumento8 páginasSegundo Parcial A2T1 Tarazona Lopez Luis EnriqueEnrique Tarazona LopezAún no hay calificaciones

- LabED1 - MiM5M6 - 18, - P3Documento6 páginasLabED1 - MiM5M6 - 18, - P3Diego Aramis Castro IllescasAún no hay calificaciones

- Comunicación Síncrona Asíncrona 12F675Documento6 páginasComunicación Síncrona Asíncrona 12F675Kevin RojasAún no hay calificaciones

- Introduccion ArduinoDocumento5 páginasIntroduccion ArduinoDAMILEX666Aún no hay calificaciones

- Tarea 3 - Erika Velandia - 233.. (1) 2023Documento5 páginasTarea 3 - Erika Velandia - 233.. (1) 2023JUAN CARLOS AREVALO ALVAREZAún no hay calificaciones

- MooreDocumento73 páginasMooreHVMC Herrera MotaAún no hay calificaciones

- 20201M2 Preguntas Adicionales para IP de L1Documento2 páginas20201M2 Preguntas Adicionales para IP de L1Sergio Miguel Villa MendozaAún no hay calificaciones

- TC Ib 20212 Pec1Documento9 páginasTC Ib 20212 Pec1BycrakerAún no hay calificaciones

- SD Hoja Guia 4 2018BDocumento3 páginasSD Hoja Guia 4 2018BIsaacSánchezAún no hay calificaciones

- Micro Pic18f4550 Practica LCD Imprime CaracteresDocumento8 páginasMicro Pic18f4550 Practica LCD Imprime CaracteresJDamián DíazAún no hay calificaciones

- Lab3 Ee604 - Fiee UniDocumento1 páginaLab3 Ee604 - Fiee UniDavidAún no hay calificaciones

- Torres González Paloma Florisel - Práctica 2Documento10 páginasTorres González Paloma Florisel - Práctica 2Paloma TorresAún no hay calificaciones

- Tarea 3 Mpi1 CGT ProblemaDocumento3 páginasTarea 3 Mpi1 CGT ProblemaChristian Dominguez VidaurreAún no hay calificaciones

- Taller Sistemas NumericosDocumento3 páginasTaller Sistemas NumericosNicolas PardoAún no hay calificaciones

- Examen-Final-Sensores y Actaudores+Documento3 páginasExamen-Final-Sensores y Actaudores+Raul QuispeAún no hay calificaciones

- Lab04 - Sistemas DigitalesDocumento12 páginasLab04 - Sistemas DigitalesManuel Alejandro Ramos BandaAún no hay calificaciones

- TC Ib 20212 Pec2Documento8 páginasTC Ib 20212 Pec2BycrakerAún no hay calificaciones

- Práctica 07 Transformada de LaplaceDocumento8 páginasPráctica 07 Transformada de LaplaceEDRICH PAUL PACHECO CAMARGOAún no hay calificaciones

- 2020-6-5 Exam Final Enonce CorrectionDocumento7 páginas2020-6-5 Exam Final Enonce CorrectionLuc AusterAún no hay calificaciones

- Informe Práctica 1 Grupo 2Documento10 páginasInforme Práctica 1 Grupo 2Samuel VillamilAún no hay calificaciones

- MANUAL de Practicas de Control IIDocumento25 páginasMANUAL de Practicas de Control IIIngrid AgAún no hay calificaciones

- Lab1 Assembly Basic IO PDFDocumento3 páginasLab1 Assembly Basic IO PDFeliasAún no hay calificaciones

- Escuela Superior Politecnica Del Litoral: Programacion Orientada A ObjetosDocumento2 páginasEscuela Superior Politecnica Del Litoral: Programacion Orientada A ObjetosCarlos Israel JimenezAún no hay calificaciones

- pc1 SoluDocumento6 páginaspc1 SoluCarlos BarretoAún no hay calificaciones

- Facultad de Ingenieria Y Computacion Programacion I Tercera Unidad: Estructuras IterativasDocumento2 páginasFacultad de Ingenieria Y Computacion Programacion I Tercera Unidad: Estructuras IterativasFABIAN VILLARROELAún no hay calificaciones

- Guia de Laboratorio 1 Ev 4 - Brenda Jacqueline Mejia MartinezDocumento3 páginasGuia de Laboratorio 1 Ev 4 - Brenda Jacqueline Mejia MartinezBrenda MartinezAún no hay calificaciones

- Practica 2 Diseño Digital FI UNAMDocumento7 páginasPractica 2 Diseño Digital FI UNAMLUIS BARRERAAún no hay calificaciones

- Tarea 3 - MPI1 - CGT (Problema)Documento4 páginasTarea 3 - MPI1 - CGT (Problema)Yenss Requejo VegaAún no hay calificaciones

- Laboratorio - 1 Manejo Basico de Instrucciones de MicroDocumento6 páginasLaboratorio - 1 Manejo Basico de Instrucciones de MicrojoresnarAún no hay calificaciones

- Actividad Nº03 - CircuitoElectricosDocumento14 páginasActividad Nº03 - CircuitoElectricosJuana magdalena Gil perezAún no hay calificaciones

- Practica #5Documento7 páginasPractica #5Angel BernabeAún no hay calificaciones

- Grupo 2 Preinforme 2Documento11 páginasGrupo 2 Preinforme 2Nairo Guerrero MarquezAún no hay calificaciones

- Lab 3 de Sistemas de ControlDocumento7 páginasLab 3 de Sistemas de ControlJoselynCordovaPerezAún no hay calificaciones

- EE514-P1-Hinostroza Palomino JhonatanDocumento8 páginasEE514-P1-Hinostroza Palomino JhonatanCarlos BarretoAún no hay calificaciones

- Informe de Practicas 1Documento4 páginasInforme de Practicas 1Niza VidalAún no hay calificaciones

- Quiz-Circuitos I - B111Documento1 páginaQuiz-Circuitos I - B111Hiana MontagutAún no hay calificaciones

- Examen Parcial Control II EE648O 2021-II Primera ParteDocumento3 páginasExamen Parcial Control II EE648O 2021-II Primera ParteJorge TarquiAún no hay calificaciones

- Guia de Laboratorio 2020Documento50 páginasGuia de Laboratorio 2020Kev CortezAún no hay calificaciones

- Diseno de Pavimentos - UmssDocumento13 páginasDiseno de Pavimentos - UmssCarlos SyAún no hay calificaciones

- Circuitos CombinacionalesDocumento9 páginasCircuitos Combinacionalesoscar santosAún no hay calificaciones

- Guia Practica 3Documento4 páginasGuia Practica 3Andre ChaconAún no hay calificaciones

- Laboratory Exercise 6a.en - Es PDFDocumento3 páginasLaboratory Exercise 6a.en - Es PDFBriNyanAún no hay calificaciones

- Informe Práctica #3Documento4 páginasInforme Práctica #3Ian BaqueroAún no hay calificaciones

- Unidad Didactica PDFDocumento10 páginasUnidad Didactica PDFMEMORIAS TALLERESAún no hay calificaciones

- Practica 01 - Ee615Documento3 páginasPractica 01 - Ee615Josue Israel MendozaAún no hay calificaciones

- Informe Componente Practico Electronica de PotenciaDocumento6 páginasInforme Componente Practico Electronica de PotenciaJuan MercadoAún no hay calificaciones

- Lab02 - GL01Documento15 páginasLab02 - GL01Mario Ernesto Duran LopezAún no hay calificaciones

- Taller # 2 OAC SRDocumento8 páginasTaller # 2 OAC SRDelvis Joel CruzAún no hay calificaciones

- Laboratorio N°01Documento11 páginasLaboratorio N°01David MayangaAún no hay calificaciones

- Laboratorio - ConvertidoresDocumento7 páginasLaboratorio - ConvertidoresHugoJoséMirandaRodriguezAún no hay calificaciones

- Lab02 - Entradas y Salidas de PLCDocumento10 páginasLab02 - Entradas y Salidas de PLCfranAún no hay calificaciones

- TC Ib 20212 Pec3Documento8 páginasTC Ib 20212 Pec3BycrakerAún no hay calificaciones

- IEE Problemas Tema7 DigitalDocumento4 páginasIEE Problemas Tema7 DigitalnivekAún no hay calificaciones

- Solución Quiz-Circuitos II - D111Documento3 páginasSolución Quiz-Circuitos II - D111Sebastian DazaAún no hay calificaciones

- Circuito de Medición de VoltajeDocumento8 páginasCircuito de Medición de VoltajeManuel CabreraAún no hay calificaciones

- Metodología básica de instrumentación industrial y electrónicaDe EverandMetodología básica de instrumentación industrial y electrónicaCalificación: 4 de 5 estrellas4/5 (12)

- Teoria de La Calidad TotalDocumento9 páginasTeoria de La Calidad TotalPeoto VallelinAún no hay calificaciones

- Resumendetarjetasdevideo 130806200237 Phpapp01Documento23 páginasResumendetarjetasdevideo 130806200237 Phpapp01Peoto VallelinAún no hay calificaciones

- Fisica 2 Laboratorio 9Documento9 páginasFisica 2 Laboratorio 9Peoto VallelinAún no hay calificaciones

- Practica 1 Fuentes de Informacion Discretas 2020 IDocumento10 páginasPractica 1 Fuentes de Informacion Discretas 2020 IPeoto VallelinAún no hay calificaciones

- Informe de Tarjetas de VideoDocumento14 páginasInforme de Tarjetas de VideoPeoto VallelinAún no hay calificaciones

- Facultad de Ingeniería - URP. Arquitectura Del ComputadorDocumento11 páginasFacultad de Ingeniería - URP. Arquitectura Del ComputadorPeoto VallelinAún no hay calificaciones

- Planeacion 2Documento32 páginasPlaneacion 2Peoto VallelinAún no hay calificaciones

- Lab 2 Tele 2 Ramirez-CuadrosDocumento15 páginasLab 2 Tele 2 Ramirez-CuadrosPeoto VallelinAún no hay calificaciones

- Cuestioanrio Labo4Documento3 páginasCuestioanrio Labo4Peoto VallelinAún no hay calificaciones

- ENRUTAMINETODocumento68 páginasENRUTAMINETOPeoto VallelinAún no hay calificaciones

- Introduccion Ingenieria ElectronicaDocumento53 páginasIntroduccion Ingenieria ElectronicaPeoto VallelinAún no hay calificaciones

- S09 MatricesDocumento40 páginasS09 MatricesPeoto VallelinAún no hay calificaciones

- Lineas Tx-N°8 - Exp Palomino-Canales-CuadrosDocumento4 páginasLineas Tx-N°8 - Exp Palomino-Canales-CuadrosPeoto VallelinAún no hay calificaciones

- TAREA GRUPAL N°2 Mate III 2021-IDocumento16 páginasTAREA GRUPAL N°2 Mate III 2021-IPeoto VallelinAún no hay calificaciones

- Segunda Evalucion Telecomunicaciones II - Jibaja Enciso Marco AntonioDocumento3 páginasSegunda Evalucion Telecomunicaciones II - Jibaja Enciso Marco AntonioPeoto VallelinAún no hay calificaciones

- 5 - 3 - Filtros y Resonancia - AlumnosDocumento13 páginas5 - 3 - Filtros y Resonancia - AlumnosPeoto VallelinAún no hay calificaciones

- CEI - Laboratorio N°2 FILTROSDocumento11 páginasCEI - Laboratorio N°2 FILTROSPeoto VallelinAún no hay calificaciones

- Laboratorio Nº1 Divisores de Frecuencia Ok Galloso-CuadrosDocumento27 páginasLaboratorio Nº1 Divisores de Frecuencia Ok Galloso-CuadrosPeoto VallelinAún no hay calificaciones

- Acarga y Fuerza Urp Marzo 2022Documento35 páginasAcarga y Fuerza Urp Marzo 2022Peoto VallelinAún no hay calificaciones

- Sistemas Embebidos Usando Pic 18F4550Documento4 páginasSistemas Embebidos Usando Pic 18F4550Peoto VallelinAún no hay calificaciones

- Teoria - Neoclasica ActDocumento23 páginasTeoria - Neoclasica ActPeoto VallelinAún no hay calificaciones

- FUERZAS y TORQUE MAGNETICOS 2021Documento5 páginasFUERZAS y TORQUE MAGNETICOS 2021Peoto VallelinAún no hay calificaciones

- CEI - Laboratorio N°5 AMPLIFICADOR EMISOR COMÜNDocumento5 páginasCEI - Laboratorio N°5 AMPLIFICADOR EMISOR COMÜNPeoto VallelinAún no hay calificaciones

- Los Microcontroladores - 2 Caracteristicas Del PIC 18F4550Documento41 páginasLos Microcontroladores - 2 Caracteristicas Del PIC 18F4550Peoto VallelinAún no hay calificaciones

- Doble Conversor de Codigo-Canchis y Valverde (Autoguardado)Documento3 páginasDoble Conversor de Codigo-Canchis y Valverde (Autoguardado)Peoto VallelinAún no hay calificaciones

- Curso de Administracion I Tema VDocumento44 páginasCurso de Administracion I Tema VPeoto VallelinAún no hay calificaciones

- Clase 4 Lenguaje VHDLDocumento90 páginasClase 4 Lenguaje VHDLPeoto VallelinAún no hay calificaciones

- Lab Exp 6 VirtualDocumento6 páginasLab Exp 6 VirtualPeoto VallelinAún no hay calificaciones

- Trabajo Grupal Final, Grupo Pss 17 Impresora 3DDocumento64 páginasTrabajo Grupal Final, Grupo Pss 17 Impresora 3DPeoto VallelinAún no hay calificaciones