Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Programacion de Memoria PLD en Wincup

Cargado por

jesus antonioTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Programacion de Memoria PLD en Wincup

Cargado por

jesus antonioCopyright:

Formatos disponibles

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

NOMBRE DE LA

CARRERA PLAN DE ESTUDIO CLAVE ASIGNATURA

ASIGNATURA

Circuitos Lógicos

I.E.E. FLEXIBLE F0210

Combinacionales

NOMBRE DE LA DURACIÓN

PRÁCTICA No. LABORATORIO DE

PRÁCTICA (HORA)

Programación de memoria

7 Eléctrica y Electrónica

PLD en WinCUPL

2

1 OBJETIVOS

Iniciar el uso del software WinCUPL para construir circuitos combinacionales

Explicar mediante un ejemplo el proceso de programación de un PLD, retomando los

conceptos de la práctica 4 que corresponde a un sumador completo.

2 INTRODUCCIÓN

En esta práctica se introduce el uso y manejo del software WinCUPL, desde la

escritura del programa con WinCUPL, hasta la programación hardware.

Proporcionando un ejemplo para un dispositivo programable muy popular: el

GAL16V8. En la última parte se incluye un conjunto de recomendaciones útiles a la

hora de la programación con WinCUPL.

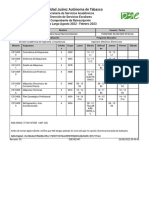

3 EQUIPO Y HERRAMIENTAS NECESARIAS EN EL TALLER

Cantidad EQUIPO Y HERRAMIENTAS MATERIAL DE APOYO

1 Computadora Pintarrón

1 Programador de dispositivos PLD Marcadores

1 GAL16V8 Práctica impresa

Bibliografía [1], [8],[10],

[11]

Titular de Laboratorio Titular de la materia Director de la División

2/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

4 DESARROLLO EXPERIMENTAL DE LA PRÁCTICA

A SIMULACIÓN EN WINCUPL

El programa de WinCUPL (Compilador Universal para Lógica Programable) es un

programa compilador mediante el cual se crean los diseños para PLDs, en caso de

alguna duda se puede consultar el menú de ayuda de WinCUPL pulsando [F1].

El software WinCUPL permite muchos de los modos de entrada convenientes como

parte del lenguaje de descripción del hardware. Existen tres métodos de entrada

diferente: una ecuación booleana, una tabla de verdad, o un diagrama

esquemático. (Figura 7.1)

Figura 7.1 Tres métodos de ingresar diseños de circuitos en un compilador

El archivo de entrada se divide en varias secciones. El encabezado que contiene

detalles de documentación, así como información que el compilador puede usar

para programar la parte que desee. Las secciones de entrada y salida se usan para

asignar nombres a las señales para pines reales en el dispositivo programable. La

sección de descripción del hardware permite que el diseño se describa en uno de

los modos convenientes previamente mencionados. Para este caso examinará el

modo de la ecuación booleana, figura 7.2. El cuadro 7.1 se muestran los

operadores lógicos y la sintaxis adecuada para ese modo.

3/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

Cuadro 7.1 Sintaxis CUPL para operaciones lógicas

Función Formato Formato

Operador

CUPL Convencional

AND & A&B A·B

OR # A#B A+B

NOT ! !A A

XOR $ A$B A⊕B

4/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

Figura 7.2 Ejemplo de formato usado para el archivo de entrada CUPL, modo de ecuación booleana

5/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

A continuación se presenta la forma de cómo utilizar el WinCUPL.

En la parte superior de la pantalla en la barra de comandos (commands) se

encuentran los diferentes menús de comandos que se pueden usar los cuales se

muestran de manera resumida en la figura 7.3.

Figura 7.3 Menús de WinCUPL

1.- Una vez abierto el programa, abre el archivo de entrada (escrito previamente en

cualquier procesador de textos) a través del menú principal File-Open. A

continuación compila, con la opción Run-Device Dependent Compile, indicada por

la flecha en la figura 7.4, que también incluye la pantalla obtenida tras una

compilación realizada con éxito.

6/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

Figura 7.4 Apertura del archivo PLD y compilación sin errores

Si la compilación finaliza con éxito se genera el archivo .JED, que será el que

utilizaras en el programa posterior para grabar en el PLD. En caso de error,

aparecen los mensajes correspondientes en la ventana de mensajes (messages).

Si esta ventana no aparece directamente, la visualizas con la opción Window-

Message.

El compilador genera siempre (incluso cuando haya errores) el archivo .DOC con

información sobre el programa del PLD, como por ejemplo, la función lógica

implementada en cada salida. Entre la información incluida en este fichero está el

número de productos que necesita la función implementada en cada salida, así

como el número de productos disponibles en dicha salida. Si el número de

productos disponibles, como pasa en el ejemplo de la figura 7.5, es menor que el

número de productos necesarios el programa no compilará.

En ese caso, verifica si es posible hacer una reasignación de pines, de forma que

en todas las salidas el número de productos necesarios sea menor al número de

productos disponibles, como en el fragmento mostrado en la figura 7.6

7/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

Figura 7.5 Error del fichero .DOC

Después de eliminar este tipo de errores es necesario eliminar los errores de

sintaxis, determinando la causa y corrigiéndola usando el procesador de textos para

modificar el archivo de entrada hasta conseguir que el fichero compile

correctamente (véase apartado de recomendaciones).

Figura 7.6 Reasignación de pines

Este proceso se repite hasta que no haya más errores o advertencias. En ese

punto, el diseño se puede probar usando un simulador. Entonces, el diseño lógico

se simula utilizando un conjunto de entradas hipotéticas conocidas como vectores

de prueba. Este proceso “ejercita”, de forma efectiva, el diseño por software para

determinar si trabaja correctamente, antes de programar realmente el PLD. Si se

descubre cualquier defecto de diseño durante la simulación, el diseño debe

depurarse y modificarse para corregir dicho defecto. Una vez terminado el diseño,

el compilador genera un archivo de documentación, que incluye las ecuaciones

lógicas finales, el archivo JEDEC y, si se desea un diagrama de los pines del PLD.

8/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

B DESARROLLO EN EL LABORATORIO

Para este ejercicio realiza el diseño de un sumador de 4 bits, utilizando el GAL16V8

el cual tiene ocho entradas dedicadas y ocho entradas/salidas (E/S), como muestra

el diagrama de la figura 7.7.

Figura 7.7 GAL16V8

Paso No. 1. Teclea en cualquier procesador de textos el archivo de entrada

presentado en la figura 7.8.

9/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

Name sumador4bits.pld;

Designer usuario ;

Partno practica6 ;

Company UJAT ;

Date enero/31/2008 ;

Assembly ninguna ;

Revision 01 ;

Location DAIA ;

Device p16v8 ;

Format j ;

/* Ejemplo de SUMADOR COMPLETO de 4 bits */

/* Asignacion de pines en Entrada y Salida del GAL */

/* Entradas */

pin 1 = C0; /* Acarreo de ENTRADA designado acarreo bit cero*/

pin [2..5] = [A0..3]; /*Sumando A 4 bits A (A0, A1, A2, A3)*/

pin [6..9] = [B0..3]; /*Sumando B 4 bits B (B0, B1, B2, B3)*/

/*Salidas */

pin [12,15,16,19] = [S0..3];

pin [13,14,17,18] = [C1..4]; /*Use C4(pin18) para el acarreo de salida

del sumador de 4 bits*/

/*Definiciones de CONJUNTOS */

field A = [A3..0]; /*Sumando de 4 bits */

field B = [B3..0]; /*Consumando de 4 bits */

field S = [S3..0]; /*Suma de 4 bits */

field Cin = [C3..0]; /* Acarreo de ENTRADA para cada uno de los cuatro

sumadores*/

field Cout = [C4..1]; /* Acarreo de SALIDA de cada sumador completo */

/* Descripcion del hardware */

Cout = A&B # A&Cin # B&Cin; /*Una ecuacion define los cuatro bits de acarreo de salida*/

S = A$(B$Cin); /*Esta ecuacion define el conjunto de 4 bits de la suma*/

Figura 7.8 Archivo de entrada para el GAL16V8

Paso No. 2. Abre el archivo de entrada mediante el menú File-Open, como se

muestra en la figura 7.9.

10/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

Figura 7.9 Apertura del archivo de entrada

Paso No. 3. Una vez abierto el archivo de entrada procede a compilarlo tal como se

indica en la figura 7.4 de la simulación en WinCUPL.

Paso No. 4. Si al compilar el archivo no se generan mensajes de error y funciona

de manera correcta con los vectores de prueba proce a programar el PLD, en este

caso el GAL16V8 (recuerda tomar la precaución necesaria para un circuito MOS).

Paso No. 5. Inserta el dispositivo PLD (GAL16V8) en el zócalo del programador,

que usualmente es un zócalo ZIF (zero insertion force, fuerza de inserción nula). En

la figura 7.10 se muestra en a) la vista del programador y en b) la forma correcta de

insertar el dispositivo en el programador. Si se inserta incorrectamente el

programador puede resultar dañado.

El programador contiene un programa controlador de software que lee el archivo

JEDEC generado por el compilador lógico y lo convierte en instrucciones que

aplican las tensiones requeridas en pines específicos del PLD, para alterar así las

celdas especificadas de la matriz de la forma que indique el mapa de fusibles.

11/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

a) b)

Figura 7.10 a) Vista del programador b) Forma correcta de insertar el dispositivo en el programador

Comienza el proceso conectando correctamente el módulo programador al

ordenador, encendiéndolo y colocando el PLD en el programador en su lugar

correcto (ajustada a la parte inferior, y con la muesca hacia arriba).

A continuación debes grabar el programa en el PLD. Para ello graba el fichero

JEDEC en el buffer intermedio y posteriormente en el PLD, como se muestra en la

figura 7.11, según los pasos de la figura 7.12:

Figura 7.11 Proceso de grabación del PLD.

12/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

Figura 7.12. Pasos para grabar un fichero en el PLD

Según este diagrama de bloques, la elección del dispositivo es el primer paso, para

el cual selecciona la opción Device del menú principal, después PLD y por último, el

PLD, PAL16V08Q de ATMEL. Si el dispositivo elegido no es correcto mostrará un

mensaje de error, y debes modificar la selección. En caso de elección correcta

veras una pantalla como la de la figura 7.13

Fabricante (ATMEL)

Dispositivo

seleccionado

Tipo de encapsulado

Información del

dispositivo

Figura 7.13. Pantalla para elegir el dispositivo.

13/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

Llegado a este punto, selecciona File, Load JEDEC File, y carga el .JED generado

en la compilación. Por último, pulsamos Program y se programará (quemará) el

PLD.

Recomendaciones

El WinCUPL incluye un directorio de ejemplos (examples) que pueden

utilizarse para familiarizarse con la sintaxis.

El WinCUPL NO admite la letra 'ñ' ni acentos, en ningún punto del programa

(ni siquiera en los comentarios). La presencia de cualquiera de estos

caracteres provocará la salida inmediata del programa cuando se intente

compilar, sin producir ningún fichero de salida ni ningún mensaje de error.

Tras la última línea de programa, en el fichero .PLD debes escribir al menos

2 retornos de carro. Si no lo haces, el programa no compilará.

Al programar con el WinCUPL es necesario tener en cuenta que en la

instrucción field posicion=[q3..0]; el orden de los términos q3 a q0 va a ser

siempre q3,q2,q1,q0, INDEPENDIENTEMENTE DEL ORDEN EN QUE LOS

SITUES, (¡sólo en esa instrucción!). Es decir, es lo mismo field

posicion=[q3..0]; que field posicion=[q0..3]; y el orden va a ser el indicado

anteriormente.

La cabecera del fichero de simulación (.si) debe ser exactamente la misma

que la del fichero .pld. En esta cabecera, se debe indicar que el Device es

"p16v8" (sin las comillas) y en Name se pondrá el mismo nombre que tiene

el fichero (sin la extensión).

Cuando utilizas la opción para programar mediante tabla de verdad es

necesario incluir todas las posibles combinaciones binarias de las entradas,

incluso las que nunca vayan a utilizarse en el circuito.

Algunas veces, al intentar compilar se muestra un mensaje de error

indicando que falta una dll. En esos casos se seguirán los siguientes pasos:

Option, Compiler options, Select library, y se seleccionará cupl.dl del

directorio donde esté instalado CUPL.

Si en las opciones de compilación (Alt-O) se activan "Simulation" y "Show

waveform" harás de una vez la compilación y la simulación, además al final

saldrá una ventana con el cronograma de las señales implicadas en la

simulación. MUCHO OJO cuando vayas a cerrarla, porque suele quedar

abierta también otra ventana por detrás. Si no se cierran TODAS las

ventanas antes de hacer la siguiente compilación, esta no se realizará

correctamente y tendrás que cerrar el WinCUPL y volver a abrirlo.

14/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

5 PREGUNTA S

1. Los dispositivos PLD pueden clasificarse como

(a) combinacionales y secuenciales

(b) programables y no programables

(c) programables una única vez y reprogramables

(d) PROM, PLA, PAL y GAL

(e) las respuestas (a) y (c)

(f) las respuestas ( c ) y (d)

2. Una GAL se diferencia de una PAL en que:

(a) una GAL tiene más entradas y salidas

(b) una GAL se implementa con una tecnología diferente

(c) una GAL puede reemplazar a diferentes PAL

(d) una GAL puede reprogramarse y una PAL no

(e) todas las respuestas anteriores

(f) todas las respuestas excepto la (a)

(g) todas las respuestas excepto ( c )

3. Las celdas reprogramables de una matriz GAL son

(a) TTL

(b) E2CMOS

(c) ECL

(d) Fusibles bipolares

4. OLMC es un acrónimo de:

(a) Output Logic Main Cell

(b) Optimun Logic Multiple Channel

(c) Output Logic Macrocell

(d) Odd-parity Logic Master Check

5. Para programar un PLD sólo se necesita:

(a) una herramienta especial

(b) una herramienta especial y un PLD maestro que se ha programado en fábrica

(c) una computadora y un programador

(d) una computadora, un programador y un software HDL

(e) una computadora, un programador y software BASIC

15/7 No. Revisión:____

UNIVERSIDAD JUÁREZ AUTÓNOMA DE TABASCO

DIVISIÓN ACADÉMICA DE INGENIERÍA Y ARQUITECTURA

DOCUMENTO DEL SISTEMA DE CALIDAD

MANUAL DE PRÁCTICAS DEL LABORATORIO

DE CIRCUITOS LÓGICOS COMBINACIONALES

6. ABEL y WinCUPL son tipos de:

(a) programadores

(b) dispositivos de PLD

(c) software HDL

(d) disco del sistema operativo

7. Los símbolos para NOT, AND, OR y XOR en WinCUPL son:

(a) !, &, +, $

(b) !, @, #, $

(c) !, &, #, $

(d) *, &, +, !

8. La expresión suma de productos X = ABC + A BC + ABC en WinCupl se escribe:

(a) X =!ABC# A!BC# AB!C ;

(b) X = !A & B & C # A & !B & C # A & B & !C ;

(c) X = !A & B & C # A&!B & C # A & B & !C

(d) X = (!A & B & C ) + (A & !B & C ) + (A & B & !C )

16/7 No. Revisión:____

También podría gustarte

- Simulacion TanqueDocumento4 páginasSimulacion TanqueJulio Cesar Lopez RodriguezAún no hay calificaciones

- Trabajo Completo de PLC Lavadora IndustrialDocumento10 páginasTrabajo Completo de PLC Lavadora IndustrialEvelyn Palma medinaAún no hay calificaciones

- Guía Proyecto de Curso 212Documento8 páginasGuía Proyecto de Curso 212Brandon LeonAún no hay calificaciones

- Lab0latorio de CircuitmakerDocumento4 páginasLab0latorio de CircuitmakerJose Maria QuintroAún no hay calificaciones

- Coco ValeDocumento43 páginasCoco ValeKatherine JacayAún no hay calificaciones

- T1 - A1 - Introduccion A Lenguaje de Programación para Métodos NúmericosDocumento12 páginasT1 - A1 - Introduccion A Lenguaje de Programación para Métodos NúmericosOctavio MedinaAún no hay calificaciones

- Conmutacion ForzadaDocumento6 páginasConmutacion ForzadaAndrés Hernandez100% (1)

- Tablero LEDDocumento12 páginasTablero LEDChristian Aguas NúñezAún no hay calificaciones

- Reporte - Analizador de Notaciones PresentaciónDocumento13 páginasReporte - Analizador de Notaciones PresentaciónjossueAún no hay calificaciones

- Manual - Prácticas de SimulaciónDocumento33 páginasManual - Prácticas de SimulaciónDV ReyesAún no hay calificaciones

- Laboratorio 1 Grupal AHPDocumento7 páginasLaboratorio 1 Grupal AHPkevin emanuel mosquera corredorAún no hay calificaciones

- Practica0 FinalDocumento9 páginasPractica0 Finalpaola quintanillaAún no hay calificaciones

- Lab 12 Grafcet Con El PLC CompactDocumento4 páginasLab 12 Grafcet Con El PLC CompactJhon Antony Ccapa HuisaAún no hay calificaciones

- Lab 1 - IntroduccionDocumento17 páginasLab 1 - IntroduccionAlexander Van StrahlenAún no hay calificaciones

- Practica 3Documento8 páginasPractica 3Angel PozosAún no hay calificaciones

- Formato PLCS EPNDocumento14 páginasFormato PLCS EPNTrajano Saúl Guevara MoralesAún no hay calificaciones

- TESISDocumento12 páginasTESISGiancarlos CasaperaltaAún no hay calificaciones

- Investigacion Optimizacion de CodigoDocumento12 páginasInvestigacion Optimizacion de Codigojossue100% (1)

- Informe 7 MecanismoDocumento19 páginasInforme 7 MecanismoAlejandro GómezAún no hay calificaciones

- Controladores Programables I IEKCIDocumento3 páginasControladores Programables I IEKCIFabi RiosAún no hay calificaciones

- Universalidad de Las Compuertas Nand y orDocumento18 páginasUniversalidad de Las Compuertas Nand y orDavid Hernández100% (1)

- ANSHELO BLADIMIR VELASCO CONSTANTE - PracticaLab - Programación ArduinoDocumento4 páginasANSHELO BLADIMIR VELASCO CONSTANTE - PracticaLab - Programación ArduinoAnshelo VelascoAún no hay calificaciones

- Reporte Nivel de Agua PIDDocumento6 páginasReporte Nivel de Agua PIDJORGE FERNANDO TELLO ESPA�AAún no hay calificaciones

- PracticasU2 Cruz Garcia Maciel HernandezDocumento7 páginasPracticasU2 Cruz Garcia Maciel HernandezOsvaldo García (Sonido Azteca)Aún no hay calificaciones

- Lenguajes de ProgramacionDocumento20 páginasLenguajes de ProgramacionJorge ChoqueAún no hay calificaciones

- Practica 4 Panel ViewDocumento7 páginasPractica 4 Panel ViewPalomares Guzmán Luis FernandoAún no hay calificaciones

- Práctica 2. Control de Un Semáforo Sencillo y de CruceDocumento5 páginasPráctica 2. Control de Un Semáforo Sencillo y de CruceSamantha Hoja VerdeAún no hay calificaciones

- Programacion de Los Lenguajes de Programacion PLC Definidos en La Norma IEC 61131-3Documento21 páginasProgramacion de Los Lenguajes de Programacion PLC Definidos en La Norma IEC 61131-3Renier de Jesus Cordova GonzalezAún no hay calificaciones

- UNIDAD I WilmaryDocumento10 páginasUNIDAD I WilmaryalondraAún no hay calificaciones

- 3 Dispositivos Digitales ProgramablesDocumento26 páginas3 Dispositivos Digitales ProgramablesAdrian MacayaAún no hay calificaciones

- Fpga Nexys 4ddrDocumento3 páginasFpga Nexys 4ddrDavid GuataAún no hay calificaciones

- Computacion IDocumento16 páginasComputacion IAdrian Miranda LopezAún no hay calificaciones

- Lab 1 - IntroducciónDocumento17 páginasLab 1 - IntroducciónIngrid DonadoAún no hay calificaciones

- Sistemas Digitales II IELDocumento3 páginasSistemas Digitales II IELRODRIGO RAMÓN BOLAÑOS SIFUENTESAún no hay calificaciones

- Laboratorio-01-Metodos Numericos-Aguirre Olivera Israel EduardoDocumento11 páginasLaboratorio-01-Metodos Numericos-Aguirre Olivera Israel EduardoIsrael Eduardo Aguirre OliveraAún no hay calificaciones

- Automatización Por Logica Programable 2Documento7 páginasAutomatización Por Logica Programable 2Kelvin Toledo ZernaAún no hay calificaciones

- Guia de Aprendizaje 2 Logica Cableada VirtualDocumento4 páginasGuia de Aprendizaje 2 Logica Cableada VirtualHaiberGarciaAún no hay calificaciones

- UNEFA S1 2012 ELN31335 EE501 LABSDII Formato para Presentar InformesDocumento3 páginasUNEFA S1 2012 ELN31335 EE501 LABSDII Formato para Presentar InformesManuel Alejandro GonzalezAún no hay calificaciones

- Guía de Laboratorio #5Documento7 páginasGuía de Laboratorio #5jesus gonzalezAún no hay calificaciones

- Eléctrónica Digital 2Documento3 páginasEléctrónica Digital 2Wara TorrezAún no hay calificaciones

- Laboratorio No.11Documento5 páginasLaboratorio No.11dafnne solanoAún no hay calificaciones

- Práctica de Laboratorio 10Documento3 páginasPráctica de Laboratorio 10OSMAN ACOSTA MONTERROSAAún no hay calificaciones

- Guía 3 - MICROCONTROLADORESDocumento11 páginasGuía 3 - MICROCONTROLADORESDiego BelloAún no hay calificaciones

- Actividad 3 PLCDocumento13 páginasActividad 3 PLCELKIN FABIAN ACOSTA OJEDA100% (2)

- Practica 4 VDHLDocumento7 páginasPractica 4 VDHLManuel GonzalezAún no hay calificaciones

- Practica 3 Frecuencimetro Con Displays MultiplexadoDocumento3 páginasPractica 3 Frecuencimetro Con Displays MultiplexadoOrlando Jose MUjica VasquezAún no hay calificaciones

- Flowtran Cape OpenDocumento65 páginasFlowtran Cape OpenDanna Elbbort GarfiasAún no hay calificaciones

- Guia de Aprendizaje 2 v2Documento9 páginasGuia de Aprendizaje 2 v2oscarfppAún no hay calificaciones

- PORTAFOLIOT1 ÜriarteGómezAlan Fundamentos de Programacion PDFDocumento24 páginasPORTAFOLIOT1 ÜriarteGómezAlan Fundamentos de Programacion PDFALAN URIARTE GÓMEZAún no hay calificaciones

- Practica 1Documento13 páginasPractica 1Mary Cecilia Tapia FernandezAún no hay calificaciones

- TR1 Vélasquez Soto JairoDocumento11 páginasTR1 Vélasquez Soto JairoJairo VelásquezAún no hay calificaciones

- Lab 2 Procesamiento de Bioseñal-202Documento18 páginasLab 2 Procesamiento de Bioseñal-202Laura FlorezAún no hay calificaciones

- TesisDocumento19 páginasTesisjontorres2017Aún no hay calificaciones

- Manual Proceso Ensamblado y LigadoDocumento17 páginasManual Proceso Ensamblado y LigadoJOSE ALFREDO AMARO OLAYAAún no hay calificaciones

- Cad Electronico TR1Documento11 páginasCad Electronico TR1Jean Pierre ZevallosAún no hay calificaciones

- Un 2020Documento6 páginasUn 2020Daniel ArceAún no hay calificaciones

- Mecatrónica AlgoritmosDocumento5 páginasMecatrónica AlgoritmosNkd SDQAún no hay calificaciones

- Instrumentación electrónica aplicada: Prácticas de laboratorioDe EverandInstrumentación electrónica aplicada: Prácticas de laboratorioCalificación: 3.5 de 5 estrellas3.5/5 (7)

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Manual de laboratorio de estructurasDe EverandManual de laboratorio de estructurasAún no hay calificaciones

- Examen SubestacionesDocumento5 páginasExamen Subestacionesjesus antonioAún no hay calificaciones

- Pruebas A TransformadoresDocumento15 páginasPruebas A Transformadoresjesus antonioAún no hay calificaciones

- Universidad Juarez Autonoma de Tabasco: AlumnoDocumento2 páginasUniversidad Juarez Autonoma de Tabasco: Alumnojesus antonioAún no hay calificaciones

- Sistema MRA Con PID JahmDocumento4 páginasSistema MRA Con PID Jahmjesus antonioAún no hay calificaciones

- Partes Del TransformadorDocumento29 páginasPartes Del Transformadorjesus antonioAún no hay calificaciones

- 5 Sistemas de Variables de Estado Simulado - JesusDocumento12 páginas5 Sistemas de Variables de Estado Simulado - Jesusjesus antonioAún no hay calificaciones

- Tira MateriaDocumento1 páginaTira MateriaDaniel MartinezAún no hay calificaciones

- 4 - Control de Fase Con TriacDocumento4 páginas4 - Control de Fase Con Triacjesus antonioAún no hay calificaciones

- 9 OptoacopladorDocumento6 páginas9 Optoacopladorjesus antonioAún no hay calificaciones

- 3-Control de Corriente Encendido-Apagado en CaDocumento7 páginas3-Control de Corriente Encendido-Apagado en Cajesus antonioAún no hay calificaciones

- 6-Identificacion de Polaridad y Regulacion de Un TransformadorDocumento4 páginas6-Identificacion de Polaridad y Regulacion de Un Transformadorjesus antonioAún no hay calificaciones

- 06.aplicación Del MultiplexorDocumento7 páginas06.aplicación Del Multiplexorjesus antonioAún no hay calificaciones

- 7 - Control de Velocidad de Un Motor Ac Con Un TriacDocumento6 páginas7 - Control de Velocidad de Un Motor Ac Con Un Triacjesus antonioAún no hay calificaciones

- 2 - Encendido y Apagado de Un SCR en CDDocumento4 páginas2 - Encendido y Apagado de Un SCR en CDjesus antonioAún no hay calificaciones

- Actividad 1 DERIVADASDocumento13 páginasActividad 1 DERIVADASjesus antonioAún no hay calificaciones

- C-Formato FSEC - 01Documento1 páginaC-Formato FSEC - 01jesus antonioAún no hay calificaciones

- Universidad Juárez Autónoma de TabascoDocumento1 páginaUniversidad Juárez Autónoma de Tabascojesus antonioAún no hay calificaciones

- Practica 1Documento12 páginasPractica 1jesus antonioAún no hay calificaciones

- Motor CD, Modelado Matematicamente y SimuladoDocumento9 páginasMotor CD, Modelado Matematicamente y Simuladojesus antonioAún no hay calificaciones

- Idoc - Pub - Capitulo 13 Autoinduccion e Induccion Solucionario de Circuitos Electricos Joseph A Edminister SchaumDocumento8 páginasIdoc - Pub - Capitulo 13 Autoinduccion e Induccion Solucionario de Circuitos Electricos Joseph A Edminister Schaumjesus antonioAún no hay calificaciones

- Principal 9Documento1 páginaPrincipal 9jesus antonioAún no hay calificaciones

- Práctica 8Documento8 páginasPráctica 8jesus antonioAún no hay calificaciones

- Actividad 2 - 3 Parcia - Metodo de DerivacionDocumento3 páginasActividad 2 - 3 Parcia - Metodo de Derivacionjesus antonioAún no hay calificaciones

- Acuse CitaDocumento2 páginasAcuse Citajesus antonioAún no hay calificaciones

- 04.implementacion de Un Sumador CompletoDocumento11 páginas04.implementacion de Un Sumador Completojesus antonioAún no hay calificaciones

- 02.implementacion de Circuitos A Partir de Expresiones BooleanasDocumento15 páginas02.implementacion de Circuitos A Partir de Expresiones Booleanasjesus antonioAún no hay calificaciones

- PortadasDocumento7 páginasPortadasjesus antonioAún no hay calificaciones

- 05.anexo CDocumento15 páginas05.anexo Cjesus antonioAún no hay calificaciones

- 06.anexo DDocumento15 páginas06.anexo Djesus antonioAún no hay calificaciones

- Antecedentes Teóricos Y de La Invest. Bloques Nutricionales - Trabajos - 69691969Documento1 páginaAntecedentes Teóricos Y de La Invest. Bloques Nutricionales - Trabajos - 69691969Emilio Pastora100% (1)

- Caso HyundaiDocumento2 páginasCaso HyundaiMarco ToroAún no hay calificaciones

- PANCREASDocumento41 páginasPANCREASPepe Bueno100% (1)

- LisztDocumento5 páginasLisztAndrés MartínezAún no hay calificaciones

- EMMcoc H21jo - Cuestionario 8Documento3 páginasEMMcoc H21jo - Cuestionario 8EMMcoc h21joAún no hay calificaciones

- El Evangelio para Los GentilesDocumento4 páginasEl Evangelio para Los GentilesRuben Monrroy CAún no hay calificaciones

- Informe de MejoraDocumento8 páginasInforme de MejoraJose HernandezAún no hay calificaciones

- Examen Bimestral Comunicación - 2do Año Lee I BimestreDocumento4 páginasExamen Bimestral Comunicación - 2do Año Lee I BimestreCristina Malpartida GuardiaAún no hay calificaciones

- TitulosDocumento2 páginasTitulosAndresz1Aún no hay calificaciones

- Cuestionario para El Estudio de EntomologíaDocumento4 páginasCuestionario para El Estudio de EntomologíaVeronica DitranoAún no hay calificaciones

- Caso Práctico La Bruixa D or (La Bruja de Oro)Documento7 páginasCaso Práctico La Bruixa D or (La Bruja de Oro)Luis García lopezAún no hay calificaciones

- Ebook Landing Page Optimization BlueCaribu PDFDocumento28 páginasEbook Landing Page Optimization BlueCaribu PDFRolandoAún no hay calificaciones

- 8 - STC1314-2017Documento12 páginas8 - STC1314-2017LAURA VALENTINA CASTRO SUÁREZAún no hay calificaciones

- Allanamiento de MoradaDocumento6 páginasAllanamiento de MoradaDannylitow Lopez50% (2)

- Obstrucción IntestinalDocumento14 páginasObstrucción IntestinalSandra CarreraAún no hay calificaciones

- La Ambigüedad Conceptual y Terminología de Los DDDocumento15 páginasLa Ambigüedad Conceptual y Terminología de Los DDandreAún no hay calificaciones

- SESION DE MAT DENTRO Y FUERA de AbrilDocumento9 páginasSESION DE MAT DENTRO Y FUERA de AbrilLuisG.SaraviaAún no hay calificaciones

- Fijacion de MuestrasDocumento8 páginasFijacion de MuestrasSabina MelloAún no hay calificaciones

- Expediente 7491 2020 10 JRDocumento25 páginasExpediente 7491 2020 10 JRRedaccion La Ley - Perú100% (1)

- Prueba Bimestral de Estadística 6° 2020 Primer PeriodoDocumento2 páginasPrueba Bimestral de Estadística 6° 2020 Primer PeriodoYULI CANTOR.100% (1)

- Una Mirada Psicoeducativa Al Aprendizaje - Qué Sabemos y Hacia Dónde VamosDocumento17 páginasUna Mirada Psicoeducativa Al Aprendizaje - Qué Sabemos y Hacia Dónde VamosaliciardgAún no hay calificaciones

- Guia de Medidas de Artefactos SanitariosDocumento11 páginasGuia de Medidas de Artefactos SanitariosHector MoyaAún no hay calificaciones

- PerfilesDocumento15 páginasPerfilesjuanjuvinaoAún no hay calificaciones

- NotificacionRezagosPO - 800183221 - 2054 COLFONDOSDocumento3 páginasNotificacionRezagosPO - 800183221 - 2054 COLFONDOSRicardo Libranza100% (1)

- Anexo-A NUESTRO PADRE CREADOR TÚPAC AMARUDocumento3 páginasAnexo-A NUESTRO PADRE CREADOR TÚPAC AMARUabrahanmauriciosahuaAún no hay calificaciones

- Ultrasonografía VeterinariaDocumento187 páginasUltrasonografía VeterinariaDavid Noriega Bravo0% (1)

- Resumen Teoria Contemporanea de La RestauracionDocumento17 páginasResumen Teoria Contemporanea de La RestauracionDiego Lindo ChumbesAún no hay calificaciones

- Agrietamiento en SoldadurasDocumento18 páginasAgrietamiento en Soldadurashicham lazcaniAún no hay calificaciones

- Organigrama Septiembre 14 de 2020Documento17 páginasOrganigrama Septiembre 14 de 2020Andrea Hernández MAún no hay calificaciones

- 5tos . - TEMAS CUARENTENADocumento8 páginas5tos . - TEMAS CUARENTENAmarthaAún no hay calificaciones