Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Informe PR Ctica 04 Comportamiento Din Mico y Est Tico de Circuitos CMOS

Cargado por

Ernesto FerreiraTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Informe PR Ctica 04 Comportamiento Din Mico y Est Tico de Circuitos CMOS

Cargado por

Ernesto FerreiraCopyright:

Formatos disponibles

1

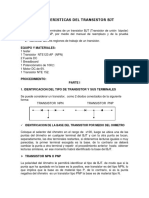

informe práctica 04: Comportamiento dinámico y

estático de circuitos CMOS.

Resumen—El siguiente informe muestra los resultados obteni- referencia. [1] En la figura se observa las diferentes confi-

dos al trabajar con configuraciones para encontrar el compor- guraciones de las OR y AND de los dos tipos de dispositivo.

tamiento de compuertas NAND y NOR a partir del integrado [1]

4007.

Index Terms—Nmos,cmos , oscilador vco,oscilador ,Negador.

O BJETIVO .

Comprobar el funcionamientos de compuertas lógicas a

partir de implementación discreta a partir del circuito integrado

4007 en configuraciones and, or , nand y nor.

I. I NTRODUCCI ÓN

Dentro de las tecnologı́as de compuertas lógicas se en-

cuentran configuraciones que trabajan dependiendo de los

valores lógicos que se requieran dentro de parámetros de

entrada y las condiciones de salida. En este caso se analiza el

comportamiento de las compuertas NAND y NOR sobre las

impedancias de entrada y la señal de salida de cada integrado.

Figura 1. NOR y NAND [1]

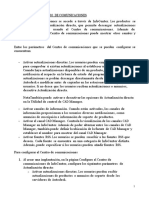

II. M ARCO T E ÓRICO .

En la siguiente se mencionara el comportamiento de la

compuertas NAND y NOR, partiendo del dibujo y disposicion

de los transistores, y el concepto general de inversor, es II-A. Compuerta de Transmisión

escencial para el diseño digital, de estas compuertas. [1]

Se utiliza dos configuraciones junto con PMOS y NMOS,

Cuadro I la unica diferencia se presenta su conexion en serie o paralelo.

VALORES L ÓGICOS DE LA COMPUERTA NAND [1]

[1]

NAND A B

1 0 0

1 0 1

1 1 0

0 1 1

Cuadro II

VALORES L ÓGICOS DE LA COMPUERTA NOR [1]

NOR A B

1 0 0

0 0 1

0 1 0

0 1 1

Por el laboratorio anterior, tenemos en cuenta el compor-

tamiento de los transistores PMOS Y NMOS, donde a una Figura 2. Compuerta de transmisión [1]

estimulacion positiva en la compuerta los transistores tipo N

funcionan como interruptor cerrado con tierra, y para el tipo

P seria un interruptor abierto. [1] La configuración en paralelo es la mas usada, en la cual

Para el diseño de las compuertas, tomamos configuraciones consiste colocar un transistor P y N conectados a la mismas

OR y AND, tanto para el PMOS (Mejores para drenar la entrada y la misma salida, teniendo una ventaja, es eliminar

corriente de la fuente de alimentacion) y NMOS, para la los voltajes de umbral sobre la señal de salida. [1]

2

III. R ESULTADOS , PROCEDIMIENTO ,C ÁLCULOS Y

S IMULACIONES .

III-A. Compuerta NAND de 2 entradas.

Para la realización del montaje con la compuerta NAND,

se implemento el circuito que se muestra en la figura 5(a). El

proceso de obtención de resultados se dividió en dos partes. La

primera corresponde a la medición de caracterı́sticas estáticas

o potencia en DC, y la segunda corresponde a caracterı́sticas

dinámicas de la compuerta, o potencia en AC. Para la primera

parte se conectaron fuentes DC en las entradas para establecer

los niveles lógicos en cada una de ellas y se evidenciaban los

resultados a la salida. Con esto se obtuvo la siguiente tabla

(a) Ciruito utilizado para la simulación de la compuerta NAND.

En esta gráfica se observa el cambio de estado alto a bajo

dentro de los valores de estado bajo de la entrada uno, para lo

que entonces se muestra en otra gráfica en que momento entra

en estado alto según las variaciones de la entrada dos a una

frecuencia de 5kHz se observa como cuando las variaciones

de la segunda entrada son positivas, se hace negativa la

salida, confirmando que solo cuando ambas entradas de la

configuración NAND son positivas con una salida en estado

bajo, ası́ afirmando que esta en correcto funcionamiento.

Figura 3. Tabla de variación de tensión y potencia para compuerta NAND

III-B. Compuerta NOR de 2 entradas.

En la figura 5(b) se puede ver el circuito utilizado para

la compuerta NOR esta se implemento con 4 transistores

Luego para determinar la potencia dinámica se conectó un mosfet. Para realizar la simulación se utiliza las siguiente

condensador a la salida de la compuerta y se coloco en la combinaciones 0,1 1,0 1,1 en las entradas A y B .

entrada una forma de onda cuadrada de la misma amplitud con

la que se encendı́a el dispositivo. El condensador empleado

era de 100nF. Para la prueba de las entradas de la compuerta

NAND con el fin de observar la salida, se aplica una entrada

a un valor de 500Hz y la segunda entrada a un valor de 5kHz

para observar el correcto funcionamiento de la compuerta

implementada. Aplicando la relación para la potencia dinámica

obteniendo la siguiente señal.

(b) Ciruito utilizado para la simulación de la com-

puerta NOR.

Para el estado estático, se aplica sobre una resistencia de

10k la salida de la compuerta NOR, con una alimentación

fija en la entrada para poder observar los valores de potencia

consumida; a continuación se presenta la tabla con los valores

de voltaje de nivel alto tomados y las potencias de consumo

Figura 4. Señal de salida para configuración NAND calculadas:

3

Figura 9. Formula de variación ESTATICA de tensión y potencia para

compuerta NOR

III-C. Compuerta de transmisión.

Para la simulación de la compuerta de trasmisión se utilizan

dos transistores mos uno N y otro P, Al transistor tipo N se

le aplica una señal de voltaje de 5V y en el gate del tipo P

Figura 5. Tabla de variación ESTATICA de tensión y potencia para compuerta un valor negado 0V. En la entrada (In) se utiliza una señal

NOR cuadrada con una amplitud de 5V y en la salida (Out ) se

puede ver que es la misma de la entrada.

Con los datos medidos, podemos afirmar sobre las varia-

ciones de los tiempos de respuesta que tienden a aumentar

a medida que aumenta la tensión de alimentación. Con res-

pecto a la potencia dinámica se tiene que calcular usando la

frecuencia aplicada, junto con la capacitancia y la fuente de

alimentación, se obtuvo como resultado:

Figura 6. Señal de salida para configuración NOR

(a) Ciruito utilizado para la simulación de la compuerta de trans-

misión

Figura 7. Tabla de variación DINÁMICA de tensión y potencia para

compuerta NOR

Con los datos medidos,podemos afirmar sobre las variacio-

nes de los tiempos de respuesta que tienden a aumentar a me-

dida que aumenta la tensión de alimentación. Con respecto a (b) Resultados obtenidos al aplicar un pulso cuadrado con un valor de

la potencia dinámica se tiene que calcular usando la frecuencia 5V

aplicada, junto con la capacitancia y la fuente de alimentación, Figura 10. Sumulación y resultados para la simulación de la compuerta de

mediante las siguientes formulas podemos dar respuesta a la transmisión.

tabla de variación estática o dinámica.

Se construye entonces la tabla de los valores medidos de

tiempos con relación a los cambios que ocurran en la alimen-

tación de los transistores. Se encuentran con tiempos de subida

y bajada bastante variables, pero no con un patrón definible

Figura 8. Fomula para variación DINÁMICA de tensión y potencia para dentro de los parámetros que se poseen. En relación con los

compuerta NOR valores de potencia dinámica, se tiene un consumo creciente

4

a medida que se aumenta la alimentación como en casos

anteriores y dado de que siguen dependiendo de la frecuencia,

se tiene que también aumenta la potencia de perdida de este

tipo a mayores tiempos de operación. Los valores de potencia

calculados que se tienen son de 1,25mW(5V), 1,8mW(6V),

2,45mW(7V), 3,2mW(8V), 4mW(9V) y 5mW(10V) en este

ensayo. Para el estado estático, se usó la resistencia de 10k y

se consignan los datos de la potencia que se calcula dentro de

la siguiente tabla:

Figura 11. Tabla de variación de tensión y potencia para compuerta de

transmisión

IV. CONCLUSIONES

En el laboratorio se logro evidenciar, que los tiempo de

subida y bajada se ven afectados por la disipación de

potencia generada por la cantidad de tensión sometida

a los dispositivos, ademas de generar perdidas por la

conmutación.

Los dispositivos evidencias efectos capacitivos generados

por la variación creciente de frecuencia a los que puede

verse sometido.

La compuerta de transmisión otorga mas eficiencia de

respuesta a los circuitos de conmutación, ya que se

evidencia disminución del efecto del voltaje umbral al

circular la señal digital por el transistor. disminuyendo

la atenuación de la señal.

R EFERENCIAS

[1] Adel S. Sedra, Kenneth C.Smith, Microelectronic Circuits, 5ta Edición,

Oxford University, 2004, páginas 650-658.

También podría gustarte

- Armónicas en Sistemas Eléctricos IndustrialesDe EverandArmónicas en Sistemas Eléctricos IndustrialesCalificación: 4.5 de 5 estrellas4.5/5 (12)

- Guia Laboratorio #5 Juan BuilesDocumento2 páginasGuia Laboratorio #5 Juan BuilesEl Pinche PastelAún no hay calificaciones

- Preinforme 4 TecnicasDocumento4 páginasPreinforme 4 TecnicasDario ClavijoAún no hay calificaciones

- Informe I Compuertas LogicasDocumento9 páginasInforme I Compuertas LogicasCristian GomezAún no hay calificaciones

- LOGICA DIGITAL Compuertas NAND, NOR, XOR y XNOR PDFDocumento6 páginasLOGICA DIGITAL Compuertas NAND, NOR, XOR y XNOR PDFGisel AngieAún no hay calificaciones

- Compuertas LogicasDocumento7 páginasCompuertas Logicaseli saAún no hay calificaciones

- Práctica 2Documento4 páginasPráctica 2Laddy Viviana ParraAún no hay calificaciones

- PRACTICA 4 - CIL - ArredondoDelgadoDocumento6 páginasPRACTICA 4 - CIL - ArredondoDelgadoDiego Armando ArredondoAún no hay calificaciones

- GUIA LABORATORIO #5 Juan BuilesDocumento2 páginasGUIA LABORATORIO #5 Juan BuilesEl Pinche PastelAún no hay calificaciones

- APUNTE - 10 - Polarización de CD de Los BJTDocumento19 páginasAPUNTE - 10 - Polarización de CD de Los BJTErik EstradaAún no hay calificaciones

- Informe Laboratorio 4Documento7 páginasInforme Laboratorio 4Cristhian PinzonAún no hay calificaciones

- Guia 1. Compuertas LógicasDocumento5 páginasGuia 1. Compuertas LógicasDiegoErasoAún no hay calificaciones

- Informe - Compuertas LógicasDocumento6 páginasInforme - Compuertas LógicasLuis Alejandro Alvarez RengifoAún no hay calificaciones

- Amplificador Diferencial JFET and CompueDocumento12 páginasAmplificador Diferencial JFET and CompueEmily JulianaAún no hay calificaciones

- Par Diferencial Con Carga PasivaDocumento5 páginasPar Diferencial Con Carga PasivaFelipe SimmondsAún no hay calificaciones

- Laboratorio 3 - FundamentosDocumento6 páginasLaboratorio 3 - FundamentosJeffersonAún no hay calificaciones

- Probador Punta LogicaDocumento7 páginasProbador Punta LogicaErik CruzAún no hay calificaciones

- Lab04 TocciDocumento6 páginasLab04 TocciRobin Téllez MendozaAún no hay calificaciones

- Guia 1 Compuertas Logicas 1Documento5 páginasGuia 1 Compuertas Logicas 1Seykarim Rafael Mestre ZalabataAún no hay calificaciones

- Informe Final Compuertas TTL y CmosDocumento6 páginasInforme Final Compuertas TTL y CmoskennetAún no hay calificaciones

- Pre Informe PR Ctica 3 Circuitos de RFDocumento6 páginasPre Informe PR Ctica 3 Circuitos de RFALVAROCELISLOPESAún no hay calificaciones

- Laboratirio de AnalogaDocumento42 páginasLaboratirio de AnalogasebastianAún no hay calificaciones

- Trabajo Inv 2Documento12 páginasTrabajo Inv 2Fátima SerranoAún no hay calificaciones

- Laboratorio 2 Cabrales Romero SuárezDocumento7 páginasLaboratorio 2 Cabrales Romero SuárezARLEY JOSE SUAREZ MERCADOAún no hay calificaciones

- Conversor-Da AdDocumento4 páginasConversor-Da AdJhonatan Fernando Avella AvilaAún no hay calificaciones

- Informe Practica 4 Diseño Electronico 1Documento4 páginasInforme Practica 4 Diseño Electronico 1Luis UrazánAún no hay calificaciones

- Informe #3: Caracterización de Transistores BJT y Análisis de Circuitos Con Transistores BJTDocumento14 páginasInforme #3: Caracterización de Transistores BJT y Análisis de Circuitos Con Transistores BJTKEVIN NI?O TEJADAAún no hay calificaciones

- Final 2 Electrónicos 2 UnmsmDocumento3 páginasFinal 2 Electrónicos 2 UnmsmSteven ZacariasAún no hay calificaciones

- Experiment o 2Documento4 páginasExperiment o 2William MarínAún no hay calificaciones

- Practica ADCDocumento9 páginasPractica ADCFernando PérezAún no hay calificaciones

- Inversores de Voltaje - Práctica de LaboratorioDocumento8 páginasInversores de Voltaje - Práctica de LaboratorioIván HerreraAún no hay calificaciones

- Semana 7 y 8 Polarizacion de Transistores y Aplicaciones 022017Documento48 páginasSemana 7 y 8 Polarizacion de Transistores y Aplicaciones 022017Fer' OrtizAún no hay calificaciones

- Estabilizacion de La Polarizacion BJT PDFDocumento24 páginasEstabilizacion de La Polarizacion BJT PDFTAMARA CONSTANZA MORALES NUNEZAún no hay calificaciones

- Wa0002 PDFDocumento13 páginasWa0002 PDFJimena Encinas López0% (1)

- Motor Paso ApasoDocumento6 páginasMotor Paso ApasoruthvirginiaAún no hay calificaciones

- Lab 4Documento11 páginasLab 4Mauricio RodríguezAún no hay calificaciones

- Informe 11 Anal Gicas PMDocumento3 páginasInforme 11 Anal Gicas PMLaura GonzalezAún no hay calificaciones

- Aplicacion de Las Puertas UniversalesDocumento8 páginasAplicacion de Las Puertas UniversalesJM LugercocasAún no hay calificaciones

- TP1 Sistemas Numeracion y Algebra 2024Documento5 páginasTP1 Sistemas Numeracion y Algebra 2024Magali GutierrezAún no hay calificaciones

- BJT Como Amplificador de Pequeña SeñalDocumento5 páginasBJT Como Amplificador de Pequeña SeñalFrancisco ChanaAún no hay calificaciones

- Diseno2 2150651 O1BDocumento4 páginasDiseno2 2150651 O1BPablo GomezAún no hay calificaciones

- Laboratorio 04 BiestablesDocumento26 páginasLaboratorio 04 BiestablesJorddy Peralta IruriAún no hay calificaciones

- Electronica Digital Informe1Documento2 páginasElectronica Digital Informe1Alejandro Zabala CamachoAún no hay calificaciones

- Rectificadores Controlador Carga ResistivaDocumento9 páginasRectificadores Controlador Carga ResistivaAlisson PedrazaAún no hay calificaciones

- Informe Proyecto Final Electronica IIDocumento10 páginasInforme Proyecto Final Electronica IIJorge TrujilloAún no hay calificaciones

- E A III T P N 7 - : Amplificador de PotenciaDocumento7 páginasE A III T P N 7 - : Amplificador de PotenciaLuciano MichalikAún no hay calificaciones

- Manual de Laboratorio de Logica Digital 1 Carlos GuzmanDocumento28 páginasManual de Laboratorio de Logica Digital 1 Carlos Guzmanjeison ariasAún no hay calificaciones

- Ibf-1009 Colin PR 2paDocumento7 páginasIbf-1009 Colin PR 2paRodrigo ColinAún no hay calificaciones

- BJT Colector Comun PNPDocumento21 páginasBJT Colector Comun PNPMaxwell SDAún no hay calificaciones

- La Aplicación de Capacitores en Circuitos Amplificadores Operacionales Como Integrador y DiferenciadorDocumento5 páginasLa Aplicación de Capacitores en Circuitos Amplificadores Operacionales Como Integrador y DiferenciadorYair Sebastian Herrera VegaAún no hay calificaciones

- Caracteristicas de Las Compuertas TTL y CmosDocumento6 páginasCaracteristicas de Las Compuertas TTL y CmosMario Asuaje100% (1)

- Guia de TransistoresDocumento12 páginasGuia de Transistoresebevm0% (1)

- Notas de ClaseDocumento15 páginasNotas de ClaseJackeline MariñoAún no hay calificaciones

- Lab 4 2022-29-11Documento12 páginasLab 4 2022-29-11Mauricio RodríguezAún no hay calificaciones

- Practica Ii.-Transistor BJT Dispositivos Electronicos: Liliana Del Rio GamboaDocumento14 páginasPractica Ii.-Transistor BJT Dispositivos Electronicos: Liliana Del Rio GamboaDaniel MartinezAún no hay calificaciones

- Informe Segundo CorteDocumento28 páginasInforme Segundo CorteLuis MontañoAún no hay calificaciones

- Laboratorio Nro. 4-Polarizcion de Un TransistorDocumento4 páginasLaboratorio Nro. 4-Polarizcion de Un TransistorRichard L TorresAún no hay calificaciones

- Resumen 4Documento12 páginasResumen 4HugoGJimenezAún no hay calificaciones

- Practica Introductoria DCCDocumento5 páginasPractica Introductoria DCCcesargarciacg7Aún no hay calificaciones

- Certamen 2 SEP1 2021Documento3 páginasCertamen 2 SEP1 2021Francisco MorenoAún no hay calificaciones

- PR Ctica 4 Rectificadores No Controlados Trif SicosDocumento5 páginasPR Ctica 4 Rectificadores No Controlados Trif SicosErnesto FerreiraAún no hay calificaciones

- SONET y SDHDocumento3 páginasSONET y SDHErnesto FerreiraAún no hay calificaciones

- Informe I Car Cteristicas de Transistores FETs y MosfetsDocumento5 páginasInforme I Car Cteristicas de Transistores FETs y MosfetsErnesto FerreiraAún no hay calificaciones

- Informe PR Ctica 03 Inversores NMOS y CMOSDocumento7 páginasInforme PR Ctica 03 Inversores NMOS y CMOSErnesto FerreiraAún no hay calificaciones

- Tarea 1 An Lisis de Circuitos Magn Ticos y TransformadoresDocumento2 páginasTarea 1 An Lisis de Circuitos Magn Ticos y TransformadoresErnesto FerreiraAún no hay calificaciones

- Informe II Car Cteristicas Del MosfetDocumento4 páginasInforme II Car Cteristicas Del MosfetErnesto FerreiraAún no hay calificaciones

- Disipaci N de Calor en Dispositivos SemiconductoresDocumento3 páginasDisipaci N de Calor en Dispositivos SemiconductoresErnesto FerreiraAún no hay calificaciones

- PR Ctica 3 Rectificador Monof Sico Con Carga RLDocumento10 páginasPR Ctica 3 Rectificador Monof Sico Con Carga RLErnesto FerreiraAún no hay calificaciones

- C Digos de LineaDocumento4 páginasC Digos de LineaErnesto FerreiraAún no hay calificaciones

- Implementacion Proyecto en FPGADocumento8 páginasImplementacion Proyecto en FPGAErnesto FerreiraAún no hay calificaciones

- Manejo de DockerDocumento2 páginasManejo de DockerErnesto FerreiraAún no hay calificaciones

- Configuración de Proyecto Con Webpack y BabelDocumento32 páginasConfiguración de Proyecto Con Webpack y BabelErnesto FerreiraAún no hay calificaciones

- Taller No 3 Algebraic Design MethodsDocumento4 páginasTaller No 3 Algebraic Design MethodsErnesto FerreiraAún no hay calificaciones

- Installacion DockerDocumento2 páginasInstallacion DockerErnesto FerreiraAún no hay calificaciones

- 3 - CSS+JSDocumento80 páginas3 - CSS+JSErnesto FerreiraAún no hay calificaciones

- CAP 04-Drenajes Tubulares (Tubos)Documento10 páginasCAP 04-Drenajes Tubulares (Tubos)carlosAún no hay calificaciones

- Nota Información CenagasDocumento4 páginasNota Información CenagasAbel ContrerasAún no hay calificaciones

- Método de Instalación RICKPACTOR WINDOWSDocumento7 páginasMétodo de Instalación RICKPACTOR WINDOWSWolffy PokemonAún no hay calificaciones

- Ejes y RodamientosDocumento46 páginasEjes y RodamientosYoel A UmañaAún no hay calificaciones

- Manual AutoCAD Avanzado 2009-I PDFDocumento45 páginasManual AutoCAD Avanzado 2009-I PDFcuervocrdAún no hay calificaciones

- Reglamento General AlumnosDocumento14 páginasReglamento General AlumnosLicenciaturas UCSEAún no hay calificaciones

- Manual de Informatica - Trucos para Aprovechar Al Maximo El PCDocumento7 páginasManual de Informatica - Trucos para Aprovechar Al Maximo El PCjavier.4evermlcAún no hay calificaciones

- Taller Iv - Camila Sánchez PalmaDocumento3 páginasTaller Iv - Camila Sánchez PalmaCamila SánchezAún no hay calificaciones

- Indicadores de Desempeño y Medicion de ProductividadDocumento3 páginasIndicadores de Desempeño y Medicion de ProductividadChemas09Aún no hay calificaciones

- Practica 3 BDDocumento4 páginasPractica 3 BDAxel Olaf SánchezAún no hay calificaciones

- Exp 7 Act. 1 Tercer GradoDocumento11 páginasExp 7 Act. 1 Tercer GradoRonald Jara QuispeAún no hay calificaciones

- Matematica 6Documento187 páginasMatematica 6Jorge Tilleria Zuñiga100% (1)

- Guia CRM PDFDocumento25 páginasGuia CRM PDFnickaxxxiAún no hay calificaciones

- Guía de Actividades y Rúbrica de Evaluación - Unidad 3 - Fase 5 - Evaluación de Resultados Del Social Media PlanDocumento7 páginasGuía de Actividades y Rúbrica de Evaluación - Unidad 3 - Fase 5 - Evaluación de Resultados Del Social Media PlanYeimy Xiomara Valderrama PuertoAún no hay calificaciones

- T024Métodos de Presentación Datos-Luis PabloHernándezMatzirDocumento7 páginasT024Métodos de Presentación Datos-Luis PabloHernándezMatzirLuis Pablo Hern�ndez MatzirAún no hay calificaciones

- Nuevas Funcionalidades de 12cDocumento9 páginasNuevas Funcionalidades de 12ckamuniasAún no hay calificaciones

- Cuestionario 2 Seguimiento Intermedio 1 - Paralelo C - Revisión Del IntentoDocumento4 páginasCuestionario 2 Seguimiento Intermedio 1 - Paralelo C - Revisión Del IntentoCARLOS GERMAN ORTEGA QUISHPEAún no hay calificaciones

- Esp. Tec. LosaDocumento6 páginasEsp. Tec. LosaAnahi MendizabalAún no hay calificaciones

- Trabajo de RubioDocumento11 páginasTrabajo de RubioAstrid JiménezAún no hay calificaciones

- Sistema ContableDocumento3 páginasSistema ContableGeral prudencioAún no hay calificaciones

- Sesión 1 - Conceptos - Generales PDFDocumento25 páginasSesión 1 - Conceptos - Generales PDFJhulia Lua HerbayAún no hay calificaciones

- Actividad 8 Outsourcing y KaizenDocumento10 páginasActividad 8 Outsourcing y KaizenLeydi MoralesAún no hay calificaciones

- Practica 1 - Industrial Automation PDFDocumento2 páginasPractica 1 - Industrial Automation PDFMisael Reynalte Jara100% (1)

- Tensei Ouji 22-26Documento123 páginasTensei Ouji 22-26Yuel YuAún no hay calificaciones

- 2023 IngIndus InformaticaI HojaDeRuta Actualizada8MayDocumento3 páginas2023 IngIndus InformaticaI HojaDeRuta Actualizada8MaymaxxkyllerAún no hay calificaciones

- S11 y S12 Tarea Académica 2 (Formato Oficial UTP) 2021 MarzoDocumento9 páginasS11 y S12 Tarea Académica 2 (Formato Oficial UTP) 2021 MarzoAndrea CrispinAún no hay calificaciones

- Facturas - Boletas PLANILLA-REPARTO00002948Documento9 páginasFacturas - Boletas PLANILLA-REPARTO00002948Anton LuisAún no hay calificaciones

- PA 02 Fundamentos ProgramaciónDocumento2 páginasPA 02 Fundamentos ProgramaciónMatematica Fisica EstadisticaAún no hay calificaciones

- Modelo CobitDocumento2 páginasModelo CobitedderAún no hay calificaciones

- Examen 2Documento2 páginasExamen 2Daniel Enrique Jimenez Paiva100% (1)