Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Práctica 2

Cargado por

Laddy Viviana ParraDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Práctica 2

Cargado por

Laddy Viviana ParraCopyright:

Formatos disponibles

1

PRÁCTICA 2: COMPUERTAS BÁSICAS

Departamento de Ingenierı́a Eléctrica, Electrónica y Computación

Universidad Nacional De Colombia - Sede Manizales

Docente: Jaime Enrique Arango

Sistemas Digitales

Semestre 2017-II

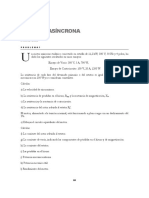

Abstract—In this lab the students will strengthen their IV. M ARCO TE ÓRICO

concepts of logic gates, Boolean expressions, truth tables

A. Transistor de Unión Bipolar

and simulation of circuits.

El transistor de unión bipolar (Bipolar Junction

Compuertas lógicas, expresiones booleanas, tabla de Transistor BJT), es un dispositivo electrónico de

verdad. estado sólido consistente en dos uniones de materiales

semiconductor PN muy cercanas entre sı́, que permite

I. I NTRODUCCI ÓN controlar el paso de la corriente a través de sus

Se denomina sistema combinacional a todo sistema terminales. La denominación de bipolar se debe a que

digital en el que sus salidas dependen exclusivamente la conducción tiene lugar gracias al desplazamiento

del valor de sus entradas en un momento dado, sin de portadores de dos polaridades (huecos positivos

que intervengan en ningún caso estados anteriores de y electrones negativos), y son de gran utilidad en

las entradas o de las salidas. Las funciones booleanas gran número de aplicaciones; pero tienen ciertos

usadas para estos sistemas son: OR, AND, NAND, inconvenientes, entre ellos su impedancia de entrada

XOR, etc. Cada función se puede representar en una bastante baja.

tabla de verdad.

Los transistores bipolares son los transistores más

En esta práctica se desarrollarán conceptos básicos conocidos y se usan generalmente en electrónica

sobre compuertas lógicas y su combinación para formar analógica aunque también en algunas aplicaciones de

funciones lógicas. electrónica digital, como la tecnologı́a TTL.

II. O BJETIVOS Un transistor de unión bipolar está formado por dos

• Identificar distintas compuertas lógicas y sus Uniones PN en un solo cristal semiconductor, separados

respectivas tablas de verdad. por una región muy estrecha. De esta manera quedan

formadas tres regiones:

• Conocer la implementación de compuertas lógicas

usando transistores. • Emisor, que se diferencia de las otras dos por

estar fuertemente dopada, comportándose como

• Adquirir habilidades básicas para el diseño y un metal. Su nombre se debe a que esta terminal

simulación de circuitos digitales. funciona como emisor de portadores de carga.

• Base, la intermedia, muy estrecha, que separa el

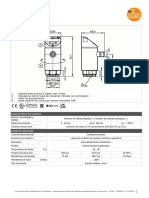

III. M ATERIALES emisor del colector.

• 13 Transistores 2N2222 o 2N3904.

• 9 Resistencias de 1kΩ • Colector, es el receptor de la carga proveniente del

• 6 Resistencias de 10kΩ. emisor que no se recombina en la base.

• 4 Resistencias de 330Ω.

• 7 Dip switch, interruptores o pulsadores. En la figura 1 se muestra el diagrama esquemático

• 4 Diodos led. de un transistor BJT NPN y PNP, donde B es la base,

2

C el colector y E el emisor.

Fig. 2. Sı́mbolo de la compuerta NOT

Fig. 1. Esquema del transistor BJT

1) Funcionamiento del transistor como interruptor:

El funcionamiento del transistor depende de la cantidad

de corriente que pase por su base. Cuando no pasa

corriente por la base, no puede pasar tampoco por sus

otros terminales; se dice entonces que el transistor está en

corte, es como si se tratara de un interruptor abierto. El

transistor está en saturación cuando existe una corriente

en la base; en ese caso se permite la circulación de

Fig. 3. Implementación de una compuerta NOT con transistores

corriente entre el colector y el emisor y el transistor se

comporta como si fuera un interruptor cerrado.

TABLE I

B. Compuertas Lógicas TABLA DE VERDAD DE LA COMPUERTA NOT

La lógica binaria tiene que ver con variables binarias A S

y con operaciones que toman un sentido lógico. La 0v

manipulación de información binaria se hace por 5v

circuitos lógicos que se denominan Compuertas lógicas.

Las compuertas son bloques de hardware que pro- B. Compuerta AND

ducen señales en binario 1 ó 0 cuando se satisfacen

los requisitos de entrada lógica. Cada compuerta tiene La compuerta AND es una compuerta lógica que

un sı́mbolo gráfico diferente y su operación puede implementa la conjunción lógica “y”, su sı́mbolo se

describirse por medio de una función algebraica. Las muestra en la figura 4.

relaciones entrada-salida de las variables binarias para

cada compuerta pueden representarse en una tabla de

verdad.

V. P ROCEDIMIENTO

A. Compuerta NOT

La compuerta NOT es una compuerta lógica digital

Fig. 4. Sı́mbolo de la compuerta AND

que implementa la negación lógica “no”, su sı́mbolo se

muestra en la figura 2.

En la figura 3 se muestra una forma de implementar En la figura 5 se muestra una forma de implementar

esta compuerta usando transistores. Se debe simular, esta compuerta usando transistores. Se debe simular,

realizar el montaje en protoboard usando una fuente realizar el montaje en protoboard usando una fuente

de 5v y completar su tabla de verdad, correspondiente de 5v y completar su tabla de verdad, correspondiente

al cuadro I, para ello se medirá el voltaje en el punto al cuadro II, para ello se medirá el voltaje en el punto

indicado cuando la entrada varı́a de acuerdo a la tabla. indicado cuando las entradas varı́an de acuerdo a la tabla.

3

Fig. 5. Implementación de una compuerta AND con transistores Fig. 7. Implementación de una compuerta OR con transistores

TABLE II

TABLA DE VERDAD DE LA COMPUERTA AND D. Compuerta NAND

A B S La compuerta NAND es una puerta lógica digital

0v 0v que implementa la conjunción lógica ”y” negada, su

0v 5v sı́mbolo se muestra en la figura 8.

5v 0v

5v 5v

C. Compuerta OR

La compuerta OR es una compuerta lógica digital

que implementa la disyunción lógica “o”, su sı́mbolo se Fig. 8. Sı́mbolo de la compuerta NAND

muestra en la figura 6.

En la figura 9 se muestra una forma de implementar

esta compuerta usando transistores. Se debe simular,

realizar el montaje en protoboard usando una fuente de

5v y completar su tabla de verdad, correspondiente al

cuadro IV, para ello se medirá el voltaje en el punto

indicado cuando las entradas varı́an de acuerdo a la tabla.

Fig. 6. Sı́mbolo de la compuerta OR

En la figura 7 se muestra una forma de implementar TABLE IV

TABLA DE VERDAD DE LA COMPUERTA NAND

esta compuerta usando transistores. Se debe simular,

realizar el montaje en protoboard usando una fuente de A B S

5v y completar su tabla de verdad, correspondiente al 0v 0v

cuadro III, para ello se medirá el voltaje en el punto 0v 5v

indicado cuando las entradas varı́an de acuerdo a la tabla. 5v 0v

5v 5v

TABLE III NOTA: para cada uno de los circuitos implementados

TABLA DE VERDAD DE LA COMPUERTA OR se debe agregar la etapa de visualización mostrada en

la figura 10, cuya base se conecta al punto donde se

A B S

midió el voltaje y corresponde a la salida del circuito.

0v 0v

0v 5v

5v 0v

5v 5v

4

Fig. 11. Simulación uno

Fig. 9. Implementación de una compuerta NAND con transistores

Fig. 10. Etapa de visualización

E. Circuitos Combinacionales

Fig. 12. Simulación dos

1) Se debe simular los circuitos de las figuras 11 y

12. De acuerdo a la simulación se debe deducir

la tabla de verdad para cada circuito y también su VI. C UESTIONARIO

respectiva función booleana.

1) Consultar las principales diferencias entre familias

2) Se debe simular las funciones booleana utilizando

TTL y CMOS.

VHDL, obtener las tablas de verdad y comparar

los resultados con los obtendios en el punto

2) Consultar Álgebra Booleana y sus principales

anterior.

postulados.

R EFERENCES

[1] http://www.virtual.unal.edu.co/cursos/ingenieria/

También podría gustarte

- GUIA - LAB - 01 DEP5101 Transistor BipolarDocumento13 páginasGUIA - LAB - 01 DEP5101 Transistor BipolarAlexander PintoAún no hay calificaciones

- Caracteristicas Tansistor BJTDocumento8 páginasCaracteristicas Tansistor BJTjaimeAún no hay calificaciones

- El Transistor Compuerta LogicaDocumento4 páginasEl Transistor Compuerta LogicaJoan MartínezAún no hay calificaciones

- Guia 6 y 7 Lab 022017Documento10 páginasGuia 6 y 7 Lab 022017Joel CordovaAún no hay calificaciones

- S6 Guia Lab03 Caracterización Del InversorDocumento6 páginasS6 Guia Lab03 Caracterización Del InversorLord KingAún no hay calificaciones

- Laboratorio 01 Curvas Del TransistorDocumento8 páginasLaboratorio 01 Curvas Del Transistorsharingan009Aún no hay calificaciones

- Circuito Lógicos Con TransistoresDocumento3 páginasCircuito Lógicos Con TransistoresDiana Catalina JaimesAún no hay calificaciones

- 21505-14 Componentes Electrónicos IIDocumento22 páginas21505-14 Componentes Electrónicos IITGAAún no hay calificaciones

- Guia 5Documento13 páginasGuia 5EdgarMartinezAún no hay calificaciones

- BJT Colector Comun PNPDocumento21 páginasBJT Colector Comun PNPMaxwell SDAún no hay calificaciones

- Curva Caracteristica Transistor InformeDocumento7 páginasCurva Caracteristica Transistor InformeMay FerAún no hay calificaciones

- Laboratorio 2 - Algebra Booleana (PACHECO)Documento11 páginasLaboratorio 2 - Algebra Booleana (PACHECO)Juan Esteban Pacheco LealAún no hay calificaciones

- E3 InformePrevioDocumento6 páginasE3 InformePreviomanuelAún no hay calificaciones

- Pre 1Documento4 páginasPre 1Manuel SanchezAún no hay calificaciones

- Práctica 1 - Familiarización Con TransistoresDocumento2 páginasPráctica 1 - Familiarización Con Transistoresjychus.jdacAún no hay calificaciones

- PRÁCTICA No 1 MDocumento19 páginasPRÁCTICA No 1 MTenuredMonkey 81Aún no hay calificaciones

- Ci PDFDocumento12 páginasCi PDFRAMOS GARCIA JENIFER YESENIAAún no hay calificaciones

- Informe Practica CompuertasDocumento6 páginasInforme Practica CompuertasGabriel CruzAún no hay calificaciones

- Informe - Compuertas LógicasDocumento6 páginasInforme - Compuertas LógicasLuis Alejandro Alvarez RengifoAún no hay calificaciones

- Curva Caracteristica Transistor InformeDocumento6 páginasCurva Caracteristica Transistor InformeMay FerAún no hay calificaciones

- Informe 7 MetrologiaDocumento5 páginasInforme 7 MetrologiaXavier SimbañaAún no hay calificaciones

- Control de Cerraduras Secuencial INFORMEDocumento22 páginasControl de Cerraduras Secuencial INFORMEFernando Quispe SerrudoAún no hay calificaciones

- Lab #1Documento1 páginaLab #1JhoelAún no hay calificaciones

- Laboratorio No 2Documento6 páginasLaboratorio No 2Juan Sebastian Yela VAún no hay calificaciones

- Practica 2 CorregidoDocumento22 páginasPractica 2 CorregidoJohn PorterAún no hay calificaciones

- Laboratorio 2 Cabrales Romero SuárezDocumento7 páginasLaboratorio 2 Cabrales Romero SuárezARLEY JOSE SUAREZ MERCADOAún no hay calificaciones

- Practica 4 Caracteristicas Del Transistor BJTDocumento6 páginasPractica 4 Caracteristicas Del Transistor BJTDiego VillaAún no hay calificaciones

- UntitledDocumento5 páginasUntitledYEFERSON EDUARDO URIBE BORREROAún no hay calificaciones

- Lab4 Etn1Documento4 páginasLab4 Etn1Joaquim MerloAún no hay calificaciones

- Amplificadores Operacionales.: 1. Introducci OnDocumento3 páginasAmplificadores Operacionales.: 1. Introducci OnJunior AlexanderAún no hay calificaciones

- Informe Previo 5 de Circuitos Electronicos 1Documento6 páginasInforme Previo 5 de Circuitos Electronicos 1LuisFernandoLevanoAún no hay calificaciones

- Guia 1 de Circuitos Electronicos II 2021Documento4 páginasGuia 1 de Circuitos Electronicos II 2021CanalDTodoUnPoco PCAún no hay calificaciones

- EPO - G2 - Características Del Transistor BJTDocumento7 páginasEPO - G2 - Características Del Transistor BJTDavid GodofredoAún no hay calificaciones

- LAB N°02 Electrónica Analógica y DigitalDocumento15 páginasLAB N°02 Electrónica Analógica y DigitalWanderley Felix Lopez QuirozAún no hay calificaciones

- Guia Laboratorio #5 Juan BuilesDocumento2 páginasGuia Laboratorio #5 Juan BuilesEl Pinche PastelAún no hay calificaciones

- Laboratorio 6Documento8 páginasLaboratorio 6PEDRO SIMON ESPARRAGOZA HERNANDEZAún no hay calificaciones

- Lab 2a 2023Documento8 páginasLab 2a 2023Frank Erick Espiritu SimonAún no hay calificaciones

- PRACTICA 4 - CIL - ArredondoDelgadoDocumento6 páginasPRACTICA 4 - CIL - ArredondoDelgadoDiego Armando ArredondoAún no hay calificaciones

- Previo 2 Electrónicos 2 UnmsmDocumento7 páginasPrevio 2 Electrónicos 2 UnmsmSteven ZacariasAún no hay calificaciones

- Amplificador Con Transistor BJTDocumento3 páginasAmplificador Con Transistor BJTArias D. CristianAún no hay calificaciones

- Amplificadores BJTDocumento11 páginasAmplificadores BJTJorge JoseAún no hay calificaciones

- Grupo 4 - Exp 3 - DE - Transistor Bipolar PNPDocumento14 páginasGrupo 4 - Exp 3 - DE - Transistor Bipolar PNPXavier Ccama Sara100% (1)

- Informe de Laboratorio de Compuertas LogicasDocumento13 páginasInforme de Laboratorio de Compuertas LogicasLuis RondoAún no hay calificaciones

- Informe Previo 2 de Laboratorio de Electronica 3 EE443Documento4 páginasInforme Previo 2 de Laboratorio de Electronica 3 EE443jose bryan miranda gameroAún no hay calificaciones

- Curvas de Transistor BipolarprevioDocumento19 páginasCurvas de Transistor BipolarpreviogeraldineAún no hay calificaciones

- Informe Final 5 HuablochoDocumento5 páginasInforme Final 5 Huablochofieeg4Aún no hay calificaciones

- Informe 1Documento6 páginasInforme 1Johinner Quenan MedinaAún no hay calificaciones

- Guia 2Documento10 páginasGuia 2Alejandro Tavera UsugaAún no hay calificaciones

- Transistor Conmutador - Practica LabDocumento6 páginasTransistor Conmutador - Practica LabvoltscribdAún no hay calificaciones

- Lab 5. NPN y PNPDocumento5 páginasLab 5. NPN y PNPpaula garciaAún no hay calificaciones

- Caracteristicas de Los Transistores BipolaresDocumento19 páginasCaracteristicas de Los Transistores BipolaresCristian Morales EspinozaAún no hay calificaciones

- Laboratorio 1 Instrumentación Ao Comparador 1S.2021Documento12 páginasLaboratorio 1 Instrumentación Ao Comparador 1S.2021Diego PinzonAún no hay calificaciones

- Experiment o 2Documento4 páginasExperiment o 2William MarínAún no hay calificaciones

- Laboratorio 2. Lógica Combinacional y Mapas de KarnaughtDocumento4 páginasLaboratorio 2. Lógica Combinacional y Mapas de KarnaughtAngie BarreraAún no hay calificaciones

- Laboratorio 03Documento11 páginasLaboratorio 03Pool Nolasco RamirezAún no hay calificaciones

- Luis Fernando Yucra Pancca INFORME-PREVIODocumento12 páginasLuis Fernando Yucra Pancca INFORME-PREVIOluis fernando yucra panccaAún no hay calificaciones

- Informe Previo 7 de Circuitos Electronicos 1 - Copia - Copia (Autoguardado)Documento5 páginasInforme Previo 7 de Circuitos Electronicos 1 - Copia - Copia (Autoguardado)LuisFernandoLevanoAún no hay calificaciones

- Informe 2Documento6 páginasInforme 2Daniel AcostaAún no hay calificaciones

- Armónicas en Sistemas Eléctricos IndustrialesDe EverandArmónicas en Sistemas Eléctricos IndustrialesCalificación: 4.5 de 5 estrellas4.5/5 (12)

- Estadistica PSU Datos No AgrupadosDocumento28 páginasEstadistica PSU Datos No AgrupadosFrancisco Saez TejosAún no hay calificaciones

- C Electrico 04Documento5 páginasC Electrico 04David BakerAún no hay calificaciones

- Condesadores Serie y ParaleloDocumento14 páginasCondesadores Serie y ParaleloLaddy Viviana ParraAún no hay calificaciones

- 1023 3366 1 SMDocumento12 páginas1023 3366 1 SMfabian andresAún no hay calificaciones

- Nivel 1-A Industrial UnalDocumento6 páginasNivel 1-A Industrial UnalLaddy Viviana ParraAún no hay calificaciones

- Unidad 3 ActividadesDocumento8 páginasUnidad 3 Actividadesernesto anguiano100% (1)

- Plan de Mantenimiento Semestral A Motor ElectricoDocumento1 páginaPlan de Mantenimiento Semestral A Motor Electricopedro castillo alvarezAún no hay calificaciones

- Inductancia e Inductancia MutuaDocumento14 páginasInductancia e Inductancia MutuaEsteban GonzalezAún no hay calificaciones

- Ejercicio 5Documento2 páginasEjercicio 5Jeyson CalderonAún no hay calificaciones

- Tarea Examen FinalDocumento11 páginasTarea Examen FinalEDWIN MOLLINEDO VELIZAún no hay calificaciones

- Cómo Funciona El Equipo IonizadorDocumento5 páginasCómo Funciona El Equipo IonizadorMercedes Lopez GomezAún no hay calificaciones

- Unidad 4 Fisica 2 Cuarto Cuatrimestre UdemexDocumento24 páginasUnidad 4 Fisica 2 Cuarto Cuatrimestre UdemexCynthia Herrera OchoaAún no hay calificaciones

- Protective Relaying Principles and Applications Blackburn (067-100) .En - Es PDFDocumento34 páginasProtective Relaying Principles and Applications Blackburn (067-100) .En - Es PDFCarlos MelgarAún no hay calificaciones

- Autos Eléctricos PDFDocumento36 páginasAutos Eléctricos PDFJesús Emanuel Urrutia100% (1)

- Sesión 2 Sistemas de Radiodifusión Sonora y Sistemas de TVDocumento77 páginasSesión 2 Sistemas de Radiodifusión Sonora y Sistemas de TVRosa SalvadorAún no hay calificaciones

- Manual Organizacion Enee Area Centralizada (Firma)Documento195 páginasManual Organizacion Enee Area Centralizada (Firma)Tito MejiaAún no hay calificaciones

- ResistividadDocumento1 páginaResistividadyissusAún no hay calificaciones

- Luminarias LEDDocumento15 páginasLuminarias LEDhermafrodita0935Aún no hay calificaciones

- Cuestionario Sobre Conductores EléctricosDocumento2 páginasCuestionario Sobre Conductores EléctricosRonal bp17100% (1)

- 16Documento8 páginas16carlosronquillo75% (4)

- Informe Resumen Desempeño de PasantesDocumento15 páginasInforme Resumen Desempeño de Pasantesomar nievesAún no hay calificaciones

- Electrodinámica IiDocumento4 páginasElectrodinámica IiRudy Saravia OcampoAún no hay calificaciones

- Riesgo Telemático - Físico-EléctricoDocumento74 páginasRiesgo Telemático - Físico-EléctricoBETSY JOHANNA NIETO HERMOSILLAAún no hay calificaciones

- Practica Tercer ParcialDocumento2 páginasPractica Tercer ParcialHugo Daniel Arteaga UriaAún no hay calificaciones

- Libro Estrategias para Resolver Problemas de Introduccià N A La Electrostática y Magnetostática 16052017 AUTORESDocumento215 páginasLibro Estrategias para Resolver Problemas de Introduccià N A La Electrostática y Magnetostática 16052017 AUTORESmonseAún no hay calificaciones

- Practica 4 CONEXIÓN EN PARALELO ALIMENTADOS CON CORRIENTE ALTERNADocumento5 páginasPractica 4 CONEXIÓN EN PARALELO ALIMENTADOS CON CORRIENTE ALTERNAUlises BerzosaAún no hay calificaciones

- Presentacion Diagnostico de FallaDocumento69 páginasPresentacion Diagnostico de FallaPedro RodriguezAún no hay calificaciones

- Presentación Clase SEM13Documento23 páginasPresentación Clase SEM13ANGEL JOAQUIN CALLUPE SEGURAAún no hay calificaciones

- Informe Previo 5 Ee441Documento15 páginasInforme Previo 5 Ee441Bernick Lincoln Salvador Rosas100% (1)

- PN2094 02 - Es EsDocumento6 páginasPN2094 02 - Es EsbrianAún no hay calificaciones

- Problemas Resueltos Motores de Corriente Alterna PDFDocumento56 páginasProblemas Resueltos Motores de Corriente Alterna PDFluis machucaAún no hay calificaciones

- Resumen Calculo de CortocircuitoDocumento30 páginasResumen Calculo de CortocircuitorvillasaAún no hay calificaciones

- Tipos de Conduntores ElectricosDocumento9 páginasTipos de Conduntores ElectricosLuigi MendozaAún no hay calificaciones

- Trabajo Sistema Puesta TierraDocumento13 páginasTrabajo Sistema Puesta TierraJavier UzcateguiAún no hay calificaciones

- T1 Dispositivos OptoelectronicosDocumento38 páginasT1 Dispositivos OptoelectronicosBryan GiovanniAún no hay calificaciones