Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Digitales Segundo Parcial

Cargado por

Mireya LuctualaDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Digitales Segundo Parcial

Cargado por

Mireya LuctualaCopyright:

Formatos disponibles

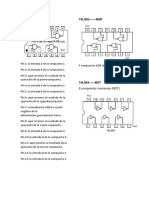

SUMADORES PARALELO DE

4 BITS 74LS283

Sumador paralelo de 4 bits que está disponible como circuito integrado es el

74LS283, está disponible en las familias TTL y CMOS.

Prof. Rosa A. Granizo L.

74LS283

Prof. Rosa A. Granizo L.

Expansión de sumadores

Los sumadores pueden ampliarse conectándose en cascada para

trabajar con más bits; ejemplo: cascada8 bits

Prof. Rosa A. Granizo L.

Expansión de sumadores

Los sumadores pueden ampliarse conectándose en cascada para

trabajar con más bits; ejemplo: cascada16 bits

Prof. Rosa A. Granizo L.

SUMADORES DE ACARREO SERIE

Y DE ACARREO ANTICIPADO

Los sumadores son iguales en términos de entradas y salidas. La diferencia

se encuentra en la velocidad a la que se suman los números.

El sumador de acarreo anticipado es mucho más rápido que el sumador

de acarreo serie.

Prof. Rosa A. Granizo L.

Sumador de acarreo serie

La salida de acarreo de cada sumador completo se conecta a la

entrada de acarreo de la siguiente etapa de orden superior

La suma y el acarreo de salida de cualquier etapa no se pueden

generar hasta que tiene lugar el acarreo de entrada

Por lo tanto produce un retardo temporal en el proceso de adición

Este retardo tiempo transcurrido Cin hasta Cout

Prof. Rosa A. Granizo L.

Sumador de acarreo serie

Prof. Rosa A. Granizo L.

Sumador de acarreo anticipado

Anticipa el acarreo de salida de cada etapa función de los bits de

entrada de cada etapa

Se genera acarreo (Cg) solo cuando ambos bit’s de entrada son 1’s

Cg función AND de los dos bit’s entrada Cg= AB

Un acarreo de propagación (Cp) cuando uno o ambos bit’s son 1’s

Se expresa con una función OR Cp = A + B

Prof. Rosa A. Granizo L.

Sumador de acarreo anticipado

Prof. Rosa A. Granizo L.

Generación de acarreo y propagación de

acarreo en función de los bits de entrada

en un sumador de 4 bits

Prof. Rosa A. Granizo L.

Generación de acarreo y propagación de

acarreo en función de los bits de entrada

en un sumador de 4 bits

Entonces desarrollamos las expresiones para el acarreo de salida:

Prof. Rosa A. Granizo L.

Generación de acarreo y propagación de

acarreo en función de los bits de entrada

en un sumador de 4 bits

Entonces desarrollamos las expresiones para el acarreo de salida:

Prof. Rosa A. Granizo L.

Generación de acarreo y propagación de

acarreo en función de los bits de entrada

en un sumador de 4 bits

Entonces desarrollamos las expresiones para el acarreo de salida:

Prof. Rosa A. Granizo L.

Conclusión

Se demuestra que el Cout depende únicamente del Cint1

Todos los acarreos están disponibles inmediatamente

No es necesario que a propague un acarreo a través de todas las

etapas

Esta técnica acelera el proceso de adición

Implementación del acarreo anticipado mediante la utilización de

compuertas lógicas

Prof. Rosa A. Granizo L.

Implementación del acarreo anticipado

mediante la utilización de compuertas

lógicas

Prof. Rosa A. Granizo L.

COMPARADORES

Consiste en comparar las magnitudes de dos cantidades binarias para

determinar su relación

Ejemplo : Un circuito comparador determina si dos números son iguales.

La puerta OR-exclusiva se puede emplear como un comparador básico

Prof. Rosa A. Granizo L.

COMPARADORES

Para comparar números binarios de dos bits, se necesita una puerta OR-

exclusiva adicional

Prof. Rosa A. Granizo L.

Ejemplo:

Determinar si son iguales o diferentes:

Prof. Rosa A. Granizo L.

Desigualdad

Algunos circuitos integrados comparadores tienen salidas adicionales

que indican cuál de los dos números que se comparan es el mayor.

Tienen salida que A>B , A< B, A= B

Para determinar una desigualdad entre los números binarios A y B, se

examina el bit de mayor orden de cada número

Prof. Rosa A. Granizo L.

Ejemplo:

Determinar las salidas A = B, A > B y A < B para los números de entrada

Prof. Rosa A. Granizo L.

EL COMPARADOR DE MAGNITUD DE 4 BITS

74HC85

Tiene tres entradas en cascada para utilizar comparadores en cascada

para la comparación de cualquier numero binario de 4 bit’s

Prof. Rosa A. Granizo L.

Ejemplo:

Utilizar comparadores 74HC85 para comparar las magnitudes de dos

números de 8 bits. Dibujar los comparadores con sus correspondientes

interconexiones.

Prof. Rosa A. Granizo L.

DECODIFICADORES

Su función es detectar la presencia de una determinada combinación

de bits (código) en sus entradas y señalar la presencia de este código

mediante un cierto nivel de salida.

Un decodificador posee n líneas de entrada para gestionar n bits y en una

de las 2^n líneas de salida indica la presencia de una o más

combinaciones de n bits.

Prof. Rosa A. Granizo L.

El decodificador binario básico

Determinar cuándo aparece el número binario 1001 en las entradas de un

circuito

Prof. Rosa A. Granizo L.

El decodificador de 4 bits

Para poder decodificar todas las posibles combinaciones de cuatro bits, se

necesitan dieciséis puertas de decodificación (2^4=16).

Se lo llama comúnmente decodificador de 4 líneas a 16 líneas

Prof. Rosa A. Granizo L.

Tabla del decodificador de 4 bits

Prof. Rosa A. Granizo L.

EL DECODIFICADOR 1 DE 16 74HC154

Tiene enable

activo a bajo

Prof. Rosa A. Granizo L.

Ejemplo

Se requiere

decodificar un

número de 5

bits, utilizar

decodificadores

74HC154

Prof. Rosa A. Granizo L.

Aplicación

Prof. Rosa A. Granizo L.

El decodificador BCD a decimal

Se lo llama decodificador de

4-línes a 10-líneas o

decodificador 1 de 10.

El método de implementación

es el mismo anteriormente

para el decodificador de 4-

líneas a 16-líneas, excepto que

ahora sólo se requieren diez

puertas decodificadoras

BCD 0 – 9

El 74HC42 es un CI

decodificador BCD-decimal

Prof. Rosa A. Granizo L.

El decodificador BCD a 7-segmentos 74LS47

El decodificador BCD a 7-

segmentos acepta el

código BCD en sus

entradas y proporciona

salidas capaces de

excitar un display de 7-

segmentos para generar

un dígito decimal.

Prof. Rosa A. Granizo L.

CODIFICADORES

Un codificador es un circuito lógico combinacional función “inversa” del

decodificador

Permite en una de sus entradas un nivel activo que representa un dígito,

como puede ser un dígito decimal u octal, y lo convierte en una salida

codificada, como BCD o binario.

Prof. Rosa A. Granizo L.

Codificador decimal-BCD

Este codificador tiene diez entradas, una para cada dígito decimal, y

cuatro salidas que corresponden al código BCD

Prof. Rosa A. Granizo L.

EL CODIFICADOR DECIMAL-BCD 74HC147

Es un codificador con prioridad con entradas activas a nivel BAJO para

los dígitos decimales del 1 al 9, y salidas BCD activas a nivel BAJO

Prof. Rosa A. Granizo L.

EL CODIFICADOR 8-LÍNEAS A 3-LÍNEAS

74LS148

Es un codificador con prioridad que tiene ocho entradas activas a nivel

BAJO y tres salidas binarias activas a nivel BAJO

Prof. Rosa A. Granizo L.

EL CODIFICADOR 8-LÍNEAS A 3-LÍNEAS

74LS148

74LS148 puede ser ampliado a un

codificador de 16-líneas a 4-líneas

conectando la salida EO del codificador de

mayor orden a la entrada EI del codificador

de menor orden, y aplicando la operación

negativa-OR a las correspondientes salidas

binarias

Prof. Rosa A. Granizo L.

MULTIPLEXORES (SELECTORES DE DATOS)

Un multiplexor (MUX) es un dispositivo que permite dirigir la información

digital procedente de diversas fuentes a una única línea para ser

transmitida a través de dicha línea a un destino común

Prof. Rosa A. Granizo L.

EL MULTIPLEXOR/SELECTOR DE DATOS DE 8

ENTRADAS 74LS151

El 74LS151 tiene ocho entradas de datos (D0 −D7) y, por tanto, tres líneas de

entrada de dirección o de selección de datos (S0-S2)

Prof. Rosa A. Granizo L.

Ejemplo:

Utilizar multiplexores 74LS151 y cualquier otra lógica necesaria para multiplexar

16 líneas de datos en una única línea de salida de datos.

Prof. Rosa A. Granizo L.

DEMULTIPLEXORES

Un demultiplexor (DEMUX) básicamente realiza la función contraria a la del

multiplexor se conoce también como distribuidor de datos

Demultiplexor (DEMUX) de 1-línea a 4-líneas

Prof. Rosa A. Granizo L.

EL DEMULTIPLEXOR 74HC154

Usan las líneas

de entrada

como líneas de

selección de

datos

Una de las

entradas de

activación se

usa como línea

de entrada de

datos y la otra

se mantiene a

nivel BAJO

Prof. Rosa A. Granizo L.

TEMPORIZADOR 555

COMO OSCILADOR

Es un oscilador de onda cuadrada y es versátil con muchas aplicaciones.

Prof. Rosa Granizo L.

Timer 555

Se compone dos comparadores un biestable (flip-flop) un transistor

de descarga y un divisor de voltaje resistivo

El FF un dispositivo de dos estados cuya salida nivel de voltaje alto

establecer S o un nivel de voltaje bajo reestablecer R

La salida cambia con señales de entrada apropiadas

El divisor de voltaje resistivo se utiliza para establecer los niveles de voltaje

en el comparador

El comparador alto tiene una referencia de 2 ⁄3VCC y el bajo tiene una

referencia de 1 ⁄3VCC

Prof. Rosa Granizo L.

Timer 555

Las salidas de los comparadores controlan el estado del biestable

Cuando el voltaje de disparo se reduce por debajo de 1 ⁄3VCC el

biestable se inicia y la salida salta a un nivel alto

La entrada de umbral normalmente está conectada a un circuito

temporizador RC externo

Cuando el voltaje en el capacitor externo excede de 2⁄3VCC

El comparador alto reestablece el biestable regresa la salida a su nivel

bajo

El transistor de descarga (Qd) se enciende y proporciona una trayectoria

para la descarga rápida del capacitor de temporización externo.

Prof. Rosa Granizo L.

Timer 555

Esta operación

básica permite

configurar el

temporizador con

componentes

externos como un

oscilador

Un monoestable

o un elemento de

retardo

Prof. Rosa Granizo L.

Timer 555

R1 y R2 D

Cext Carga R1

+R2

Descarga R2

D

Prof. Rosa Granizo L.

Timer 555

El período es :

El ciclo de trabajo D en % es:

Prof. Rosa Granizo L.

Timer 555

Para D < 50% se puede

modificar el circuito

Cext se cargue sólo a

través de R1 y se

descargue a través de R2,

esto diodo D1

El D< 50% R1<R2

Prof. Rosa Granizo L.

Ejercicio

Un temporizador 555

configurado para que

funcione en el modo

astable Determinar la

frecuencia de la salida y

el ciclo de trabajo.

Prof. Rosa Granizo L.

Ejercicio

Un temporizador 555

configurado para que

funcione en el modo

astable Determinar la

frecuencia de la salida y

el ciclo de trabajo.

Prof. Rosa Granizo L.

LATCHES, FLIP-FLOPS

La diferencia básica entre latches y flip-flops es la manera en que cambian

de un estado a otro.

Prof. Rosa Granizo L.

LATCHES

El latch cerrojo es un tipo de dispositivo de almacenamiento temporal

de dos estados biestable, categoría diferente flip-flops

Pueden permanecer en sus diferentes estados gracias a su capacidad

de realimentación

La diferencia principal entre estos tipos de dispositivos está en el método

empleado para cambiar de estado.

Prof. Rosa Granizo L.

El latch S-R (SET-RESET)

Un latch es un tipo de dispositivo lógico biestable o multivibrador

Entrada activa a nivel ALTO formado dos puertas NOR acopladas

Un latch con entrada activa a nivel BAJO está formado por dos puertas

NAND

La salida de cada puerta se conecta a la entrada de la puerta opuesta

Dando lugar a realimentación feedback característica de todos

los latches y flip-flops.

Prof. Rosa Granizo L.

El latch S-R (SET-RESET)

Entradas a Nivel Alto1

5V 7402

Entradas a Nivel Bajo 0

0V7400

Prof. Rosa Granizo L.

Aplicación Eliminador de rebote de

contactos

Prof. Rosa Granizo L.

LATCH SET-RESET 74LS279

Este es un cuádruple latch como se muestra en las siguientes figuras:

Prof. Rosa Granizo L.

El latch S-R con entrada de

habilitación

Las entradas S y R controlan el estado al que va a cambiar el latch

cuando se aplica un nivel ALTO a la entrada de habilitación EN, enable

no cambia de estado hasta EN nivel alto

El estado no válido del latch se produce cuando las dos entradas S y R

están simultáneamente a nivel ALTO.

Prof. Rosa Granizo L.

Ejemplo

Determinar la forma de onda de salida Q, si se aplican las señales de

entrada mostradas a un latch S-R con entrada de habilitación, que se

encuentra inicialmente en estado de RESET

Prof. Rosa Granizo L.

El latch D con entrada de habilitación

La diferencia con el anterior solo una entrada además del enable

Prof. Rosa Granizo L.

LATCH D 74LS75

Este dispositivo está compuesto por cuatro latches,la entrada de

habilitación EN activa a nivel ALTO con su respectiva tabla de verdad

Prof. Rosa Granizo L.

FLIP-FLOPS DISPARADOS POR FLANCO

Los flip-flops son dispositivos síncronos de dos estados, también conocidos

como multivibradores biestables

El término síncrono significa que la salida cambia de estado únicamente

en un instante específico de una entrada de disparo denominada reloj

(CLK) control

Esto significa que los cambios en la salida se producen sincronizadamente

con el reloj.

Un flip-flop disparado por flanco cambia de estado con el flanco positivo

flanco de subida, o con el flanco negativo flanco de bajada del

impulso de reloj

Los disparados por flancos son S-R, D, y J-K

Prof. Rosa Granizo L.

FLIP-FLOPS DISPARADOS POR FLANCO

Prof. Rosa Granizo L.

FLIP-FLOPS DISPARADOS POR FLANCO

Prof. Rosa Granizo L.

Ejemplo

Determinar las formas de onda de salida Q, para las entradas S, R y CLK

Suponer que el flip-flop disparado por flanco positivo se encuentra,

inicialmente, en estado RESET.

Prof. Rosa Granizo L.

Un método de disparo por flanco

El flip-flop S-R se distingue del latch S-R con entrada de habilitación

únicamente en que cuenta con un detector de transiciones de impulsos.

Prof. Rosa Granizo L.

Un método de disparo por flanco

Prof. Rosa Granizo L.

El flip-flop D disparado por flanco

El flip-flop D resulta muy útil cuando se necesita almacenar un único bit de

datos (1 o 0)

Si se añade un inversor a un flip-flop S-R obtenemos un flipflop D básico

Prof. Rosa Granizo L.

Ejemplo

Dadas las formas de onda de la Figura 7.21(a) para la entrada D y el reloj,

determinar la onda de salida Q si el flip-flop parte del estado RESET

Prof. Rosa Granizo L.

El flip-flop J-K disparado por flanco

El flip-flop J-K es versátil y es uno de los tipos de flip-flop más ampliamente

utilizado

El funcionamiento del flip-flop J-K es idéntico al del flip-flop S-R en las

condiciones de operación SET, RESET y de permanencia de estado (no

cambio)

La diferencia está en que el flip-flop J-K no tiene condiciones no válidas

como ocurre en el S-R.

Prof. Rosa Granizo L.

El flip-flop J-K disparado por flanco

Cuando está basculación

F.F. tipo T

Prof. Rosa Granizo L.

Ejemplo:

Las formas de onda se aplican a las entradas J, K y de reloj, tal y como se

muestra. Determinar la salida Q suponiendo que el flip-flop se encuentra

inicialmente en estado RESET.

Prof. Rosa Granizo L.

Entradas asíncronas de

inicialización y borrado

F.F. S-R, D y J-K tiene sus entradas síncronas, ya que los datos de estas

entradas condicionan la salida F.F sólo durante el flanco de disparo del

impulso de reloj; esto significa que los datos se transfieren sincronizados con la

señal de reloj.

Prof. Rosa A. Granizo L.

Entradas

Una entrada de inicialización activa

pone la salida Q a nivel ALTO (SET).

Una entrada de borrado activa

pone la salida Q a nivel BAJO

(RESET).

Prof. Rosa A. Granizo L.

Ejemplo:

En un F.F J-K activado por flanco positivo con entradas preset y clear, se

debe determinar la salida Q para las entradas mostradas en el diagrama

de tiempos de la parte (a), si Q está inicialmente a nivel BAJO.

Prof. Rosa A. Granizo L.

CARACTERÍSTICAS DE OPERACIÓN DE LOS

FLIP-FLOPS

Retardos de propagación el intervalo de tiempo requerido para que se produzca un

cambio en la salida una vez que se ha aplicado una señal en la entrada

Prof. Rosa A. Granizo L.

CARACTERÍSTICAS DE OPERACIÓN DE LOS

FLIP-FLOPS

Tiempo de establecimiento ts setup time es el intervalo mínimo que

los niveles lógicos deben mantener constantes en las entradas (J y K, S

y R o D) antes de que llegue el flanco de disparo del impulso de reloj,

de modo que dichos niveles sincronicen correctamente en el F.F

Prof. Rosa A. Granizo L.

CARACTERÍSTICAS DE OPERACIÓN DE LOS

FLIP-FLOPS

Frecuencia máxima de reloj fmax es la mayor velocidad a la que se puede

disparar el F.F de manera fiable. Para frecuencias del reloj por encima de la

máxima, el F.F puede ser incapaz de responder lo suficientemente rápido y su

funcionamiento se vería deteriorado.

Anchura de los impulsos los fabricantes especifican la anchura mínima de los

impulsos (tW) para un funcionamiento adecuado de las entradas de reloj,

inicialización y borrado. Típicamente, el reloj se especifica mediante sus intervalos

de tiempo mínimo para los niveles ALTO y BAJO.

Disipación de potencia La disipación de potencia de cualquier circuito digital se

define como la potencia total consumida por el dispositivo. Por ejemplo, si el F. F

funciona con una fuente de continua de +5 V y circula por él una corriente de 5 mA,

la disipación de potencia es:

P = VCC ⋅ ICC = 5 V ⋅ 5 mA = 25 mW

Prof. Rosa A. Granizo L.

CARACTERÍSTICAS DE OPERACIÓN DE LOS

FLIP-FLOPS

Disipación de potencia Ahora supones que tenemos un sistema digital que

requiere un total 10 F.F. que cada uno de ellos disipa una potencia de 25 mW.

PT = 10 ⋅ 25 mW = 250 mW = 0,25 W Po fuente de alimentación.

Para calcular la corriente total que tiene que suministrar la fuente sería

Por tanto necesitamos una fuente de 5V que suministre una I al menos 50mA

Prof. Rosa A. Granizo L.

APLICACIONES DE LOS FLIP-FLOPS

Almacenamiento

de datos paralelo

Prof. Rosa A. Granizo L.

APLICACIONES DE LOS FLIP-FLOPS

División de

frecuencia

Prof. Rosa A. Granizo L.

APLICACIONES DE LOS FLIP-FLOPS

Contadores

Prof. Rosa A. Granizo L.

APLICACIONES DE LOS FLIP-FLOPS

Contadores

Prof. Rosa A. Granizo L.

También podría gustarte

- Trabajo de Logica Digital DecodificadoresDocumento12 páginasTrabajo de Logica Digital DecodificadoreskarenpadronAún no hay calificaciones

- Multiplex OresDocumento17 páginasMultiplex Oresyouacrazy100% (1)

- Circuitos Combinacionales MSIDocumento13 páginasCircuitos Combinacionales MSIKarlita NuñezAún no hay calificaciones

- Anexo Codificadores y DecodificadoresDocumento7 páginasAnexo Codificadores y DecodificadoresJuana L Atorre S AnchezAún no hay calificaciones

- Decodificador BCD A 7 SegmentosDocumento8 páginasDecodificador BCD A 7 Segmentoscarlos3107100% (1)

- Componentes Combinacionales Basicos PDFDocumento49 páginasComponentes Combinacionales Basicos PDFAnonymous o7WTkbq8bAún no hay calificaciones

- Trabajo de DigitalesDocumento5 páginasTrabajo de DigitalesJuniior Cabrera BolivarAún no hay calificaciones

- Codificador BCD A Display de 7 SegmentosDocumento11 páginasCodificador BCD A Display de 7 SegmentosPcsolution SlpAún no hay calificaciones

- 8.deco Codi ResumenDocumento7 páginas8.deco Codi ResumenYair AlmadaAún no hay calificaciones

- Informe Previo Numero 5 C.digitalesDocumento12 páginasInforme Previo Numero 5 C.digitalesDiego FloresAún no hay calificaciones

- Tipos de CircuitosDocumento11 páginasTipos de Circuitosalonsoalex25Aún no hay calificaciones

- DECODIFICADORDocumento10 páginasDECODIFICADORJulio BonillaAún no hay calificaciones

- DECODIFICADORDocumento10 páginasDECODIFICADORJulio BonillaAún no hay calificaciones

- Semana03y04-Logica Combinacional PDFDocumento61 páginasSemana03y04-Logica Combinacional PDFYobany alberto Romero martinezAún no hay calificaciones

- Bloques FuncionalesDocumento19 páginasBloques FuncionalesEdy GVAún no hay calificaciones

- Circuitos DecodificadoresDocumento3 páginasCircuitos Decodificadoressaul lozadaAún no hay calificaciones

- MsiDocumento107 páginasMsiHernán PogoAún no hay calificaciones

- Informe Previo N°5Documento20 páginasInforme Previo N°5Hubert Vásquez CuevaAún no hay calificaciones

- Codificador y Decodificador de BCD A 7 SegmentosDocumento7 páginasCodificador y Decodificador de BCD A 7 SegmentosLeonardo Perez PradoAún no hay calificaciones

- Practica 5Documento10 páginasPractica 5Lenin Pardo SalazarAún no hay calificaciones

- DEMULTIPLEXORDocumento11 páginasDEMULTIPLEXORDaniel ReyesAún no hay calificaciones

- Multiplexores y DemultiplexorDocumento25 páginasMultiplexores y DemultiplexorJOSÉ LUIS REYNOSO TIUAún no hay calificaciones

- El 74LS164NDocumento5 páginasEl 74LS164NcharlycortosAún no hay calificaciones

- Funciones de La Logica CombinacionalDocumento27 páginasFunciones de La Logica CombinacionalJuan David Acosta DangondAún no hay calificaciones

- Informe de Un Restador en PROTOBOARDDocumento10 páginasInforme de Un Restador en PROTOBOARDIvan Crispin PaucarAún no hay calificaciones

- PRACTICA 6docxDocumento5 páginasPRACTICA 6docxRene PerezAún no hay calificaciones

- CUESTIONARIO PREVIO N°5 (QUINTANA, JOHN)Documento16 páginasCUESTIONARIO PREVIO N°5 (QUINTANA, JOHN)John QuintanaAún no hay calificaciones

- Arista Lopez Josue Darwin - 2023 - Laboratorio - Circuitos Digitales - 05Documento31 páginasArista Lopez Josue Darwin - 2023 - Laboratorio - Circuitos Digitales - 05JOSUE DARWIN ARISTA LOPEZAún no hay calificaciones

- 7 DecodificadoresDocumento8 páginas7 DecodificadoresalexisAún no hay calificaciones

- Marco Teorico Labo 5Documento12 páginasMarco Teorico Labo 5DanteJaraEspinozaAún no hay calificaciones

- Diagrama de Bloques Circuitos LogicosDocumento3 páginasDiagrama de Bloques Circuitos Logicosoperadorelias0% (1)

- FrecuencimetroDocumento6 páginasFrecuencimetroRodrigo Marcelo Parra Aguilar100% (1)

- Codificadores Dec BCD PDFDocumento6 páginasCodificadores Dec BCD PDFJudith CasasAún no hay calificaciones

- Converter CodeDocumento19 páginasConverter CodeseleneedithAún no hay calificaciones

- 8 CombinacionalesDocumento65 páginas8 CombinacionalesFERMINAún no hay calificaciones

- Circuitos MSI y Sus Aplicaciones (Clase D)Documento39 páginasCircuitos MSI y Sus Aplicaciones (Clase D)kevin isaiasAún no hay calificaciones

- Informe de ElectronicosDocumento20 páginasInforme de ElectronicosMartin QuioszAún no hay calificaciones

- EDG023 Dia 7 CodDecDocumento47 páginasEDG023 Dia 7 CodDecdennis bolañosAún no hay calificaciones

- Circuitos Integrados CaracteristicasDocumento3 páginasCircuitos Integrados CaracteristicasLuis Gusman EstradaAún no hay calificaciones

- DecodificadorDocumento4 páginasDecodificadorOmar GuerreroAún no hay calificaciones

- Practica 5Documento10 páginasPractica 5HomeroOjedaAún no hay calificaciones

- Diseño de Circuitos Combinacionales2Documento15 páginasDiseño de Circuitos Combinacionales2Alex GomezAún no hay calificaciones

- Laboratorio de Electrónica Digital - Parctica 2 Fecha de NacimientoDocumento14 páginasLaboratorio de Electrónica Digital - Parctica 2 Fecha de NacimientoRomina OropezaAún no hay calificaciones

- Informe N°5Documento10 páginasInforme N°5Hans HuamanAún no hay calificaciones

- Practicas de DigitalDocumento27 páginasPracticas de DigitalLuis ValdezAún no hay calificaciones

- Codificadores y DecodificadoresDocumento5 páginasCodificadores y DecodificadoresGabriel Pavon IpialesAún no hay calificaciones

- Practica 4 CIRCUITOS MSI. GENERACION DE FUNCIONES LÓGICAS CODIFICADORES, DECODIFICADORES, MULTIPLEXORES Y DEMULTIPLEXORESDocumento8 páginasPractica 4 CIRCUITOS MSI. GENERACION DE FUNCIONES LÓGICAS CODIFICADORES, DECODIFICADORES, MULTIPLEXORES Y DEMULTIPLEXORESJesús'Chucho'MohaliAún no hay calificaciones

- Circuitos CombinacionalesDocumento59 páginasCircuitos CombinacionalesJuan Torres GamarraAún no hay calificaciones

- Diagramas de Tiempo Compuertas Logicas 1Documento21 páginasDiagramas de Tiempo Compuertas Logicas 1Miguel Ruiz0% (1)

- Sesion 3 A 4Documento62 páginasSesion 3 A 4Hugo Quezada AlegríaAún no hay calificaciones

- De Multiplex OresDocumento25 páginasDe Multiplex OresAxel HernandezAún no hay calificaciones

- Circuitos CombinacionalesDocumento19 páginasCircuitos Combinacionalescc ddAún no hay calificaciones

- Catalogo de Productos Jieremy Coronel 27346954Documento22 páginasCatalogo de Productos Jieremy Coronel 27346954jieremy11Aún no hay calificaciones

- Registro de DesplazamientoDocumento10 páginasRegistro de DesplazamientoLeydycita HemofixAún no hay calificaciones

- Clase 4Documento19 páginasClase 4Josue David Zea HerreraAún no hay calificaciones

- Unidad III - Diseño Con Circuitos MSIDocumento18 páginasUnidad III - Diseño Con Circuitos MSICarlos OrtegaAún no hay calificaciones

- S05 - Sistemas Combinacionales IIDocumento38 páginasS05 - Sistemas Combinacionales IImicuantaAún no hay calificaciones

- Informe 7 Sistemas DigitalesDocumento12 páginasInforme 7 Sistemas DigitalesXavier GuanoAún no hay calificaciones

- 100 Circuitos de Audio (ES) - volume 1De Everand100 Circuitos de Audio (ES) - volume 1Calificación: 5 de 5 estrellas5/5 (2)

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiDe EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiCalificación: 5 de 5 estrellas5/5 (1)

- Padilla Fernando Tarea 1 Individual 09-11-2021 Ensayo EvidenciaDocumento1 páginaPadilla Fernando Tarea 1 Individual 09-11-2021 Ensayo EvidenciaMireya LuctualaAún no hay calificaciones

- Guia 1Documento1 páginaGuia 1Mireya LuctualaAún no hay calificaciones

- Malla Curricular Mecanica NavalDocumento1 páginaMalla Curricular Mecanica NavalMireya LuctualaAún no hay calificaciones

- Vasquez Franklin Consulta Curvas B-H y U-HDocumento4 páginasVasquez Franklin Consulta Curvas B-H y U-HMireya LuctualaAún no hay calificaciones

- Tarea 10 Resumen Técnico de La Normativa Nacional Semana 4 - Lema LuisDocumento14 páginasTarea 10 Resumen Técnico de La Normativa Nacional Semana 4 - Lema LuisMireya LuctualaAún no hay calificaciones

- Banco de Preguntas 2 Parcial 2Documento82 páginasBanco de Preguntas 2 Parcial 2Mireya LuctualaAún no hay calificaciones

- Luctuala Fatima - Guia Individual Unidad2Documento14 páginasLuctuala Fatima - Guia Individual Unidad2Mireya LuctualaAún no hay calificaciones

- Luctuala Mireya - Motor de Imanes Permanentes - Motor de Reluctancia - Motor de Flujo AxialDocumento6 páginasLuctuala Mireya - Motor de Imanes Permanentes - Motor de Reluctancia - Motor de Flujo AxialMireya LuctualaAún no hay calificaciones

- Shineray X30, La Van Favorita Del Trabajador Ecuatoriano - Carburando - EcDocumento3 páginasShineray X30, La Van Favorita Del Trabajador Ecuatoriano - Carburando - EcMireya LuctualaAún no hay calificaciones

- Cuestionario Segundo Parcial - Inuca Jefferson - Grupo IDocumento69 páginasCuestionario Segundo Parcial - Inuca Jefferson - Grupo IMireya LuctualaAún no hay calificaciones

- NEUMAICOSDocumento10 páginasNEUMAICOSMireya LuctualaAún no hay calificaciones

- Formado Por Pulsos Magnéticos CuestionarioDocumento2 páginasFormado Por Pulsos Magnéticos CuestionarioMireya LuctualaAún no hay calificaciones

- Lección Conformado Por LaminadoDocumento20 páginasLección Conformado Por LaminadoMireya LuctualaAún no hay calificaciones

- Examen Seguridad 2 ParcialDocumento18 páginasExamen Seguridad 2 ParcialMireya LuctualaAún no hay calificaciones

- ) Diseñe Un Varillaje de Cuatro Barras para Mover La Caja A Través ...Documento2 páginas) Diseñe Un Varillaje de Cuatro Barras para Mover La Caja A Través ...Mireya LuctualaAún no hay calificaciones

- Cuestionario TrefiladoDocumento4 páginasCuestionario TrefiladoMireya Luctuala100% (1)

- Ejercicio de CognadosDocumento2 páginasEjercicio de CognadosMireya LuctualaAún no hay calificaciones

- ANÁLISIS DE LOS INTERCAMBIADORES - Grupo 6Documento8 páginasANÁLISIS DE LOS INTERCAMBIADORES - Grupo 6Mireya LuctualaAún no hay calificaciones

- TRASMISIONDocumento1 páginaTRASMISIONMireya LuctualaAún no hay calificaciones

- MicropythonDocumento9 páginasMicropythonMireya LuctualaAún no hay calificaciones

- P3 - Tarea 1 - Ensayo Modelo de Innovacion - Inuca JeffersonDocumento4 páginasP3 - Tarea 1 - Ensayo Modelo de Innovacion - Inuca JeffersonMireya LuctualaAún no hay calificaciones

- Decorar La Vocal EeDocumento1 páginaDecorar La Vocal EeMireya LuctualaAún no hay calificaciones

- Preguntas Rectificadora de Cilindros - Partes y Carácteristicas TécnicasDocumento1 páginaPreguntas Rectificadora de Cilindros - Partes y Carácteristicas TécnicasMireya LuctualaAún no hay calificaciones

- Vocal oDocumento1 páginaVocal oMireya LuctualaAún no hay calificaciones

- Preguntas CilindrosDocumento2 páginasPreguntas CilindrosMireya Luctuala100% (1)

- Decorar La Vocal EeDocumento1 páginaDecorar La Vocal EeMireya LuctualaAún no hay calificaciones

- 3 Unad Examenes MorfofisiologiaDocumento13 páginas3 Unad Examenes MorfofisiologiaHéctor Armando Valderrama Baquero67% (3)

- 1º Parcial FitoDocumento150 páginas1º Parcial FitoVili Eli Domínguez Quino100% (1)

- MENDOZA CORDOVA Karenina Ultimo 2022Documento36 páginasMENDOZA CORDOVA Karenina Ultimo 2022YESICA MARIVEL BAUTISTA REQUEZAún no hay calificaciones

- Faro Docente 2020Documento88 páginasFaro Docente 2020Agustina GramajoAún no hay calificaciones

- Procedimientos Operativos Normalizados - PONSDocumento18 páginasProcedimientos Operativos Normalizados - PONSHéctor F. Martínez D.Aún no hay calificaciones

- BOOKINGDocumento4 páginasBOOKINGMaffe ArellanoAún no hay calificaciones

- LogisticaDocumento19 páginasLogisticaMitzu ToyosatoAún no hay calificaciones

- PRE QuimicaDocumento9 páginasPRE QuimicaStefany AgudeloAún no hay calificaciones

- Catalogo GalvasidDocumento32 páginasCatalogo GalvasidOscar AlonsoAún no hay calificaciones

- 90 10EstudioShakespearDocumento8 páginas90 10EstudioShakespearJuanjo GoncalvesAún no hay calificaciones

- Linea Del TiempoDocumento2 páginasLinea Del TiempoSara GonzálezAún no hay calificaciones

- MANUAL FUSION 3 EspañolDocumento32 páginasMANUAL FUSION 3 EspañolVicente Luna GarcíaAún no hay calificaciones

- Modelo Guía Protocolo de Bioseguridad CDSDocumento27 páginasModelo Guía Protocolo de Bioseguridad CDShelenaAún no hay calificaciones

- DescargaDocumento1 páginaDescargaLuis Angel Santos AlmazanAún no hay calificaciones

- Practica 2Documento4 páginasPractica 2Mario XavierAún no hay calificaciones

- Mires, Fernando - La Revolucion Que Nadie SoñoDocumento179 páginasMires, Fernando - La Revolucion Que Nadie SoñoMichelle Otero100% (1)

- Asis Callao 2002-2003Documento339 páginasAsis Callao 2002-2003Liliana CoggiolaAún no hay calificaciones

- Estudio de Factibilidad de Ingenio AzucareroDocumento99 páginasEstudio de Factibilidad de Ingenio AzucareroCarlos Espada100% (2)

- La Actividad Física Terapéutica y Profiláctica en El Adulto MayorDocumento14 páginasLa Actividad Física Terapéutica y Profiláctica en El Adulto MayorCristian Manuel Goicochea ChuqueAún no hay calificaciones

- Modelos Más Usados en EnfermeríaDocumento18 páginasModelos Más Usados en EnfermeríaAdriana RuizAún no hay calificaciones

- CubiertasDocumento59 páginasCubiertasEsneiider GarciiaAún no hay calificaciones

- Tarea 1Documento5 páginasTarea 1Inaara NuñezAún no hay calificaciones

- Plan de PracticasDocumento7 páginasPlan de PracticasCarlos Ramirez AcuñaAún no hay calificaciones

- Infografía Línea de Tiempo Moderna Rosa y Negro PDFDocumento5 páginasInfografía Línea de Tiempo Moderna Rosa y Negro PDFValeria VizhñayAún no hay calificaciones

- Biol PreoDocumento2 páginasBiol Preogasto05Aún no hay calificaciones

- (Inagep) Iperc - Llimpieza Publica - Actividad Obligatoria A DesarrollarDocumento6 páginas(Inagep) Iperc - Llimpieza Publica - Actividad Obligatoria A DesarrollarARLENY PORTEROAún no hay calificaciones

- Ep Mecanica-Cynthia Alejandra Quevedo Falconi (2011177375) - IcaDocumento9 páginasEp Mecanica-Cynthia Alejandra Quevedo Falconi (2011177375) - IcaceluzAún no hay calificaciones

- Empresas Españolas en RD PDFDocumento35 páginasEmpresas Españolas en RD PDFramon alberto brea felixAún no hay calificaciones

- TIKA - Ficha de Evaluación y Presentación de Proyectos Colombia 2019Documento5 páginasTIKA - Ficha de Evaluación y Presentación de Proyectos Colombia 2019juan carlos rodriguez amayaAún no hay calificaciones

- La Capacidad Instalada de Un Taller Automotriz Es Crucial para Su Funcionamiento EficienteDocumento6 páginasLa Capacidad Instalada de Un Taller Automotriz Es Crucial para Su Funcionamiento EficienteFrancisco Antonio Coste NuñezAún no hay calificaciones