Documentos de Académico

Documentos de Profesional

Documentos de Cultura

TEMA 6 Amplificador Diferencial

TEMA 6 Amplificador Diferencial

Cargado por

WATNER OCHOA NUÑEZTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

TEMA 6 Amplificador Diferencial

TEMA 6 Amplificador Diferencial

Cargado por

WATNER OCHOA NUÑEZCopyright:

Formatos disponibles

Tema 6

TEMA 6

Amplificador diferencial

6.1.- Introducción

El amplificador diferencial es un circuito que constituye parte fundamental de muchos amplificadores y

comparadores y es la etapa clave de la familia lógica ECL. En este tema se describen y analizan diferentes tipos de

amplificadores diferenciales basados en dispositivos bipolares y FET. Se abordan técnicas de polarización y

análisis de pequeña señal introduciendo los conceptos en modo diferencial y modo común que permiten

simplificar el análisis de estos amplificadores. Por último, se presentan y estudian amplificadores diferenciales

integrados complejos que resultan muy útiles como introducción a los amplificadores operacionales.

6.2.- Análisis de un amplificador diferencial básico bipolar

El amplificador diferencial constituye la etapa de entrada más típica de la mayoría de los amplificadores

operaciones y comparadores, siendo además el elemento básico de las puertas digitales de la familia lógica ECL.

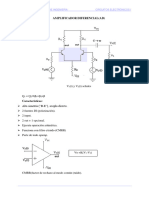

En la figura 6.1.a aparece la estructura básica de este amplificador. Uno de sus aspectos más importantes es su

simetría que le confiere unas características muy especiales de análisis y diseño. Por ello, los transistores Q1 y Q2

deben ser idénticos, aspecto que únicamente se logra cuando el circuito está fabricado en un chip. Realizar este

amplificador con componentes discretos pierde sus principales propiedades al romperse esa simetría. A

continuación se realiza un análisis de este amplificador, primero en continua y luego en alterna donde se

introducen los conceptos de configuración en modo común y modo diferencial.

V CC V CC

RC RC

IC

Recta de carga estática

VCC

vo1 vo2

R C+2RE

Q1 Q2

+ +

vi1 ~ ~ vi2 Q

ICQ IBQ

RE

—V CC VCEQ 2VCC VCE

a) b)

Figura 6.1. a) Amplificador diferencial básico y b ) recta de carga estática.

I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001 – 101 –

Electronica Básica para Ingenieros

6.2.1.- Análisis en continua

En el caso de que vi1 y vi2 sean componentes de pequeña señal, y suponiendo que hFE>>1, entonces se puede

extraer del circuito de la figura 6.1.a la siguiente relación

0 ≈ VBE + (I E1 + I E 2 )R E − VCC (6.1)

La simetría del circuito y el hecho de que Q1 y Q2 son transistores idénticos hace que IE1=IE2=IE de forma

que

V − VBE

I E ≈ I C = CC

2R E (6.2)

La ecuación de recta de carga estática se obtiene aplicando KVL a la malla colector-emisor de los

transistores:

2 VCC ≈ VCE + I C ( R C + 2 R E ) (6.3)

Esta recta se encuentra dibujada en la figura 6.1.b. La situación del punto de trabajo define los límites de

variación de señal de entrada y el rango de funcionamiento lineal permisible. La máxima amplitud de salida se

consigue cuando VCEQ=VCC.

6.2.2.- Análisis de las configuraciones en modo común y diferencial

La simetría del amplificador diferencial permite simplificar su

análisis convirtiendo las tensiones de entrada en tensiones de VCC VCC

entrada de modo común y modo diferencial. Además, estos

conceptos están en consonancia con las aplicaciones típicas del RC RC

amplificador operacional que se suele utilizar para amplificar la

diferencia entre las dos señales de entrada. La tensión de entrada vo1 vo2

en modo diferencial (vid) y modo común (vic) se definen como

Q1 Q2

v id = v i1 − v i 2

v i1 = v id / 2 + v ic

v i1 + v i 2 o

v ic = v i 2 = ±v id / 2 + v ic RE

2 (6.4) + +

~ ~ –vid/2

A su vez, estas tensiones vid y vic dan lugar a dos tensiones vid/2

VCC

de salida, en modo diferencial (vod) y modo común (voc), definidas

de una manera similar como

vic ~

vod = vo1 − vo2

vo1 = vod / 2 + voc

vo1 + vo2 o

voc = vo2 = ±vod / 2 + voc Figura 6 . 2. Amplificador diferencial con

2 (6.5) tensiones en modo diferencial y modo común.

Con la definición de las tensiones en modo diferencial y modo común, el amplificador diferencial tiene dos

ganancias, una en modo diferencial (Ad) y otra en modo común (Ac) definidas como

– 102 – I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001

Tema 6

v v

A d = od y A c = oc

v id v ic (6.6)

La aplicación de los estos conceptos permite transformar el circuito de la figura 6.1.a en el de la figura 6.2.

Este nuevo circuito presenta unas propiedades de simetría que facilita su análisis mediante la aplicación del

principio de superposición a las entradas en modo diferencial y común independientemente.

• Ganancia en modo diferencial

En la figura 6.3 se muestra el circuito equivalente simplificado del amplificador diferencial cuando

únicamente se considera modo diferencial a la entrada. El análisis del circuito establece las siguientes ecuaciones

v id / 2 = i b1h ie − i b 2 h ie − v id / 2 ⇒ v id = (i b1 − i b 2 )h ie

v e = (i b1 + i b 2 )(1 + h fe )R E

v / 2 = i h + v

id b1 ie e

(6.7)

RC RC

ib1 vod/2 –vod/2 ib2

+ +

vid/2 ~ hfeib1 hfeib2 ~ –vid/2

hie hie

ve

RE

Figura 6.3. Circuito de pequeña señal simplificado del amplificador diferencial en modo diferencial (hoe=hre=0).

Resolviendo las ecuaciones de 6.7 se llega fácilmente a la siguiente relación

(i b1 + i b2 )(h ie / 2 + (1 + h fe )R E ) = 0 (6.8)

siendo la única solución posible

i b1 = − i b 2

(6.9)

resultando que

ve = 0

(6.10)

La ecuación (6.10) indica que la tensión de pequeña señal en el emisor de los transistores es nula, es decir,

que ese nudo se comporta como un nudo de masa virtual; no hay que confundirla con la masa real del circuito.

Por consiguiente, analizar el circuito de la figura 6.3 es equivalente a analizar los circuitos equivalentes del

amplificador diferencial en modo diferencial mostrados en las figuras 6.4.a y 6.4.b. La ganancia en tensión en

modo diferencial de este amplificador es

v /2 h R

A d = od = − fe C

v id / 2 h ie

(6.11)

I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001 – 103 –

Electronica Básica para Ingenieros

La impedancia de entrada del circuito de la figura 6.4 es Zi=hie. Por consiguiente, la impedancia de entrada

vista a través de los dos terminales de entrada diferencial es

Z id = 2 h ie . (6.12)

RC

RC

ib1 vod/2

vod/2 +

vid/2 ~ hfeib1

+ Q1 hie

vid/2 ~

Masa virtual Masa virtual

a) b)

Figura 6.4. Circuitos equivalente del amplificador diferencial en modo diferencial a) en alterna, b ) en pequeña

señal (hoe=hre=0).

• Ganancia en modo común

En la figura 6.5 aparece el circuito equivalente del amplificador diferencial cuando únicamente se considera

modo común a la entrada. Para obtener un circuito más simplificado se va a determinar en primer lugar las

impedancias equivalentes Ze1 y Ze2 vista a través de los emisores de los transistores Q1 y Q2. Estas impedancias

se definen como

v ve ve ve

Z e1 = e = y Z e2 = =

i e1 i b1 + h fe i b1 i e 2 i b 2 + h fe i b 2 (6.13)

RC RC

ib1 voc voc ib2

+ +

vic ~ ~ vic

hfeib1 hfeib2

hie

ve

ie1 ie2

Ze1 Ze2

RE

Figura 6.5. Amplificador diferencial en modo común. (hoe=hre=0).

Analizando el circuito de la figura 6.5 se obtiene la siguiente ecuación

v ic = i b1h ie − i b 2 h ie + v ic (6.14)

que permite demostrar que

i b1 = i b 2 (6.15)

– 104 – I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001

Tema 6

Por otra parte, la tensión ve se puede expresar como

v e = (i b1 + h fe i b1 + i b 2 + h fe i b 2 )R E (6.16)

RC RC

ib1 voc

voc +

vic ~ hfeib1

+ Q1 hie

vic ~

2RE 2RE

a) b)

Figura 6.6. Circuitos equivalente del amplificador diferencial en modo común a) en alterna, b ) en pequeña

señal (hoe=hre=0).

y utilizando las ecuaciones 6.13, 6.14 y 6.15 fácilmente se demuestra que

Z e1 = Z e 2 = 2 R E

(6.17)

Luego, los emisores de Q1 y Q2 “ven” una resistencia equivalente expresada en 6.17 de forma que el

circuito de la figura 6.5 se transforma en los circuitos equivalentes más sencillos mostrados en la figuras 6.6.a y

6.6.b. Fácilmente se demuestra que la ganancia en modo común es

v v h fe R C

A c = o1 = oc = −

v ic v ic h ie + 2 R E (1 + h fe )

(6.18)

• Relación de rechazo en modo común

Un amplificador diferencial ideal tiene una tensión de salida proporcional a vid y no depende de la

componente en modo común (Ac=0). En la práctica no sucede así y para medir esa desviación se introduce el

concepto de relación de rechazo en modo común RRMC; en inglés common-mode rejection ratio o CMRR. Se

define la RRMC como la relación entre la ganancia en modo diferencial y modo común

Ad

RRMC =

Ac (6.19)

que a veces se expresa en decibelios como

A

RRMC (dB) = 20 log10 d

Ac

(6.20)

6.3.- Amplificador diferencial bipolar con fuente de corriente

En la etapa diferencial anterior una RRMC muy elevada exige una RE grande; en el caso ideal RRMC→∞ si

I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001 – 105 –

Electronica Básica para Ingenieros

RE→∞. Sin embargo, la polarización del transistor es fuertemente dependiente del valor de esta resistencia. Una

alternativa que se utiliza en la práctica consiste en sustituir la resistencia RE por una fuente de corriente. De esta

manera, la polarización del circuito puede realizarse con facilidad y la RRMC es muy elevada ya que una fuente

de corriente presenta una impedancia interna muy alta.

VCC VCC

IC1 IC2 lineal

RC RC IEE

vo1 vo2

IEE/2

Q1 Q2

+ + 0

vi1 ~ ~ vi2

–2VT 0 +2V vid

T

IEE

a) b)

Figura 6.7. a) Amplificador diferencial polarizado con fuente de corriente. b ) Característica de transferencia del circuito.

En la figura 6.7.a se muestra un amplificador diferencial polarizado con una fuente de corriente de valor IEE.

Esta corriente se reparte simétricamente en ambos transistores resultando que en continua

I

I C1 ≈ I C2 ≈ EE

2 (6.21)

Cuando se aplica una tensión de entrada diferencial, la suma de corriente en ambos transistores se mantiene

constante a IEE, es decir,

I C1 + I C2 = I EE (6.22)

Esto significa que un incremento de corriente en un transistor origina una disminución de corriente en la

misma proporción en el otro transistor. La gráfica de la figura 6.7.b presenta la característica de transferencia del

amplificador cuando se aplica una tensión en modo diferencial. Este circuito opera con tensiones máximas de

entrada en modo diferencial bajas; del orden de 100mV~4VT. Superado este valor uno de los transistores se corta

y por el otro circula toda la corriente IEE. Las características de transferencia son lineales en una pequeña región

de operación (±2VT). Una modificación de este amplificador para que trabaje con tensiones en modo diferencial

mayores consiste en añadir una resistencia de emisor tal como se describe en la figura 6.8.a. Este circuito

mantiene la simetría de un amplificador diferencial aumentando el rango de tensiones de entrada. Este efecto se

puede observar claramente en la figura 6.8.b en donde la característica de transferencia tiene un rango de entrada

lineal mayor según aumenta RE. El inconveniente es que la ganancia en modo diferencial disminuye. Para este

circuito, se puede demostrar que si hre=hoe=0, la ganancia en modo diferencial vale

h fe R C

Ad = ±

h ie + (1 + h fe )R E

(6.23)

Valores razonables de RE deben estar comprendidos entre 50 a 100Ω ya que con valores grandes la Ad se

reduce excesivamente.

– 106 – I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001

Tema 6

VCC VCC

IC1 IC2 RE << RE >>

RC RC IEE

vo1 vo2

Q1 Q2 IEE/2

+ +

vi1 ~ ~ vi2

RE RE 0

IEE

0 vid

a) b)

Figura 6.8. a) Amplificador diferencial con resistencia de emisor. b ) Característica de transferencia del circuito

para diferentes valores de resistencia de emisor.

6.3.1.- Amplificador diferencial con carga activa

Las fuentes de corriente pueden ser utilizadas como carga activa en un amplificador diferencial. El espejo de

corriente es el circuito que mejor se adapta al tener una resistencia interna no demasiado elevada la cual elimina

problemas de polarización y mantiene una ganancia muy alta. La figura 6.9.a muestra la estructura de un

amplificador diferencial que tiene una carga activa constituida por el espejo de corriente formado por los

transistores PNP Q3, Q4 y Q5. Por necesidades de polarización la intensidad de referencia de este espejo tiene

que ser la mitad de IEE ya que las intensidades de colector de Q1 y Q4, y Q2 y Q3 deben ser idénticas.

Fácilmente se puede comprobar aplicando las propiedades de simetría del amplificador diferencial que la ganancia

en modo diferencial es

−1 −1

h oep || h oen

A d = − h fe

h ie (6.24)

donde hoep y hoen es la resistencia de salida de un transistor PNP y NPN respectivamente.

VCC VCC

Q4 Q4

Q5 Q3 Q3

vo

vo1 vo2

IEE/2

Q2 Q1 Q2

+ Q1 + +

+

vi1 ~ IEE/2 IEE/2 ~ vi2 vi1 ~ ~ vi2

IEE IEE

a) b)

Figura 6.9. Amplificador diferencial con a) carga activa y b ) carga activa modificada.

En la figura 6.9.b se presenta un amplificador diferencial con una carga activa constituida por un espejo de

corriente (Q3,Q4) que necesita menos dispositivos que el caso anterior. Tiene una única salida que proporciona

I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001 – 107 –

Electronica Básica para Ingenieros

una conversión de entrada diferencial-salida simple (differential to single-ended conversion) y, aunque en

principio se rompe la simetría del amplificador diferencial, este circuito tiene una ganancia en modo diferencial

que se aproxima al valor expresado en la ecuación 6.24.

6.3.2.- Ejemplo de un amplificador diferencial bipolar complejo

En este apartado se va a realizar una análisis simplificado un amplificador diferencial completo de la figura

6.10 constituido por varias etapas amplificadoras conectadas en cascada. Básicamente, es un amplificador

operacional formado por una etapa diferencial de entrada (Q1,Q2), otra etapa diferencial intermedia (Q7,Q8) y la

etapa de salida en configuración de seguidor de emisor (Q9).

V CC

V CC=10V

Q5 Q6 R C1=10kΩ

R D=18.6kΩ

R C1 R C1 R E=10kΩ

R C2=17.2kΩ

Q7 Q8

hie=5kΩ

hfe=200

hie=hre=0

Z9

+ Q1 Q2

+

vi1 ~ ~ vi2 RD Q9

R C2 vo

RE

Q3 Q4

–VCC

Figura 6.10. Amplificador diferencial completo.

• Análisis DC. El análisis en continua de este amplificador se realiza suponiendo nulas las entradas vi1 y

vi2 y despreciando las corrientes de base.. En la polarización de las etapas diferenciales se utiliza dos espejos de

corriente, uno basado en transistores NPN (Q3,Q4) y otro en PNP (Q5,Q6), cuya corriente de referencia se fija a

través de RD. Si se desprecia las corrientes de base de los transistores se verifica que

2 VCC − 2 VBE

I C3 ≈ I C 4 ≈ I C5 ≈ I C6 = I EE = = 1mA

RD (6.25)

Por consiguiente, aplicando el principio de simetría a ambos amplificadores diferenciales

I

I C1 ≈ I C2 ≈ I C 7 ≈ I C8 = EE = 0.5mA

2 (6.26)

Luego, la tensión de salida

vo ≈ I C8R C2 + 3VD − VBE 9 − VCC = 0 V (6.27)

es nula en ausencia de señal.

– 108 – I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001

Tema 6

RC1 hfeib2

Masas hie

vid2 /2 RC1

vod1 /2 Q8 virtuales

ib1 vid2 /2

vid1 /2 vod2 /2 vod1 /2

Q1 vid1 /2 ib2 vod2 /2~vo

hie RC2

RC2 Z9 hfeib1

a) b)

Figura 6.11. a) Aplicación del principio de simetría al circuito de la figura 6.10; b ) Modelo equivalente de pequeña señal.

• Análisis de pequeña señal. Al despreciar el parámetro hoe los espejos de corriente son ideales

resultando que la ganancia en modo común es nula. Ello permite aplicar los principios de simetría del

amplificador diferencial en modo diferencial, reduciendo el análisis de este amplificador al circuito mostrado en la

figura 6.11.a. La tensión de salida vo es prácticamente la tensión del colector de Q8 al ser la ganancia en tensión

de la etapa de salida prácticamente 1 (se trata de una seguidor de emisor). Además, Q8 tiene como carga la

resistencia RC2 y la impedancia de entrada de Q9 que en la figura 6.11.a. se representa por Z9. El valor de Z9 es

Z 9 = h ie + (1 + h fe R E ) ≈ 2 MΩ (6.28)

Por consiguiente, se puede hacer la siguiente aproximación RC2||Z9≅RC2. La ganancia del amplificador de la

figura 6.11.a se puede obtener resolviendo el circuito equivalente de la figura 6.11.b. De esta forma,

vo v v / 2 vod 2 / 2

Ad = = od 2 / 2 = od1 = A d1A d 2 =

v id1 / 2 v id1 / 2 v id1 / 2 vod1 / 2

− h ( R || h ) − h R (6.29)

= fe C1 ie fe C2 ≈ 92 ⋅ 103

h ie h ie

Luego, la ganancia del amplificador completo

vo 1 vo A

A OL = = = d ≈ 46 ⋅ 103 vi1 +

v id 2 v id1 / 2 2 (6.30) + vo

Zid Zo

La impedancia de entrada en modo diferencial es vid AOLvid

Zid=2hie=10kΩ, y la impedancia de salida vale

vi2 –

R C2 + h ie R C2 + h ie

Z o = R E || ≅ = 110Ω

1 + h fe 1 + h fe (6.31) Figura 6 . 1 2. Modelo equivalente

simplificado del amplificador de la figura

En la figura 6.12 se muestra el modelo equivalente del 6.10.

amplificador completo.

6.4.- Amplificadores diferenciales FET

La impedancia de entrada de un amplificador diferencial puede ser muy alta si se utiliza transistores FET. La

I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001 – 109 –

Electronica Básica para Ingenieros

figura 6.13.a presenta un amplificador diferencial básico basado en los transistores NMOS, M1 y M2, cuya

polarización se realiza a través de una fuente de corriente de valor ISS con una resistencia interna RSS y la figura

6.13.b muestra el circuito equivalente de pequeña señal. Al presentar este amplificador las mismas características

de simetría descritas en el amplificador diferencial bipolar se puede utilizar la conversión a señal modo diferencial

y modo común. Por similitud, en modo diferencial el terminal fuente de estos transistores se comporta como un

nudo de masa virtual y en modo común la resistencia RSS se descompone en dos en paralelo. Aplicando estos

principios de simetría es sencillo comprobar que la ganancia en modo diferencial y común vale

A d = − gm( R D || rd )

−µR D (6.32)

Ac =

2 R SS (1 + µ ) + rd + R D

VDD VDD

RD RD

vo1 vo2 RD

RD

vo1 vo2

M1 M2

+ + + +

vi1 ~ ~ vi2 ~ vgs1 vgs2 ~

vi1 gmvgs1 rd rd vi2

gmvgs2

ISS RSS

RSS

-VSS

a) b)

Figura 6.13.a) Amplificador diferencial simple de transistores NMOS. b ) Circuito equivalente de pequeña señal.

La ganancia de este amplificador puede mejorarse utilizando cargas activas. En las figura 6.14 aparece un

amplificador diferencial NMOS con carga activa formado por los transistores M3 y M4. M3 y M4 tienen la

puerta y el drenador cortocircuitado de forma que en pequeña señal pueden ser sustituidos por un elemento

resistivo de valor rdl||1/gml (subíndice l de load). Las expresiones de la Ad y Ac son similares a las descritas en la

ecuación 6.32 sustituyendo la RD por la carga equivalente

rdl||1/gml. VDD VDD

La tecnología CMOS permite realizar también rdl||1/gml M4

M3

amplificadores diferenciales con carga activa. El amplificador de

la figura 6.15.a utiliza un espejo de corriente de transistores vo1 vo2

PMOS como carga activa y el de la figura 6.15.b otro espejo de

M1 M2

corriente autopolarizado con salida simple que realiza una + +

conversión salida simple-entrada diferencial. Em ambos casos se vi1 ~ ~ vi2

puede demostrar que, en primera aproximación, las ganancias en

modo diferencial y común valen ISS RSS

−1

A d = ±g mi ( rdl || rdi ) y A c = -VSS

2g mi R SS 1 + dl

r (6.33)

rdi Figura 6 . 1 4 . Amplificador diferencial

NMOS con carga activa.

– 110 – I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001

Tema 6

siendo el subíndice l relacionado con M3 y M4 y el subíndice i con M1 y M2.

VDD VDD

M3

M5 M4 M3 M4

vo1 vo2 vo

IDD

M1 M2 M1 M2

+ + + +

vi1 ~ ~ vi2 vi1 ~ ~ vi2

ISS RSS ISS RSS

-VSS -VSS

a) b)

Figura 6.15. Amplificador diferencial CMOS con a) espejo de corriente y b ) autopolarizado.

Los transistores JFET al tener una tecnología

+VCC

compatible con los BJT pueden ser fabricados

simultáneamente en un circuito integrado. Con ello, se

combina las características de ambos dispositivos como son

su alta impedancia de entrada (JFET) y linealidad y altas Q9 Q10

prestaciones (BJT). En la figura 6.16 se muestra un Q8

ejemplo práctico correspondiente a la etapa de entrada del

amplificador operacional TL080 de Texas Instruments que vi1 vi2

Q6 Q7 IEE

utiliza PJFET como transistores de entrada de la etapa

diferencial y transistores bipolares para polarización y

amplificación. La etapa de entrada diferencial está

Q3 vo

constituida por Q6 y Q7 cuya carga activa lo forma la

Q4

fuente de corriente Q1 y Q2; las corrientes de entrada son

Q1 Q2 Q5

del orden de pA. Q4 actúa como amplificador en

configuración seguidor de emisor con objeto de introducir

una carga de muy alto valor a Q7 y servir de etapa de

interfase con la siguiente etapa amplificadora basada en

Q5. Q3 introduce una carga similar a Q4 para mantener la -V CC

simetría de la etapa diferencial. Q8, Q9 y Q10 son fuentes 100kΩ

de corriente (Widlar y espejo de corriente respectivamente) OFFSET NULL

para polarización del circuito. Como es frecuente en los -V CC

amplificadores operacionales, factores de disimetría en la Figura 6.16. Etapa de entrada del TL080 basada en

JFET con corrección de offset.

etapa diferencial hace que en ausencia de señal de entrada

la salida no sea nula, en contra de lo que debe suceder en teoría (offset null). Para corregir este efecto, algunos

amplificadores tienen salidas al exterior que mediante un potenciómetro variable se corrige el desequilibrio de la

etapa diferencial y se anula este efecto. En la figura se indica la situación y valor típico del potenciómetro.

I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001 – 111 –

Electronica Básica para Ingenieros

Problemas

P6.1 Para el amplificador diferencial de la figura P6.3 En la figura P6.3 se muestra un amplificador

P6.1, se pide: diferencial con carga activa (transistores Q6 y

a) La tensión vo1 y vo2 en DC. Q7). ¿Qué ventajas e incovenientes presenta

b) Ganancia en modo diferencial y una carga activa frente a una carga resistiva?.

común. Para este circuito, se pide:

c) Si vi1=1.02V senwt y vi2=1.025V a) el valor adecuado de R2 para que el

senwt, determinar la vod, voc, vo1 y vo2. circuito se encuentre polarizado

Datos: hFE=100, hfe=100, hie=3333Ω, correctamente. Despreciar las

hre=hoe=0. corrientes de base.

b) Ad y Ac.

VCC VCC Datos: NPN: hie=5kΩ, hfe=100, hoe= 1/50kΩ,

hre~0. PNP: hie=6kΩ, hfe=60, hoe= 1/50kΩ,

RC RC hre~0.

vo1 vo2 VCC

Q1 Q2

+ + Q6

vi1 ~ ~ vi2 Q5 Q7

RE vo1 vo2

VCC=15 V R1

RC=RE=10kΩ Q1 Q2

+ +

–VCC R2 vi1 ~ ~ vi2

Figura P6.1

P6.2 Repetir el problema P6.1 con el circuito de la Q3 Q4

R1 =10kΩ

figura P6.2. VCC=10V

–VCC

VCC VCC

Figura P6.3

VCC=15 V

RC=6kΩ P6.4 Calcular la tensión vo1 y vo2 en continua y la

RC RC RE1=330Ω

vo1 vo2 Ad del amplificador diferencial basado en un

RE2=8kΩ

par Darlington de la figura P6.4. Datos:

Q1 Q2 hFE=90, hie=5kΩ, hfe=100, hre=hoe=0.

+ +

vi1 ~ ~ vi2

RE1 RE1

RE2

–VCC

Figura P6.2

– 112 – I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001

Tema 6

V CC V CC

VDD

RC RC

RC RC

v o1 vo2

RS RS vo1 vo2

+ +

Q1 M1 M2

v i1 ~ ~ vi2 + +

vi1 ~ ~ vi2

RE RE VDD

V CC=12V

V EE=–6V

R C=5kΩ VDD=5V

R E=50Ω R B1 RG1 RC=2kΩ

M3

R D=1k3Ω RD RG1=RG2=25kΩ

R B1=1k3Ω RB2

R B2=2k9Ω RG2

RS=10kΩ VEE –VDD

Figura P6.4 Figura P6.6

P6.7 Determinar el valor de la resistencia R para que

P6.5 Comprobar que aplicando el principio de

que el circuito de la figura P6.7 esté polarizado

simetría el amplificador diferencial de la figura

correctamente. Calcular el valor de la Ad.

P6.5 verifica las siguientes expresiones. Nota:

Datos: W 1=W2=15µm, W 3=W4=W5=30µm,

hre=hoe=0.

L1=L2=L3=L4=L5=4µm

h fe R C || L

R

NMOS: k=66µA/V 2,VT=1V, gm1=gm2=

Ad = − 2 y Ac = −

h fe R C

h ie h ie + (1 + h fe )2 R E 1mΩ– 1, rd1=rd2=100kΩ;

PMOS: k=33µA/V 2, VT=-1V, gm3=gm4=

VCC VCC gm5=0.5mΩ- 1, rd3=rd4=rd5=150kΩ.

RC RC VDD

vo1 vo2 M3

RL M5 M4

Q1 Q2 vo1 vo2

+ +

vi1 ~ ~ vi2 R

M1 M2

+ +

RE

vi1 ~ ~ vi2

–VCC IEE IEE=1mA

Figura P6.5 VDD=5 V

P6.6 Calcular la ID de los transistores NMOS del Figura P6.7

amplificador diferencial de la figura P6.6.

P6.8 Calcular la tensión vo1 y vo2 en continua y la

Determinar la Ad y la tensión de salida vo1

relación A1=vo1/ii y A2=vo2/ii del

cuando vi1=2V+0.1V senwt y vi2=2V.

amplificador de la figura P6.8. Datos:

Datos: k=33µA/V 2,VT=1V, W 1=W2=10µm, hfe=100, hie=2kΩ. Nota: Despreciar las

W 3=20µm, L 1=L2=L3=4µm. intensidades de base frente al resto de las

I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001 – 113 –

Electronica Básica para Ingenieros

intensidades del circuito. la vo.

VCC Datos: NPN: hfe=200, hie=5kΩ, hoe-1=50kΩ,

RB1 RC RC RB1 hre=0; PNP: hfe=150, hie=3kΩ, hoe-1=50kΩ,

RS hre=0

vo2 Nota: Considerar únicamente el parámetro hoe

en los transistores Q2, Q3, Q10 y Q11. En el

resto se tomará como nulo.

ii vo1

RE

P6.10 Comprobar el valor de las tensiones indicadas

RB2 RB2

RS en el esquema del amplificador operacional

MC1530 de la figura P6.10.

Nota: Despreciar las intensidades de base.

V CC=9 V RB1 =3kΩ RB2=2kΩ

RC=2.6kΩ RE=500Ω RS=600Ω

Figura P6.8 P6.11 La figura P6.11 muestra el esquema de un

amplificador operacional sencillo. Se pide:

P6.9 El circuito de la figura P6.9 es un amplificador a) Calcular las intensidades que circula

diferencial típico d e u n amplificador por cada uno de los transistores y el

operacional. Para este circuito se pide: valor de vo en continua. Utilizar los

a) Calcular las intensidades I1, I2, I3, I4, principios de simetría de los

I5 e I6 y el valor de vo en continua. amplificadores diferenciales.

Utilizar los principios de simetría de

Despreciar la IB frente a IC (IB<<IC).

los amplificadores diferenciales.

b) Determinar la potencia de disipación

Despreciar la IB frente a IC (IB<<IC).

de este circuito.

b) Calcular la ganancia en modo c) Si los transistores Q1 y Q2 tienen una

diferencial.

hFE=100, calcular las corrientes de

c) Si vi1=10mV senwt y vi2=0 V, calcular

entrada.

VCC

VCC=10V

R 1 =200Ω Q10 Q13

Q11

R 2 =17k2Ω

R 3 =33k3Ω vo

Q12

I5 I6

R2

vi1 vi2

Q1 Q4

Q2 R3 Q3

I8 I4

I7

I1 I2 I3

Q9

Q7

Q5 Q8

Q6

R1 R1

–VCC

Figura P6.9

– 114 – I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001

Tema 6

d) Obtener el modelo equivalente en oportunas.

tensión del amplificador utilizando las Datos: NPN: hfe=150, hie=5kΩ, hoe=hre=0;

aproximaciones que se consideren PNP: hfe=120, hie=4kΩ, hoe=hre=0.

Figura P6.10

VCC

VCC=15V

R C1 =20kΩ RE2

R C2 =3kΩ

RC2

R C3 =15.7kΩ

RC1 RC1 Q11

R C4 =28.6kΩ

R E1=3kΩ

R E2=2.3kΩ Q3 Q4

Q12

Q1 Q2

+ +

~ ~ vi2 RC4

vi1 vo

RC3

Q6

Q5 Q7,10 RE1

–VCC

Figura P6.11

I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001 – 115 –

Electronica Básica para Ingenieros

– 116 – I.S.B.N.:84-607-1933-2 Depósito Legal:SA-138-2001

También podría gustarte

- Proyectos de instalaciones eléctrica de baja tensiónDe EverandProyectos de instalaciones eléctrica de baja tensiónCalificación: 5 de 5 estrellas5/5 (1)

- Armónicas en Sistemas Eléctricos IndustrialesDe EverandArmónicas en Sistemas Eléctricos IndustrialesCalificación: 4.5 de 5 estrellas4.5/5 (12)

- Problemas resueltos de Hidráulica de CanalesDe EverandProblemas resueltos de Hidráulica de CanalesCalificación: 4.5 de 5 estrellas4.5/5 (7)

- Laboratorio Nro 1 - Amplificador DiferencialDocumento7 páginasLaboratorio Nro 1 - Amplificador DiferencialGustavo La Madrid100% (1)

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiDe EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiCalificación: 5 de 5 estrellas5/5 (1)

- Ejemplos de Diagramas de BodeDocumento4 páginasEjemplos de Diagramas de BodeLeslie Mardones Muñoz100% (2)

- Tipos de Liderazgo Según MAX WEBER FullDocumento6 páginasTipos de Liderazgo Según MAX WEBER FullJose Luis Montes Gonzalez67% (3)

- Complemento Actividad 2Documento12 páginasComplemento Actividad 2wilson orozcoAún no hay calificaciones

- Ampli Cadores Multietapa: Related PapersDocumento13 páginasAmpli Cadores Multietapa: Related PapersJuan BrugginkAún no hay calificaciones

- Tarea A2Documento13 páginasTarea A2luis fernando de santiago lupercioAún no hay calificaciones

- CE MT1 ArredondoDelgado Práctica07BDocumento6 páginasCE MT1 ArredondoDelgado Práctica07BDiego Armando ArredondoAún no hay calificaciones

- Laboratorio 1 2015-0Documento12 páginasLaboratorio 1 2015-0Jimmie Valverde MontalvoAún no hay calificaciones

- Lab 7-Ricardo MendietaDocumento9 páginasLab 7-Ricardo MendietaRicardo MendietaAún no hay calificaciones

- Tema7 Respuesta A.C. Del BJTDocumento10 páginasTema7 Respuesta A.C. Del BJTJulio MarinAún no hay calificaciones

- Tema 8 1 V3Documento17 páginasTema 8 1 V3Ymary MB767Aún no hay calificaciones

- Amplificador Diferencial - CON PLANTILLADocumento9 páginasAmplificador Diferencial - CON PLANTILLAdougs020598Aún no hay calificaciones

- Tracc PDFDocumento31 páginasTracc PDFKattyCalixtoAún no hay calificaciones

- Circuitos Amplificadores Con Transistores PDFDocumento9 páginasCircuitos Amplificadores Con Transistores PDFalfonsocastro03Aún no hay calificaciones

- Analoga II Analisis Amplificador (36-44)Documento9 páginasAnaloga II Analisis Amplificador (36-44)Kevin Santiago Castrillon MendezAún no hay calificaciones

- Lab 6-Ricardo MendietaDocumento9 páginasLab 6-Ricardo MendietaRicardo MendietaAún no hay calificaciones

- A Guias de Laboratorio 1Documento21 páginasA Guias de Laboratorio 1Adrian LfnsAún no hay calificaciones

- AnalógicaDocumento28 páginasAnalógicaAdlin MachacaAún no hay calificaciones

- Ibf - 1009 Lorenzana Bi 2paDocumento23 páginasIbf - 1009 Lorenzana Bi 2paIVAN LORENZANA BELLIAún no hay calificaciones

- Amplificadores MultiplesDocumento12 páginasAmplificadores MultiplesMiriam YovisAún no hay calificaciones

- Guias de Laboratorio114Documento18 páginasGuias de Laboratorio114Clases MatematicasAún no hay calificaciones

- E421 Circuitos Electrónicos - Despues Parcial (Champion)Documento28 páginasE421 Circuitos Electrónicos - Despues Parcial (Champion)Sebastian VasquezAún no hay calificaciones

- Cargas Activas BJTDocumento34 páginasCargas Activas BJTjacintoAún no hay calificaciones

- Lce1p6b Inv06Documento3 páginasLce1p6b Inv06RAMON ELIZARRARASAún no hay calificaciones

- Actividad 2Documento17 páginasActividad 2wilson orozcoAún no hay calificaciones

- Solucionariode Circuitos Electronicos IIDocumento13 páginasSolucionariode Circuitos Electronicos IIAbrhaam Navarro HerreraAún no hay calificaciones

- Recta de CargaDocumento31 páginasRecta de CargaJacoboRosasGonzalezAún no hay calificaciones

- Ee 442 Mprev 6Documento14 páginasEe 442 Mprev 6Cesar CBAún no hay calificaciones

- Guía de Práctica 3 - Amplificadores Con BJT de 1 EtapaDocumento12 páginasGuía de Práctica 3 - Amplificadores Con BJT de 1 EtapaJorge NavarroAún no hay calificaciones

- Ejemplo Polarizacion Fija de Un BJTDocumento13 páginasEjemplo Polarizacion Fija de Un BJTDamacio BarillasAún no hay calificaciones

- Lce1p5b Inv06Documento5 páginasLce1p5b Inv06Peter LunaAún no hay calificaciones

- Clase 12 Potencia AB (Autoguardado) LanderDocumento17 páginasClase 12 Potencia AB (Autoguardado) LanderLander Cordova PuellesAún no hay calificaciones

- Práctica 2Documento5 páginasPráctica 2lizbarretocvAún no hay calificaciones

- Taller - Polarizacion BJTDocumento2 páginasTaller - Polarizacion BJTOscar ZorrillaAún no hay calificaciones

- Ex. Sustitutorio Ee438 - Fiee UniDocumento12 páginasEx. Sustitutorio Ee438 - Fiee UniDavidAún no hay calificaciones

- Amplificador DiferencialDocumento10 páginasAmplificador DiferencialRoller APAún no hay calificaciones

- Semana 5. Polarizacion Del BJT2Documento80 páginasSemana 5. Polarizacion Del BJT2Eric TobarAún no hay calificaciones

- Configuracion TransistoresDocumento8 páginasConfiguracion Transistoresaresguiligan08Aún no hay calificaciones

- TE Práctica4Documento6 páginasTE Práctica4MartínBlancoLandaAún no hay calificaciones

- Amplificador DiferencialDocumento7 páginasAmplificador DiferencialAngélica TrujilloAún no hay calificaciones

- Lab 7-Ricardo MendietaDocumento8 páginasLab 7-Ricardo MendietaRicardo MendietaAún no hay calificaciones

- Practica 5 LinealDocumento11 páginasPractica 5 LinealSandy Depp0% (1)

- PROBLEMA 1 A 5 SolucionDocumento9 páginasPROBLEMA 1 A 5 Solucionchinojim20Aún no hay calificaciones

- Circuito de Polarizacion Por Divisor deDocumento5 páginasCircuito de Polarizacion Por Divisor deAlejandro PAún no hay calificaciones

- Ex. Parcial Ee438 - Fiee UniDocumento6 páginasEx. Parcial Ee438 - Fiee UniDavidAún no hay calificaciones

- Electronica - Guía22 - TBJ - RceDocumento6 páginasElectronica - Guía22 - TBJ - RcePablo SaquettoAún no hay calificaciones

- Polarizacion BTJDocumento55 páginasPolarizacion BTJmartin santa cruzAún no hay calificaciones

- Practica4 Amplificacion Ordoñez-Estrada-AbigailDocumento10 páginasPractica4 Amplificacion Ordoñez-Estrada-AbigailTirone GonzálezAún no hay calificaciones

- Ejercicios Resueltos 2bDocumento4 páginasEjercicios Resueltos 2bsamuel gonzalezAún no hay calificaciones

- Mult Iee 3Documento14 páginasMult Iee 3justin jhon gutierrez quispe100% (1)

- Ampli Cadores MultietapaDocumento12 páginasAmpli Cadores Multietapaalvin-jesus-coba-garcia-9437Aún no hay calificaciones

- Control neuronal y difuso para sistemas fotovoltaicosDe EverandControl neuronal y difuso para sistemas fotovoltaicosAún no hay calificaciones

- Experiencias sobre circuitos eléctricos en serie operados por corriente directaDe EverandExperiencias sobre circuitos eléctricos en serie operados por corriente directaAún no hay calificaciones

- AmplificadoresDocumento61 páginasAmplificadoresRaul Jacob Aligue GarberiAún no hay calificaciones

- Funciones - Jefe y GerenteDocumento2 páginasFunciones - Jefe y GerenteRaul Jacob Aligue GarberiAún no hay calificaciones

- PLC S y CaracterísticasDocumento2 páginasPLC S y CaracterísticasRaul Jacob Aligue GarberiAún no hay calificaciones

- ProgramCC PDFDocumento1 páginaProgramCC PDFRaul Jacob Aligue GarberiAún no hay calificaciones

- Program CCDocumento1 páginaProgram CCRaul Jacob Aligue GarberiAún no hay calificaciones

- FODA Desarrollo HumanoDocumento3 páginasFODA Desarrollo HumanoRaul Jacob Aligue GarberiAún no hay calificaciones

- Manual de Usuario QUADXDocumento35 páginasManual de Usuario QUADXRaul Jacob Aligue GarberiAún no hay calificaciones

- Notas Teoria Electromagnetica PDFDocumento88 páginasNotas Teoria Electromagnetica PDFRaul Jacob Aligue GarberiAún no hay calificaciones

- Unidad 5 Recursos para Mantener Armonía y EquilibrioDocumento28 páginasUnidad 5 Recursos para Mantener Armonía y EquilibrioRaul Jacob Aligue GarberiAún no hay calificaciones

- Victoria - Control 1 Contabilidad IACCDocumento4 páginasVictoria - Control 1 Contabilidad IACCclaudio hurtadoAún no hay calificaciones

- 4.petar Trabajos en AlturaDocumento2 páginas4.petar Trabajos en AlturaRommel Augusto Arnica AguedoAún no hay calificaciones

- Tutorial de Fórmula1Documento80 páginasTutorial de Fórmula1Juan AbelAún no hay calificaciones

- Derecho EconomicoDocumento6 páginasDerecho EconomicoJoaquin Mauricio CcanchiAún no hay calificaciones

- 1im16 S8 M2 Barrientos Sánchez UlisesDocumento5 páginas1im16 S8 M2 Barrientos Sánchez UlisesUlises Barrientos SánchezAún no hay calificaciones

- Formato ICA 3a Acta 989Documento8 páginasFormato ICA 3a Acta 989luis fernandoAún no hay calificaciones

- Makro PDFDocumento16 páginasMakro PDFkalin3169899Aún no hay calificaciones

- Clase 1Documento30 páginasClase 1Alexa VarelaAún no hay calificaciones

- Análisis Del PEMC Por TerminarDocumento21 páginasAnálisis Del PEMC Por TerminarIsa Campos100% (1)

- TGS Proyecto Final Rodrigo ReyesDocumento5 páginasTGS Proyecto Final Rodrigo ReyesromabegoAún no hay calificaciones

- Asientos Contables TallerDocumento10 páginasAsientos Contables TallerMateo YaimaAún no hay calificaciones

- Ley de BoyleDocumento3 páginasLey de BoyleFernanda Lujan SolisAún no hay calificaciones

- Estadística InferencialDocumento9 páginasEstadística InferencialecojaqueAún no hay calificaciones

- Lámpara Quirúrgica Stryker VisumDocumento44 páginasLámpara Quirúrgica Stryker VisumDiana Infante100% (1)

- Definicion de Pavimento-3Documento30 páginasDefinicion de Pavimento-3marjhoanAún no hay calificaciones

- Bloque 1 Fisica PrimerosDocumento3 páginasBloque 1 Fisica Primerosedriel100Aún no hay calificaciones

- Informe Diagramas ElectricosDocumento10 páginasInforme Diagramas ElectricosabigailAún no hay calificaciones

- Evaluación Ambiental Estratégica (EAE) : "Proceso de Decisión Ambiental y Sostenible para Ecuador"Documento12 páginasEvaluación Ambiental Estratégica (EAE) : "Proceso de Decisión Ambiental y Sostenible para Ecuador"anderson joel torres alzamoraAún no hay calificaciones

- ACORDEONDocumento5 páginasACORDEONGustavo HernandezAún no hay calificaciones

- Actividad Matriz de Requisitos LegalesDocumento11 páginasActividad Matriz de Requisitos LegalesGerson SuárezAún no hay calificaciones

- Trabajo Colaborativo 3 Calculo IntegralDocumento7 páginasTrabajo Colaborativo 3 Calculo Integralvictor48581Aún no hay calificaciones

- Contrato y Presupuesto Isaac MontoyaDocumento5 páginasContrato y Presupuesto Isaac MontoyaIsaac Alejandro Montoya MachadoAún no hay calificaciones

- World Donuts Informe FinalDocumento55 páginasWorld Donuts Informe FinalSandy rashell Jimenez riosAún no hay calificaciones

- A#8 Bienes y Derechos RealesDocumento5 páginasA#8 Bienes y Derechos RealesWendy ArzolaAún no hay calificaciones

- Vacuna CovidDocumento22 páginasVacuna CovidLisseth Miranda CavaAún no hay calificaciones

- Taller de Inversión - WorkbookDocumento8 páginasTaller de Inversión - WorkbookJas NorabuenaAún no hay calificaciones

- Obligación de DarDocumento13 páginasObligación de DarMónicaAún no hay calificaciones

- Absorcion PresentacionDocumento26 páginasAbsorcion PresentacionPaola Robles VásquezAún no hay calificaciones

- Reglamento Transporte y Vialidad Monclova 2024Documento40 páginasReglamento Transporte y Vialidad Monclova 2024アレハンドラ アレギン キロスAún no hay calificaciones