Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Proyectos de Circuitos Digitales

Proyectos de Circuitos Digitales

Cargado por

Jose Norberto Lopez SolanoTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Proyectos de Circuitos Digitales

Proyectos de Circuitos Digitales

Cargado por

Jose Norberto Lopez SolanoCopyright:

Formatos disponibles

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing.

INRRI TOVAR CIRCUITOS DIGITALES

PROYECTO # 1 (4.5)

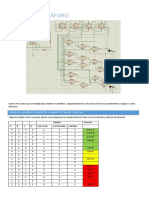

Disee un circuito lgico cuya salida es ALTA slo cuando la mayora de las entradas A, B y C son BAJAS.

TABLA DE LA VERDAD

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 X 1 1 1 0 1 0 0 0

TABLA DE KARNAUGH C AB AB AB AB 1 1 0 1 C 1 0 0 0

ABC ABC ABC ABC

X= ABC + ABC + ABC + ABC

X= AB + AC + BC

SIMPLIFICACIN CIRCUITO LOGICO

A B C X

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

PROYECTO # 2 (4.8)

La figura 4-42 muestra el diagrama de una alarma para automvil empleada para detectar ciertas condiciones no deseables. Los tres interruptores se emplean para indicar el estado en el que se encuentra la puerta del lado del conductor, el encendido y l os faros respectivamente. Disee un circuito lgico con estos tres interruptores como entradas, de manera que la alarma se active cuando se presenten cualquiera de las siguientes condiciones: Los faros estn prendidos mientras el encendido est apagado. La puerta est abierta mientras el encendido est prendido. A= Puerta, B= Encendido, C= Luces.

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

TABLA DE LA VERDAD.

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 X 0 1 0 0 0 1 1 1

SIMPLIFICACIN

C ABC AB AB ABC ABC ABC AB AB 0 0 1 0

C 1 0 1 1

X= AB + BC X= ABC + ABC + ABC + ABC

CIRCUITO LOGICO A B X

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

DIAGRAMA DE CONEXIN

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

PROYECTO # 3 (4.25) Cuatro tanques de gran capacidad de una planta qumica contien en diferentes lquidos sometidos a calentamiento. Se utilizan sensores de nivel de lquido para detectar si el nivel de los tanques A y B excede un nivel predeterminado. Los sensores de temperatura de los tanques C y D detectan cuando la temperatura de est os tanques desciende de un lmite prescrito. Suponga que las salidas A y B del sensor de nivel del liquido son BAJOS cuando el nivel es satisfactorio y ALTOS cuando es demasiado alto. Asimismo, las salidas C y D del sensor de temperatura son BAJAS cuando la temperatura es satisfactoria y ALTAS cuando la temperatura es demasiado baja. Disee un circuito lgico que detecte cuando el nivel del tanque A o B es muy alto al mismo tiempo que la temperatura ya sea en el tanque C o en el D es muy baja.

TABLA DE LA VERDAD

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 0 0 0 0 0 1 1 1 0 1 1 1 0 1 1 1

ABCD ABCD ABCD ABCD ABCD ABCD ABCD ABCD ABCD

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

X = ABCD + ABCD + ABCD + ABCD + ABCD + ABCD + ABCD + ABCD + ABCD + ABCD

SIMPLIFICACIN

CD AB AB AB AB 0 0 0 1

CD 0 1 1 1

CD 0 1 1 1

CD 0 1 1 1

X= AB + BC + BD

CIRCUITO LOGICO

A B X

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

DIAGRAMA DE CONEXIN

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

PROYECTO # 4 (4.16)

La figura 4.44 muestra un contador BCD que produce una salida de 4 bits que representa el cdigo BCD para el nmero de pulsos que se han aplicado en la entrada del contador. Por ejemplo, despus de 4 pulsos, la salidas del contador son BCBA = 01002 = 410. El contador se reajusta a 0000 2 despus del decimo pulso y comienza a contar de nuevo. En otras palabras; las salidas DCBA nunca representarn un nmero mayor que 1001 2 = 910. Disee el circuito lgico que produzca una salida en ALTO cada ve z que el valor de la cuenta sea 2, 3 9. Utilice el mapa de karnaugh y aproveche las condiciones no importa.

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

TABLA DE LA VERDAD

D 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 C 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 A 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 0 0 1 1 0 0 0 0 0 1 X X X X X X

SIMPLIFICACIN

DCBA DCBA DC DC DCBA DC DC

AB 0 0 X 0

AB 1 0 X X

AB 1 0 X X

AB 0 0 X 1

X= BC + BD + AD + DC

X= DCBA + DBCA + DBCA

CIRCUITO LOGICO D C B A X

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

DEAGRAMA DE CONEXIN

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

PROYECTO # 5 (4.26) La figura 4-50 muestra el cruce de una autopista principal con un c amino de acceso secundario. Se colocan sensores de deteccin de vehculos a lo largo de los carriles C y D (camino principal) y en los carriles A y B (camino de acceso). Las salidas del sensor son BAJAS (0) cuando no pasa ningn vehculo y ALTAS (1) cuando pasa algn vehculo. El semforo del crucero se controlar de acuerdo con la siguiente lgica:

1. El semforo E-O estar en luz verde siempre que los carriles C y D estn ocupados. 2. El semforo E-O estar en luz verde siempre que ya sea C o D estn ocupados pero A y B no lo estn. 3. El semforo N-S estar en luz verde siempre que los carriles A y B estn ocupados pero C y D no lo estn. 4. El semforo N-S tambin estar en luz verde cuando A o B estn ocupados en tanto que C y D no lo estn. 5. El semforo E-O estar en luz verde cuando no haya vehculos transitando.

Utilizando las salidas del sensor A, B, C y D como entradas, disee un circuito lgico para controlar el semforo. Debe haber dos salidas N -S y E-O, que pasen a ALTO cuando la luz correspondiente se p one verde. Simplifique el circuito lo ms que sea posible y muestre todos los pasos.

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

TABLA DE LA VERDAD

Camino de acceso A B 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 1 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1

Camino principal C D 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1

E-O 1 1 1 1 0 1 1 1 0 1 1 1 0 1 1 1

N -S 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0

NOTA: prioridad de paso al camino principal.

E-O = ABCD + ABCD + ABCD + ABCD + ABCD +ABCD + ABCD + ABCD + ABCD + ABCD +ABCD OBSERVACIN: Se tomo la salida N-S para desarrollar el circuito lgico aplicndole la simplificacin, esto se debe a que todas las condiciones que no se cumple en la salida N S se cumplen en E-O, esto quiere decir que la salida E-O es el negado de N-S.

N-S = ABCD + ABCD + ABCD

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

NS = ABCD + ABCD + ABCD

CD SIMPLIFICACIN AB AB AB AB 0 1 1 1

CD 0 0 0 0

CD 0 0 0 0

CD SALIDA N-S 0 0 0 0 NS = BCD + ACD

CIRCUITO LOGICO

A B C E-O D N-S

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

DIAGRAMA DE CONEXIN

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

PROYECTO # 6 (4.17)

La figura 4-45 muestra cuatro interruptores que son parte de la circuitera de control de una mquina copiadora. Los interruptores se encuentran en distintos puntos a lo largo del camino que recorre el papel dentro de la mquina. C ada interruptor est normalmente abierto y, cuando el papel pasa sobre el interruptor, ste se cierra. Es imposible que los interruptores S 1 y S4 se cierren al mismo tiempo. Disee un circuito lgico que genere una salida ALTO cada vez que dos o ms interr uptores estn cerrados al mismo tiempo. Utilice el mapa K y aproveche las ventajas que ofrecen las condiciones no importa.

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

TABLA DE LA VERDAD

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 X 0 0 0 1 0 1 1 1 0 X 1 1 1 X 1 X

ABCD ABCD ABCD ABCD

S1 = A S2 = B S3 = C S4 = D

ABCD ABCD ABCD ABCD

X = ABCD + ABCD + ABCD + ABCD + ABCD + ABCD + ABCD +ABCD SIMPLIFICACIN CD AB AB AB AB 0 0 1 0 CD 0 1 X X CD 1 1 X 1 CD 0 1 X = CD + B (A+C+D) + AC 1 1 X = CD + AB + BC + BD + AC

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

CIRCUITO LOGICO

A X

B C

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

DIAGRAMA DE CONEXIN

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

PROYECTO # 7 (4.22)

La figura 4-49 representa un circuito multiplicador que toma dos nme ros de 2 bits, X 1X0 y Y1Y0 y produce un numero binario de salida Z3Z2Z1Z0 que es igual al producto aritmtico de los dos nmeros de entrada. Disee el circuito lgico para el multiplicador. (sugerencia: el circuito lgico tendr cuatro entradas y cuatro sa lidas).

TABLA DE LA VERDAD

XI=D XO=C Y1=B Y0=A Z3 Z2 Z1 Z0

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 0 0 0 1 1 0 0 1 0

0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0

0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 1

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

Z0= DCBA + DCBA + DCBA + DCBA Z1= DCBA + DCBA + DCBA + DCBA + DCBA + DCBA Z2= DCBA + DCBA + DCBA Z3= DCBA

SIMPLIFICACIN DE Z0

BA DC DC DC DC 0 0 0 0

BA 0 1 1 0

BA 0 1 1 0

BA 0

Z0 = AC

0 0 0

CIRCUITO LOGICO

NOTA: Z0 ms adelante se fusionar

A Z0 B

con Z3 esto por que comparten las mismas entradas haciendo un ahorro de componentes.

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

Z1= DCBA + DCBA + DCBA + DCBA + DCBA + DCBA

SIMPLIFICACIN DE Z1

BA DC DC DC DC 0 0 0 0

BA 0 0 1 1

BA 0 1 0 1

BA 0 Z1 = ABC + BCD + ACD + ABD 1 1 0

CIRCUITO LOGICO

A B C D

Z1

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

Z2 = DCBA + DCBA + DCBA

SIMPLIFICACIN DE Z2

BA DC DC DC DC 0 0 0 0

BA 0 0 0 0

BA 0 0 0 1

BA 0 0 1 1 Z1 = ABC + BCD

CIRCUITO LOGICO

A B C D

Z2

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

Z3= DCBA

OBSERVACIN: Z3, no tiene simplificacin pero puede ser fusionado con Z 0 para reducir la cantidad de componentes y para trabajar con un solo modelo de compuerta AND.

A B C D

Z3

Z0

FUSIN

Z0

C

Z3

D B

CIRCUITO LOGICO

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

CIRCUITO DE CONEXIN INTEGRADO

Z0

Z1

Z2

Z3

REALIZADO POR: JOSE AGUILAR C.I. 11.592.018-SECCIN 3046 PROFESOR: Ing. INRRI TOVAR CIRCUITOS DIGITALES

DIAGRAMA DE CONEXIN

También podría gustarte

- Evaluaciones Aleatorias Personas 1 Del Simulador pmp21Documento69 páginasEvaluaciones Aleatorias Personas 1 Del Simulador pmp21karolina perez77% (22)

- Detalles Constructivos de Zapatas Aisladas, 8l.Documento32 páginasDetalles Constructivos de Zapatas Aisladas, 8l.Guadalupe Gomez SantizAún no hay calificaciones

- Circuitos CombinacionalesDocumento25 páginasCircuitos Combinacionaleschinguito100% (3)

- Contrato de DonaciónDocumento5 páginasContrato de Donaciónsheyla100% (1)

- Alarma de CarroDocumento3 páginasAlarma de CarroJoseCHEO83% (6)

- Alarma de CarroDocumento3 páginasAlarma de CarroJoseCHEO83% (6)

- Clase N2 Unidad IIIDocumento44 páginasClase N2 Unidad IIIGabo RojasAún no hay calificaciones

- Circuitos y Sistemas DigitalesDocumento175 páginasCircuitos y Sistemas DigitalesCarlos Espinoza100% (11)

- FactoryDocumento89 páginasFactoryJoseCHEO100% (2)

- Electronica Digital Combinacional - Diseño Teoria y PracticaDocumento300 páginasElectronica Digital Combinacional - Diseño Teoria y Practicalortiva93% (14)

- Proyecto SemaforoDocumento12 páginasProyecto SemaforoAlain Guzman100% (1)

- Proyecto SemáforoDocumento4 páginasProyecto SemáforoNorelys ArroyoAún no hay calificaciones

- TAREA1Documento6 páginasTAREA1ricardo monteroAún no hay calificaciones

- Ejercicios Bases de DatosDocumento6 páginasEjercicios Bases de Datosivonnegomez16Aún no hay calificaciones

- Binario Al CuadradoDocumento8 páginasBinario Al CuadradoAlexis Brayan Ricaldi GonzalesAún no hay calificaciones

- Trabajando Con Un Accionamiento Indramat Ecodrive03 Desde Un Siemens S7Documento17 páginasTrabajando Con Un Accionamiento Indramat Ecodrive03 Desde Un Siemens S7JoseCHEOAún no hay calificaciones

- 2do - Parcial - Circuitos Digitales 2021Documento3 páginas2do - Parcial - Circuitos Digitales 2021Kj HdAún no hay calificaciones

- Decodificador Con CompuertasDocumento3 páginasDecodificador Con CompuertasOptimusTronic100% (10)

- UNIDAD 1 - Modulo 2-ALGEBRA DE BOOLEDocumento25 páginasUNIDAD 1 - Modulo 2-ALGEBRA DE BOOLEjedison100% (18)

- Multiplexor y DemultiplexorDocumento12 páginasMultiplexor y DemultiplexorSigur Svenska100% (7)

- Cuaderno Ejercicios DigitalesDocumento42 páginasCuaderno Ejercicios Digitalesgmoivan100% (16)

- Electrónica Digital Con Ejercicios (Ampliado)Documento29 páginasElectrónica Digital Con Ejercicios (Ampliado)1011tecnologia100% (5)

- Compuertas LogicasDocumento11 páginasCompuertas LogicasSargAún no hay calificaciones

- Sesión 02. Circuitos de Electrónica DigitalDocumento19 páginasSesión 02. Circuitos de Electrónica DigitalJorge Valdeiglesias CoronadoAún no hay calificaciones

- ACO Filminas Práctico U2 Circ Combinacionales (Parte1)Documento18 páginasACO Filminas Práctico U2 Circ Combinacionales (Parte1)nataliacruzvrAún no hay calificaciones

- OAC - Evaluación Parcial - Tipo B - LOARDO QUISPE, EDGAR A.Documento5 páginasOAC - Evaluación Parcial - Tipo B - LOARDO QUISPE, EDGAR A.EDGAR AGUSTIN LOARDO QUISPEAún no hay calificaciones

- FORO LL GRUPO 3Documento11 páginasFORO LL GRUPO 3Alex GonzalezAún no hay calificaciones

- Actividad 2 - Forma Canónica y Mapas de KarnaughDocumento22 páginasActividad 2 - Forma Canónica y Mapas de KarnaughANDRES JERICO ARELLANO LUNAAún no hay calificaciones

- ArquitecturaDocumento21 páginasArquitecturadanielaAún no hay calificaciones

- Laboratorio 1Documento13 páginasLaboratorio 1Elfrugele ViscarraAún no hay calificaciones

- Diseño de Circuitos CombinatoriosDocumento46 páginasDiseño de Circuitos CombinatoriosIvan PuaAún no hay calificaciones

- TP N°2Documento19 páginasTP N°2Josue Francisco Ruben CabanaAún no hay calificaciones

- INFORME N 2 Dise o de Circuitos L Gicos 2Documento2 páginasINFORME N 2 Dise o de Circuitos L Gicos 2RODRIGO ALONZO VELASQUEZ FLORESAún no hay calificaciones

- Compuertas Logicas LaboratoriosDocumento7 páginasCompuertas Logicas Laboratoriosjhon fredy delgado peñaAún no hay calificaciones

- Lecture 2 Compuertas - MoodleDocumento38 páginasLecture 2 Compuertas - MoodleAngela Maria Benavides JojoaAún no hay calificaciones

- Circuitos DigitalesDocumento10 páginasCircuitos Digitalesalonso cadillo villanuevaAún no hay calificaciones

- Electricidad Industrial: "Puerto de Mejillones"Documento12 páginasElectricidad Industrial: "Puerto de Mejillones"Samuel DiazAún no hay calificaciones

- Actividad IIIDocumento6 páginasActividad IIIluis ortegaAún no hay calificaciones

- Ejercicio 1Documento3 páginasEjercicio 1Tim BlackAún no hay calificaciones

- Informe 2 Repaso Teorema de MorganDocumento5 páginasInforme 2 Repaso Teorema de MorganGüerrëröYöylëAún no hay calificaciones

- Arquitectura de Computadoras - Semana 04Documento31 páginasArquitectura de Computadoras - Semana 04ismael quesadaAún no hay calificaciones

- Suma de Dos Bits Mas Dos BitsDocumento10 páginasSuma de Dos Bits Mas Dos BitsAlvaro ZarabandaAún no hay calificaciones

- Sumador 3 Bits Con DisplayDocumento6 páginasSumador 3 Bits Con DisplaySaul Maza AcaroAún no hay calificaciones

- Electronica Digital Punto 3Documento5 páginasElectronica Digital Punto 3juan villaAún no hay calificaciones

- Compuertas Algebra de Boole y Teorema de MorganDocumento26 páginasCompuertas Algebra de Boole y Teorema de MorganAngela Maria Benavides JojoaAún no hay calificaciones

- SD POMALAZA - Evaluación Parcial 202110Documento8 páginasSD POMALAZA - Evaluación Parcial 202110juniorAún no hay calificaciones

- Algebra BooleanaDocumento34 páginasAlgebra BooleanaIsrael Jahdai Azpeitia CardonaAún no hay calificaciones

- Diseño y Simulación de Circuitos MSIDocumento15 páginasDiseño y Simulación de Circuitos MSIManuel Trujillo MoralesAún no hay calificaciones

- Practica 1 - DiseñoDigitalDocumento17 páginasPractica 1 - DiseñoDigitalFrancisco OrtegaAún no hay calificaciones

- Práctica 2Documento8 páginasPráctica 2Eduardo GonzalezAún no hay calificaciones

- Actividad 9 MapasDocumento4 páginasActividad 9 MapasCarolinaAún no hay calificaciones

- Practica 04. Algebra BooleanaDocumento8 páginasPractica 04. Algebra BooleanaRobertoAún no hay calificaciones

- Laura Valentina Riapira RodriguezDocumento3 páginasLaura Valentina Riapira RodriguezLaura RodríguezAún no hay calificaciones

- Practica 3Documento4 páginasPractica 3Bryam FajardoAún no hay calificaciones

- Informe 2 Sistemas DigitalesDocumento10 páginasInforme 2 Sistemas DigitalesFrancisco Hernandez Viviana CarolinaAún no hay calificaciones

- Laboratorio n5 - 11190120 - Pedro Calixtro SotoDocumento14 páginasLaboratorio n5 - 11190120 - Pedro Calixtro SotoPedro Calixtro SotoAún no hay calificaciones

- Proyecto SemáforoDocumento4 páginasProyecto SemáforoDiego AlonzoAún no hay calificaciones

- 06.anexo DDocumento15 páginas06.anexo Djesus antonioAún no hay calificaciones

- Actividad 2Documento5 páginasActividad 2Manuel Resendiz TorresAún no hay calificaciones

- Fisica Foro HoyDocumento9 páginasFisica Foro HoyJuan ManuelAún no hay calificaciones

- Ejercicios A Simular PDFDocumento49 páginasEjercicios A Simular PDFSebastian GarciaAún no hay calificaciones

- Mapas KDocumento3 páginasMapas Kchrisnino6511Aún no hay calificaciones

- Reporte 4 Lab DigitalDocumento9 páginasReporte 4 Lab DigitalJake EnglishAún no hay calificaciones

- Informe 1 Repaso Postulados y Leyes Del Algebra de BooleDocumento4 páginasInforme 1 Repaso Postulados y Leyes Del Algebra de BooleGüerrëröYöylëAún no hay calificaciones

- PRACTICA 6 - Mapa de Karnaugh-VeitchDocumento7 páginasPRACTICA 6 - Mapa de Karnaugh-VeitchNadia Irina GutierrezAún no hay calificaciones

- Curso de Electronica Digital - Trabajos Practicos 2 Al 6 (2022 1C)Documento37 páginasCurso de Electronica Digital - Trabajos Practicos 2 Al 6 (2022 1C)morena.2012.dpAún no hay calificaciones

- PRACTICA1Documento11 páginasPRACTICA1Alejandro HernándezAún no hay calificaciones

- VisionView1 4ES1Documento76 páginasVisionView1 4ES1JoseCHEOAún no hay calificaciones

- Nomenclaturas Electronicas y ElectricasDocumento47 páginasNomenclaturas Electronicas y ElectricasJoseCHEO67% (6)

- Control Semana6Documento12 páginasControl Semana6Mauricio Jara BrionesAún no hay calificaciones

- RESOLUCIÓN 56/2024 (A.N.Se.S.) Fondo de Garantía de SustentabilidadDocumento8 páginasRESOLUCIÓN 56/2024 (A.N.Se.S.) Fondo de Garantía de SustentabilidadEstudio Alvarezg AsociadosAún no hay calificaciones

- Plan de Trabajo CraDocumento3 páginasPlan de Trabajo CraAMANDA GONZALEZAún no hay calificaciones

- Losa en Dos Direcciones Concreto II.Documento11 páginasLosa en Dos Direcciones Concreto II.ORLANDO JOSE ALVARADO RODRIGUEZ100% (1)

- Informe de Mantenimiento Del Equipo SkakoDocumento5 páginasInforme de Mantenimiento Del Equipo SkakoCamilo UpeguiAún no hay calificaciones

- Cualidades y Conocimiento Que Debe Poseer Un EmpresarioDocumento4 páginasCualidades y Conocimiento Que Debe Poseer Un EmpresarioJaneth Viviana Gòmez GuillenAún no hay calificaciones

- Émonda ALR 4 Trek Bikes (MX)Documento1 páginaÉmonda ALR 4 Trek Bikes (MX)Christian GarduñoAún no hay calificaciones

- PROCEDIMIENTOS CONSTRUCTIVOS EN OBRA - Procedimiento Constructivo ARDILADocumento7 páginasPROCEDIMIENTOS CONSTRUCTIVOS EN OBRA - Procedimiento Constructivo ARDILAJuan Isai Vasques OchoaAún no hay calificaciones

- Castro Karla Programación LinealDocumento9 páginasCastro Karla Programación LinealKarla GonzalezAún no hay calificaciones

- Especif - TecnDocumento113 páginasEspecif - TecnEdgar Amador Zegarra YangaliAún no hay calificaciones

- Iau Proyecto de Grado 2020Documento153 páginasIau Proyecto de Grado 2020Hernan SemperteguiAún no hay calificaciones

- Cnss Resol 581Documento30 páginasCnss Resol 581Anamarys Gomez PinedaAún no hay calificaciones

- SECUNDARIADocumento1 páginaSECUNDARIAAngel ArguellesAún no hay calificaciones

- Analisis Granulometrico o Por TamizadoDocumento51 páginasAnalisis Granulometrico o Por TamizadoGilberto Salas Colotta67% (3)

- Acero L6Documento3 páginasAcero L6juan7j7garciaAún no hay calificaciones

- Datos de Placa de Un Motor DerrateoDocumento6 páginasDatos de Placa de Un Motor DerrateoRPBAún no hay calificaciones

- Derecho Internacional PrivadoDocumento2 páginasDerecho Internacional PrivadoKary Hernández50% (2)

- Métodos Alternativos No Podrá Ser Divulgada, Por Lo Que Será Intransferible eDocumento9 páginasMétodos Alternativos No Podrá Ser Divulgada, Por Lo Que Será Intransferible eFernando ArroyoAún no hay calificaciones

- 2da Tarea de AlgoritmosDocumento6 páginas2da Tarea de Algoritmosjesus huamaniAún no hay calificaciones

- Protocolo de Datagramas de UsuarioDocumento17 páginasProtocolo de Datagramas de UsuarioAnonymous HfBaAz81CsAún no hay calificaciones

- Sociedad EsclavistaDocumento7 páginasSociedad EsclavistaEstrella ZanabriaAún no hay calificaciones

- EMPAQUETAMIENTO HoyDocumento24 páginasEMPAQUETAMIENTO HoyEduardo Turcios100% (1)

- Inventario Vial de La AvDocumento18 páginasInventario Vial de La AvDiego Cárdenas SilveraAún no hay calificaciones

- Fiat Punto - Empleo y Cuidado PDFDocumento243 páginasFiat Punto - Empleo y Cuidado PDFDavidReyGMAún no hay calificaciones

- Act 12 JAASDocumento19 páginasAct 12 JAASMARIA JOSE SANCHEZ ORTIZAún no hay calificaciones