Documentos de Académico

Documentos de Profesional

Documentos de Cultura

19480683-Practica 1

Cargado por

rijfbrhijDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

19480683-Practica 1

Cargado por

rijfbrhijCopyright:

Formatos disponibles

Instituto Tecnológico de Nuevo León

Practica #1 Compuerta AND

Desarrollar una compuerta lógica en VHDL y generar su simulación

Nombre: Julio Cesar Torres Vazquez Mat: Diseño Digital con VHDL

Fecha 14 de septiembre de 2021

Maestro: M.I. Armando Martínez Reyes

Teoría Practica # 1

• La misión más importante de un lenguaje de descripción HW es que sea capaz de

simular perfectamente el comportamiento lógico de un circuito sin que el

programador necesite imponer restricciones.

• La herramienta Xilinx-ISE (Integrated Software Environment) es una herramienta de

diseño de circuitos profesional que nos va a permitir, entre otras funciones, la

realización de esquemáticos y su posterior simulación, así como finalmente la

síntesis en un FPGA.

Objetivo.

• Crear el proyecto en ISE Design Suite

• Utilizar la lógica combinacional para desarrollar una compuerta lógica en VHDL

Ing. Armando Martínez Reyes. Page 1

• Simulación de la aplicación

Equipo y materiales necesarios:

• Equipo de cómputo con Windows versión 8 o 10

• Software ISE Design Suite 14.7

Procedimiento:

Pasos a seguir y desarrollo de la práctica, elaborar Reporte, imágenes y link de video de

evidencia lo cual es requerido.

1. En nuestro equipo de cómputo ejecutamos el software de ISE Design Suite 14.7

2. Una vez abierto en la ventana principal seguimos la siguiente ruta File>New

Project...

Ing. Armando Martínez Reyes. Page 2

3. Nos abrirá una ventana que es el wizard para crear el workspace de nuestro

proyecto. Nos pide:

• Nombre: Nombre que tendrá la carpeta donde ese almacenará el

workspace, hay que tener en cuenta que no debe tener caracteres especiales

ni acentos, no debe empezar con un número y te recomiendo no usar

espacios sino guiones bajos.

• Ruta: La ruta donde se almacenará el proyecto, no debe tener ningún

carácter especial, las carpetas NO deben contener acentos ni espacios.

• Tipo de fuente: HDL

Una vez terminado damos clic en Next.

Ing. Armando Martínez Reyes. Page 3

4. En la siguiente ventana nos pide las especificaciones acerca de la tarjeta de

desarrollo en este caso para una Amiba 2.

• Vaciamos estos datos en los siguientes campos. Al finalizar damos clic en Next

Ing. Armando Martínez Reyes. Page 4

5. A continuación, nos mostrara un resumen. Damos clic en Finish.

6. Del lado izquierdo tenemos la zona de diseño, el workspace y abajo, el dispositivo

que estoy utilizando. Vamos a crear nuestro archivo en un módulo VHDL, doy click

en “New Source”

Ing. Armando Martínez Reyes. Page 5

7. Selecciono “VHDL Module” y le damos un nombre al archivo y la ubicación debe ser

la misma que seleccionamos en un inicio. Damos clic en Next.

Ing. Armando Martínez Reyes. Page 6

8. A continuación, en la ventana le damos un nombre a la arquitectura, también

agregamos los puertos y definimos si son entradas o salidas. Damos clic en Next.

9. Aparecerá un resumen de los datos vaciados, si todo esta correcto. Damos clic en

Finish.

Ing. Armando Martínez Reyes. Page 7

10. Completado estos pasos nos aparecerá en la ventana principal el código, dentro de

esta lo único que agregamos es el funcionamiento, Después del begin agregamos la

instrucción de la compuerta AND.

11. Después guardamos los cambios hechos en nuestro código.

12. Damos clic en Implementation>CompuertaAND>Sinthezise – XST(doble clic) . Por

último, si todo esta correcto a un costado aparecerá una flecha verde.

Ing. Armando Martínez Reyes. Page 8

13. A continuación, se realizará la simulación en la parte superior izquierda damos clic

en Simulation>CompuertaAND>ISim Simulator>Behavioral Check Syntax(doble

clic)>Simulated Behavioral Model(doble clic).

Ing. Armando Martínez Reyes. Page 9

14. A continuación, saldrá la siguiente pantalla del simulador.

15. Lo primero es reiniciar la simulación dando clic en el botón Restart.

16. Después agregamos valor a la constante. Dando clic izquierdo sobre U en la contante

a>Force Contant dentro de esta ventana en Force to value damos un valor de 0, para

ambas constantes el proceso es el mismo solo a y b.

Ing. Armando Martínez Reyes. Page 10

17. A continuación, se procede a ejecutar la simulación por un tiempo definido de 1µs.

18. Al hacer clic nos aparecerá un diagrama de tiempo en el cual podremos apreciar los

estados en los que permanecieron las contantes.

Si a=0 y b=0 la salida deberá ser c=0, por lo cual cumple como compuerta AND

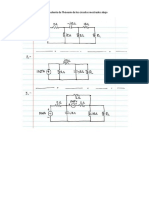

19. Ahora a las contantes les agregaremos comportamiento de reloj.

Para la constante “a”

Ing. Armando Martínez Reyes. Page 11

Ing. Armando Martínez Reyes. Page 12

Para la constante “b”

20. A continuación, se procede a ejecutar la simulación por un tiempo definido de 1µs.

Reporte

Aparecerá el diagrama de tiempo con ambas contantes a y b con comportamientos de reloj,

a partir de aquí se puede hacer el análisis de nuestra compuerta AND contra la tabla de la

verdad.

Ing. Armando Martínez Reyes. Page 13

a b c

0 0 0

a b c

1 0 0

a b c

0 1 0

a b c

1 1 1

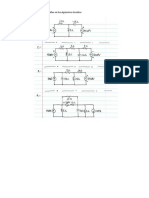

Comprobación en Logisim. Diagrama combinacional y tabla de verdad.

Ing. Armando Martínez Reyes. Page 14

Link de video de evidencia

https://youtu.be/k0ug8kNdghU

Conclusiones y referencias

La presente practica planteo como objetivo el conocer el software de ISE Desing Suite para

describir el hardware en lenguaje VHDL, también el conocer su interfaz, librerías,

arquitectura etc. y el cómo simular el código

El uso de VHDL no sólo es importante en la industria, sino también para la enseñanza ya

que provee una forma legible y estándar de especificar y describir sistemas digitales.

Referencias

intescmx. (2014). Primer proyecto en ISE Design Suite. septiembre 10, 2021, de intescmx Sitio web:

https://youtu.be/8N117AErglQ

Ing. Armando Martínez Reyes. Page 15

También podría gustarte

- Aprender React con 100 ejercicios prácticosDe EverandAprender React con 100 ejercicios prácticosAún no hay calificaciones

- Tarea 2Documento2 páginasTarea 2Vijosu Boni86% (14)

- Aprender a programar con Excel VBA con 100 ejercicios prácticoDe EverandAprender a programar con Excel VBA con 100 ejercicios prácticoCalificación: 4.5 de 5 estrellas4.5/5 (3)

- Actividad6 Pérez Padrón Edgar AbrahamDocumento18 páginasActividad6 Pérez Padrón Edgar AbrahamEdgar Perez Padron100% (1)

- Curso Completo o SCADA Vijeo Citect 6,10 Schneider ElectricDocumento63 páginasCurso Completo o SCADA Vijeo Citect 6,10 Schneider ElectricJulianodeLima100% (1)

- Aprender Autocad 2012 con 100 ejercicios prácticosDe EverandAprender Autocad 2012 con 100 ejercicios prácticosCalificación: 3 de 5 estrellas3/5 (1)

- Programación con lenguajes de guión en páginas web. IFCD0110De EverandProgramación con lenguajes de guión en páginas web. IFCD0110Aún no hay calificaciones

- Maquetación y compaginación de productos gráficos complejos. ARGP0110De EverandMaquetación y compaginación de productos gráficos complejos. ARGP0110Aún no hay calificaciones

- Aprender Adobe After Effects CS5.5 con 100 ejercicios prácticosDe EverandAprender Adobe After Effects CS5.5 con 100 ejercicios prácticosAún no hay calificaciones

- Aprender AutoCAD 2015 Avanzado con 100 ejercicios prácticosDe EverandAprender AutoCAD 2015 Avanzado con 100 ejercicios prácticosAún no hay calificaciones

- Guia #3 AnualidadesDocumento3 páginasGuia #3 AnualidadesrizzlionAún no hay calificaciones

- Laboratorio #7Documento22 páginasLaboratorio #7Nolan Alexis Rosales Sanchez0% (1)

- Gpl-Pic CDocumento9 páginasGpl-Pic CAntonio Garfias TitoAún no hay calificaciones

- Trabajo de MicrocontroladoresDocumento10 páginasTrabajo de MicrocontroladoresiwefferAún no hay calificaciones

- Informe Xilinx Laboratorio Sistemas DigitalesDocumento18 páginasInforme Xilinx Laboratorio Sistemas DigitalesJosset Aldridge AguilaAún no hay calificaciones

- Practica Con VHDLDocumento9 páginasPractica Con VHDLAle KeyAún no hay calificaciones

- Contador Ascendente y Descendente en VHDLDocumento12 páginasContador Ascendente y Descendente en VHDLStephany BradburyAún no hay calificaciones

- LAB 02 MPLAB IntroductionDocumento4 páginasLAB 02 MPLAB IntroductionJairo GuevaraAún no hay calificaciones

- Karq2 Ea U3 XXXXDocumento8 páginasKarq2 Ea U3 XXXXIkusi CuentaAún no hay calificaciones

- Que Es My Open LabDocumento13 páginasQue Es My Open LabEvelin ReyesAún no hay calificaciones

- Citect TutorialDocumento63 páginasCitect TutorialLuis Enrique CorzoAún no hay calificaciones

- Display 7 Segment OsDocumento9 páginasDisplay 7 Segment OsDaniel MateAún no hay calificaciones

- Curso de Mcu - ProteusDocumento72 páginasCurso de Mcu - ProteusWilliam Giovanny Sanchez100% (2)

- 19480683-Proyecto Final-Reloj de 24 HorasDocumento9 páginas19480683-Proyecto Final-Reloj de 24 HorasrijfbrhijAún no hay calificaciones

- Programar y Simular Con ProteusDocumento12 páginasProgramar y Simular Con ProteusIsaias Rodriguez100% (1)

- 01-Cartilla de Ejercicios Del Curso "Programación Pantallas HMI (Vijeo Designer)Documento24 páginas01-Cartilla de Ejercicios Del Curso "Programación Pantallas HMI (Vijeo Designer)hectorAún no hay calificaciones

- Tarea 1 SDI 115 2015Documento11 páginasTarea 1 SDI 115 2015Javiier UmañaAún no hay calificaciones

- Uso de Mplab y ProteousDocumento12 páginasUso de Mplab y ProteousGustavo AmericoAún no hay calificaciones

- Programacion S7-314Documento137 páginasProgramacion S7-314Luis Alberto Zapata OjedaAún no hay calificaciones

- Display - Circuitos DigitalesDocumento17 páginasDisplay - Circuitos DigitalesFranklin Jancovick Varòn HuertasAún no hay calificaciones

- Osciloscopio emDocumento17 páginasOsciloscopio emluisAún no hay calificaciones

- Aprendiendo A Programar. Microcontroladores PIC En. Lenguaje C Con CCSDocumento62 páginasAprendiendo A Programar. Microcontroladores PIC En. Lenguaje C Con CCSELPICHUE0% (1)

- P01 IDE MikroC Edicion Compilacion Simulacion y Depuracion de Un ProgramaDocumento15 páginasP01 IDE MikroC Edicion Compilacion Simulacion y Depuracion de Un ProgramaaLciLAún no hay calificaciones

- Ejemplo FlowcodeDocumento3 páginasEjemplo FlowcodeMilton Alvarez50% (2)

- Flowcode ManualDocumento19 páginasFlowcode ManualDavid GallegoAún no hay calificaciones

- P05 Programacion en Lenguaje C Con El IDE MikroC Pro For PICDocumento12 páginasP05 Programacion en Lenguaje C Con El IDE MikroC Pro For PICMarco Antonio Ergueta Yujra0% (1)

- Aprendiendo Aprogramar PIC Con CCSDocumento58 páginasAprendiendo Aprogramar PIC Con CCSAndres Raul Bruno SaraviaAún no hay calificaciones

- Guía 1 SDI 115 2013Documento10 páginasGuía 1 SDI 115 2013Estevis MongeAún no hay calificaciones

- Tutorial Sistema ScadaDocumento27 páginasTutorial Sistema ScadaRonald Pineda100% (1)

- Lectura Del Puerto Serial de Arduino Vs LabVIEWDocumento10 páginasLectura Del Puerto Serial de Arduino Vs LabVIEWRey ArturoAún no hay calificaciones

- ControlMotor CC Velocidad Sentido PDFDocumento12 páginasControlMotor CC Velocidad Sentido PDFSalimAún no hay calificaciones

- Practica 1 Compuertas Multiplexor VHDLDocumento10 páginasPractica 1 Compuertas Multiplexor VHDLshujidanAún no hay calificaciones

- Circuito Programador de Microcontroladores PicDocumento9 páginasCircuito Programador de Microcontroladores PicOvanio MolinaAún no hay calificaciones

- El Manual DeberDocumento17 páginasEl Manual DeberBerty Ibarra.CAún no hay calificaciones

- Programador Universal Microchip Picstart PlusDocumento51 páginasProgramador Universal Microchip Picstart PlusELPICHUE100% (1)

- Guía de Actividades y Rúbrica de Evaluación - Fase 0 - Actividad de PresaberesDocumento11 páginasGuía de Actividades y Rúbrica de Evaluación - Fase 0 - Actividad de PresaberesDANIELA GOMEZAún no hay calificaciones

- PIC18F4550 AsemblerDocumento297 páginasPIC18F4550 Asemblerrosemberg_trujilloAún no hay calificaciones

- Guia SubviDocumento25 páginasGuia SubviEli HaredAún no hay calificaciones

- Indice Curso de Programacion Pic en C Con CcsDocumento112 páginasIndice Curso de Programacion Pic en C Con CcsCHUCIAún no hay calificaciones

- Flowcode Manual PDFDocumento19 páginasFlowcode Manual PDFCarlos ArangurenAún no hay calificaciones

- Tecnológico Nacional de México, Campus Lázaro Cárdenas.: Compilación y Corrida de Un Programa en C++Documento11 páginasTecnológico Nacional de México, Campus Lázaro Cárdenas.: Compilación y Corrida de Un Programa en C++Giselle Valencia MorenoAún no hay calificaciones

- Compilador C CCS y Simulador Proteus para Microcontroladores PICDe EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICCalificación: 2.5 de 5 estrellas2.5/5 (5)

- Aprender Autocad 2012 Avanzado con 100 ejercicios prácticosDe EverandAprender Autocad 2012 Avanzado con 100 ejercicios prácticosAún no hay calificaciones

- Aprender Postproducción Avanzada con After Effects con 100 ejercicios prácticosDe EverandAprender Postproducción Avanzada con After Effects con 100 ejercicios prácticosAún no hay calificaciones

- Introducción a la programación en C. Un enfoque práctico.De EverandIntroducción a la programación en C. Un enfoque práctico.Aún no hay calificaciones

- Comprobación y optimización del programa cnc para el mecanizado por arranque de viruta. FMEH0109De EverandComprobación y optimización del programa cnc para el mecanizado por arranque de viruta. FMEH0109Aún no hay calificaciones

- Conexión SQL SERVER & C# (Manual para principiantes)De EverandConexión SQL SERVER & C# (Manual para principiantes)Calificación: 1 de 5 estrellas1/5 (1)

- Examen Tema 3 - Circuitos Ii1111Documento4 páginasExamen Tema 3 - Circuitos Ii1111rijfbrhijAún no hay calificaciones

- Tarea 3.111111Documento5 páginasTarea 3.111111rijfbrhijAún no hay calificaciones

- Inforelevante Infinitum299Documento2 páginasInforelevante Infinitum299rijfbrhijAún no hay calificaciones

- Tarea 2.1 - Ce-Ii1111Documento3 páginasTarea 2.1 - Ce-Ii1111rijfbrhijAún no hay calificaciones

- Tarea 1.111111Documento5 páginasTarea 1.111111rijfbrhijAún no hay calificaciones

- Tarea 3.21111Documento8 páginasTarea 3.21111rijfbrhijAún no hay calificaciones

- 19480683-Puntos 3.5 y 3.6Documento10 páginas19480683-Puntos 3.5 y 3.6rijfbrhijAún no hay calificaciones

- PRÁCTICA No. 555555555555555Documento4 páginasPRÁCTICA No. 555555555555555rijfbrhijAún no hay calificaciones

- Tarea 4.2222Documento3 páginasTarea 4.2222rijfbrhijAún no hay calificaciones

- PRÁCTICA No. 3 CIRCUITOS ELÉCTRICOS I111Documento3 páginasPRÁCTICA No. 3 CIRCUITOS ELÉCTRICOS I111rijfbrhijAún no hay calificaciones

- Tarea 5.11111111111Documento3 páginasTarea 5.11111111111rijfbrhijAún no hay calificaciones

- Tarea 4.11111111Documento3 páginasTarea 4.11111111rijfbrhijAún no hay calificaciones

- EXAMEN TEMA 4zzzzzzzzzzzzzzzDocumento3 páginasEXAMEN TEMA 4zzzzzzzzzzzzzzzrijfbrhijAún no hay calificaciones

- Examen Tema 1 - Circuitos IDocumento4 páginasExamen Tema 1 - Circuitos IrijfbrhijAún no hay calificaciones

- PLC 1111Documento1 páginaPLC 1111rijfbrhijAún no hay calificaciones

- Tarea 3.2 - 1111Documento4 páginasTarea 3.2 - 1111rijfbrhijAún no hay calificaciones

- Tarea 1.2Documento7 páginasTarea 1.2rijfbrhijAún no hay calificaciones

- Tarea 1.1Documento2 páginasTarea 1.1rijfbrhijAún no hay calificaciones

- Entre Vista 2222Documento2 páginasEntre Vista 2222rijfbrhijAún no hay calificaciones

- PRÁCTICA No.Documento13 páginasPRÁCTICA No.rijfbrhijAún no hay calificaciones

- Termistor 11111111Documento2 páginasTermistor 11111111rijfbrhijAún no hay calificaciones

- Periodo Maderista11111111Documento11 páginasPeriodo Maderista11111111rijfbrhijAún no hay calificaciones

- Ejemplo 11111Documento4 páginasEjemplo 11111rijfbrhijAún no hay calificaciones

- Etapa 3 Resumen de Los SensoresDocumento2 páginasEtapa 3 Resumen de Los SensoresrijfbrhijAún no hay calificaciones

- El Joven y La MujerDocumento5 páginasEl Joven y La MujerrijfbrhijAún no hay calificaciones

- DocDocumento5 páginasDocrijfbrhijAún no hay calificaciones

- ProbabilidadDocumento8 páginasProbabilidadrijfbrhijAún no hay calificaciones

- Ensayo Cyela111111111111111111Documento2 páginasEnsayo Cyela111111111111111111rijfbrhijAún no hay calificaciones

- Ejemplo 11Documento5 páginasEjemplo 11rijfbrhijAún no hay calificaciones

- Actividad de MetacognicionDocumento2 páginasActividad de MetacognicionrijfbrhijAún no hay calificaciones

- Ok. Silabo de DESARROLLO PERSONAL II CICLO III-2023Documento9 páginasOk. Silabo de DESARROLLO PERSONAL II CICLO III-2023Yadira Linarez100% (1)

- Tarea N°2 Conflicto Tía MaríaDocumento19 páginasTarea N°2 Conflicto Tía MaríaHéctor QuiñonezAún no hay calificaciones

- Charla Norma OIT-OSH 2001Documento11 páginasCharla Norma OIT-OSH 2001alexanderAún no hay calificaciones

- Incidencia Del Manejo Del Comercio Electronico en La Venta Del Producto Turistico en Agencias de Viajes y TurismoDocumento7 páginasIncidencia Del Manejo Del Comercio Electronico en La Venta Del Producto Turistico en Agencias de Viajes y TurismobacilioAún no hay calificaciones

- Formato Análisis de Trabajo Seguro (Ats) : Información GeneralDocumento4 páginasFormato Análisis de Trabajo Seguro (Ats) : Información GeneralMónica Cubillos100% (1)

- Tema 2 Conmutacion-Teoria v3Documento64 páginasTema 2 Conmutacion-Teoria v3anduva8Aún no hay calificaciones

- POWER BI Brochure ActualDocumento9 páginasPOWER BI Brochure Actualmasacre002Aún no hay calificaciones

- Acuerdo de Inversión de Artistas (Pro-Inversor)Documento6 páginasAcuerdo de Inversión de Artistas (Pro-Inversor)ScribdTranslationsAún no hay calificaciones

- Plan de Tesis Silupu-RamosDocumento24 páginasPlan de Tesis Silupu-RamosPercy RamosAún no hay calificaciones

- La Empresa Los Portones LtdaDocumento3 páginasLa Empresa Los Portones LtdaDorisAún no hay calificaciones

- (DIN ISO 1977 TraducidaDocumento23 páginas(DIN ISO 1977 TraducidaleandroAún no hay calificaciones

- Notas 4, 5 y 6 Costo de VentasDocumento2 páginasNotas 4, 5 y 6 Costo de VentasDenísse GonzálezAún no hay calificaciones

- Certificacion Gestion Integral Del Riesgo de DesastresDocumento2 páginasCertificacion Gestion Integral Del Riesgo de Desastresricardo martinezAún no hay calificaciones

- Caso de Estudio A2Documento3 páginasCaso de Estudio A2jota357Aún no hay calificaciones

- Informe SectorialDocumento99 páginasInforme SectorialpieecosolucionesAún no hay calificaciones

- Enunciado Pa02 TallerDocumento2 páginasEnunciado Pa02 TallerCarlinho SayanAún no hay calificaciones

- Guía 1 Expresiones AlgebraicasDocumento6 páginasGuía 1 Expresiones Algebraicasjose david rodriguezAún no hay calificaciones

- Manual Librerias BIM - LastigamaDocumento59 páginasManual Librerias BIM - LastigamaangeloAún no hay calificaciones

- 2 RISC y CISC - En.es PDFDocumento21 páginas2 RISC y CISC - En.es PDFGerald AburtoAún no hay calificaciones

- Megias Diseño de ServiciosDocumento8 páginasMegias Diseño de ServiciosZullyAún no hay calificaciones

- 3 Gestión de MantenimientoDocumento35 páginas3 Gestión de MantenimientoLuis Enrique FernandezAún no hay calificaciones

- Quartus IIDocumento34 páginasQuartus IIVictor MargueizAún no hay calificaciones

- Robot StructuralDocumento2 páginasRobot StructuralEduardo Manuel Saavedra LizarazúAún no hay calificaciones

- Jose Luis Martínez MontañoDocumento111 páginasJose Luis Martínez MontañoRigoberto GONZALEZ SUAREZAún no hay calificaciones

- Certificado 1188644668027914133875599 PDFDocumento2 páginasCertificado 1188644668027914133875599 PDFPUNTO COPIASAún no hay calificaciones

- Planificación HESA-2019-02 Hasta Primer ParcialDocumento4 páginasPlanificación HESA-2019-02 Hasta Primer ParcialAgustina EskenaziAún no hay calificaciones

- Quiz Plan de InversionDocumento10 páginasQuiz Plan de Inversionolga elizaAún no hay calificaciones

- Qué Es El Cifrado de Redes LAN Inalámbricas y Por Qué Se UtilizaDocumento6 páginasQué Es El Cifrado de Redes LAN Inalámbricas y Por Qué Se UtilizaFrs DevAún no hay calificaciones