Documentos de Académico

Documentos de Profesional

Documentos de Cultura

19480683-Proyecto Final-Reloj de 24 Horas

Cargado por

rijfbrhijTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

19480683-Proyecto Final-Reloj de 24 Horas

Cargado por

rijfbrhijCopyright:

Formatos disponibles

Instituto Tecnológico de Nuevo León

Proyecto final-Reloj de 24 Horas

Elaborar un Reloj de 24 Horas en VHDL

Nombre: Julio Cesar Torres Vazquez, Abelardo Castillo Hernández, Cristian Martin De

León Morales

Mat: Diseño Digital con VHDL

Fecha 9 de diciembre de 2021

Maestro: M.I. Armando Martínez Reyes

Teoría Proyecto final

• La misión más importante de un lenguaje de descripción HW es que sea capaz de

simular perfectamente el comportamiento lógico de un circuito sin que el

programador necesite imponer restricciones.

• La herramienta Xilinx-ISE (Integrated Software Environment) es una herramienta de

diseño de circuitos profesional que nos va a permitir, entre otras funciones, la

realización de esquemáticos y su posterior simulación, así como finalmente la

síntesis en un FPGA.

• Un decimal codificado en binario (BCD) es un contador digital en serie que cuenta

diez dígitos y se reinicia para cada nueva entrada de reloj. Como puede pasar por 10

combinaciones únicas de salida, también se le llama "contador de décadas". Un

contador BCD puede contar 0000, 0001, 0010, 1000, 1001, 1010, 1011, 1110, 1111,

0000, 0001 y así sucesivamente.

• El display ánodo común es aquel cuyos ánodos están conectados al mismo punto.

Este tipo de display es controlado por ceros, es decir que el microcontrolador o

Ing. Armando Martínez Reyes. Page 1

MCU, FPGA o microprocesador, le asigna a cada segmento un cero lógico (también

llamada tierra digital).

Objetivo.

• Crear el proyecto en ISE Design Suite

• Simulación de la aplicación

• Ejecución del programa en la tarjeta FPGA

• Aprender el manejo de la descripción por comportamiento de varios bloques

funcionales dentro del lenguaje VHDL, la cual consiste, como su nombre indica, en

describir el comportamiento de algún sistema digital.

Especificaciones:

• Se requiere el diseño y construcción de un reloj digital que cuente con 4 display los

dos primeros para visualizar las horas y los siguientes dos para los minutos. Cada vez

que se llegue a 23horas con 59 minutos, se volverá a empezar la cuenta. La siguiente

figura muestra el diagrama del bloque de este sistema

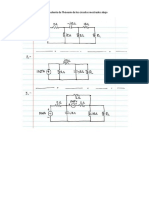

Diagrama De Bloque:

Dentro del cronómetro digital existen varios bloques funcionales, los cuales serán unidos

mediante señales. Las siguiente figura muestra los bloques funcionales del sistema

“Reloj digital”

Ing. Armando Martínez Reyes. Page 2

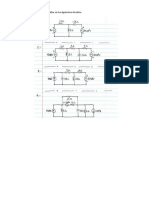

Bloques Funcionales:

Diagrama RTL

Ing. Armando Martínez Reyes. Page 3

Display 7 segmentos ánodo común

Equipo y materiales necesarios:

• Equipo de cómputo con Windows versión 8 o 10

• Software ISE Design Suite 14.7

• Tarjeta de desarrollo Amiba 2

Procedimiento:

Pasos para seguir y desarrollo de la práctica, elaborar Reporte, imágenes y link de video de

evidencia lo cual es requerido.

1. Primero agregamos las librerías a utilizar y definimos las entradas y salidas de

nuestro programa

Ing. Armando Martínez Reyes. Page 4

“Clk50mhz” será el pulso de reloj de la tarjeta Amiba2

“display” es la salida a los display definida como un vector de (7:0)

“cur_display” es la salida a los ánodos de los display definida como un vector de (3:0)

2. Después definimos la arquitectura

3. Por último, creamos el case para los display y el proceso de reset.

Ing. Armando Martínez Reyes. Page 5

Ing. Armando Martínez Reyes. Page 6

Ing. Armando Martínez Reyes. Page 7

4. Para hacer la prueba en la tarjeta Amiba2 creamos un archivo .ucf

Reporte-Simulación

Para este proyecto de reloj de 24 horas no fue necesario crear una simulación, por lo tanto,

procedimos a crear el archivo .ucf y programarlo a la tarjeta Amiba 2.

Link de video de evidencia

https://youtu.be/ZO8ajWq17IM

Ing. Armando Martínez Reyes. Page 8

Conclusiones

Si bien hoy este tipo de visualizadores parecen antiguos u obsoletos, ya que en la actualidad

es muy común el uso de pantallas gráficas basadas en píxeles, el visualizador de 7

segmentos sigue siendo una excelente opción en ciertas situaciones en las que se requiera

mayor poder lumínico y trabajo en áreas hostiles, donde las pantallas de píxeles podrían

verse afectadas por condiciones ambientales adversas.

Este proyecto final nos permitió integrar los temas ya vistos en el curso de Diseño digital

con VHDL, como la Practica de Modulación de ancho de pulso en concreto nos sirvió para

ajustar los tiempos en las horas y minutos y el Contador de 0 a 9 con display para encender

o desactivar los segmentos requeridos.

Ing. Armando Martínez Reyes. Page 9

También podría gustarte

- 19480683-Practica Contador de 0 A 9 Con DisplayDocumento7 páginas19480683-Practica Contador de 0 A 9 Con DisplayrijfbrhijAún no hay calificaciones

- Programación de PICDocumento18 páginasProgramación de PICOscarConradoAún no hay calificaciones

- Practica 2 PicoBlazeDocumento24 páginasPractica 2 PicoBlazeAntonio David EscobarAún no hay calificaciones

- Implementación de un multiplicador de 2 bits en CDocumento6 páginasImplementación de un multiplicador de 2 bits en CDiego BonecchiAún no hay calificaciones

- Centro de Estudios Científicos y Tecnológicos No.9 "Juan de Dios Bátiz" Arquitectura de Microprocesadores Y MicrocontroladoresDocumento16 páginasCentro de Estudios Científicos y Tecnológicos No.9 "Juan de Dios Bátiz" Arquitectura de Microprocesadores Y MicrocontroladoresNúñez Salazar DiegoAún no hay calificaciones

- Display de 7 SegmentosDocumento9 páginasDisplay de 7 SegmentosLuis PeñaAún no hay calificaciones

- Practica No.4 - Sandoval Frias DavidDocumento10 páginasPractica No.4 - Sandoval Frias DavidDavid Sandoval FriasAún no hay calificaciones

- Reductor de Frecuencia PDFDocumento8 páginasReductor de Frecuencia PDFAlejandro AlvarezAún no hay calificaciones

- Compilador C CCS y Simulador Proteus para Microcontroladores PICDe EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICCalificación: 2.5 de 5 estrellas2.5/5 (5)

- Ttarea6 Grupo24Documento13 páginasTtarea6 Grupo24Carlos Eduardo Rengifo AvilaAún no hay calificaciones

- Multiplicador divisor PIC16F887Documento11 páginasMultiplicador divisor PIC16F887Saira Guadalupe Ramírez TrejoAún no hay calificaciones

- 3 LCD AdcDocumento21 páginas3 LCD Adcjhonny espitiaAún no hay calificaciones

- Infoplc Net Manual Formacion Vijeo DesignerDocumento130 páginasInfoplc Net Manual Formacion Vijeo Designerluis francisco pereiraAún no hay calificaciones

- Microcontroladores PIC Parte 3Documento70 páginasMicrocontroladores PIC Parte 3number2013Aún no hay calificaciones

- PROYECTO2 4bitsDocumento13 páginasPROYECTO2 4bitsJESUS JARED SANCHEZ PINEDAAún no hay calificaciones

- Chess ClockDocumento8 páginasChess ClockCristian GomezAún no hay calificaciones

- Primeros Pasos Pic 2018Documento192 páginasPrimeros Pasos Pic 2018daniel gonzalez martinezAún no hay calificaciones

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeDe EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeAún no hay calificaciones

- Vijeo Designer Manual de FormacionDocumento258 páginasVijeo Designer Manual de FormacionJulio Antonio Guerrero CofreAún no hay calificaciones

- Manual Formacion Vijeo DesignerDocumento130 páginasManual Formacion Vijeo DesignernegonzaAún no hay calificaciones

- Caracteristicas MultisimDocumento7 páginasCaracteristicas MultisimCarlos Hernandez100% (1)

- Lab 9Documento13 páginasLab 9Ronny Rodrigo Rivera CaballeroAún no hay calificaciones

- Dmpa Once.Documento10 páginasDmpa Once.CRIS ERIK ARISTE MANRIQUEAún no hay calificaciones

- Pract Lab 4 Dig 2Documento3 páginasPract Lab 4 Dig 2Josue ChavarriaAún no hay calificaciones

- Informe Laboratorio Dirigido Microcontroladores (Puntos)Documento10 páginasInforme Laboratorio Dirigido Microcontroladores (Puntos)compressAún no hay calificaciones

- Informe 4 LCDDocumento23 páginasInforme 4 LCDJonathan RuizAún no hay calificaciones

- Cronometro Digital Con PsoCDocumento4 páginasCronometro Digital Con PsoCSEBASTIAN DAVID PINTOR AHUMADAAún no hay calificaciones

- Xilinx ISE TutorialDocumento30 páginasXilinx ISE TutorialJavier Balam BasoraAún no hay calificaciones

- Informe Probeta A FatigaDocumento11 páginasInforme Probeta A FatigaJosué PánchezAún no hay calificaciones

- Funcionamiento LCD para FPGADocumento4 páginasFuncionamiento LCD para FPGAMichael ßermeoAún no hay calificaciones

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Practica 7-DerlisDocumento8 páginasPractica 7-DerlisSaira Guadalupe Ramírez TrejoAún no hay calificaciones

- Mplab C18Documento56 páginasMplab C18kone_acm100% (1)

- Letrero LCD con ArduinoDocumento21 páginasLetrero LCD con ArduinoRicardo RamirezAún no hay calificaciones

- Construye Un LCD para I2CDocumento7 páginasConstruye Un LCD para I2CmazacotesAún no hay calificaciones

- Informe 2..1Documento10 páginasInforme 2..1RICHARD ALEXANDER PAUCAR FONSECAAún no hay calificaciones

- Informe Robo y MicroDocumento17 páginasInforme Robo y MicrojefersonAún no hay calificaciones

- Informe AdcDocumento14 páginasInforme AdcJuaanGoo AlvarezAún no hay calificaciones

- Dmpa 11Documento12 páginasDmpa 11Wilber Franz Toledo MamaniAún no hay calificaciones

- Practica #2 Control de Un Display de 7 SegmentosDocumento9 páginasPractica #2 Control de Un Display de 7 SegmentosJuan Pablo Garcia LanderoAún no hay calificaciones

- Informe de Laboratorio N3 LCDDocumento4 páginasInforme de Laboratorio N3 LCDJose Miguel LariosAún no hay calificaciones

- Informe de Laboratorio 1Documento6 páginasInforme de Laboratorio 1Andres SuarezAún no hay calificaciones

- Practica 3 William Hita MendozaDocumento5 páginasPractica 3 William Hita MendozaKmilo Andres Vargas VegaAún no hay calificaciones

- ALTIUMDocumento5 páginasALTIUMSergio VeraAún no hay calificaciones

- Especialización Profesional en Microcontroladores Pic de 8 Bits BrouchureDocumento15 páginasEspecialización Profesional en Microcontroladores Pic de 8 Bits BrouchureSergio SergioAún no hay calificaciones

- Tarea 4.1.jose Angel Garcia SelvanDocumento4 páginasTarea 4.1.jose Angel Garcia SelvanFranciscoAún no hay calificaciones

- MicrocontroladoresDocumento12 páginasMicrocontroladoresalvaro rojas mendezAún no hay calificaciones

- Practica Con VHDLDocumento9 páginasPractica Con VHDLAle KeyAún no hay calificaciones

- Tutorial MicrowindDocumento12 páginasTutorial MicrowindWilmer Huaman LlanosAún no hay calificaciones

- Controladores Industriales 2Documento28 páginasControladores Industriales 2sebastian riquelmeAún no hay calificaciones

- Display LCD - Caracteres personalizadosDocumento9 páginasDisplay LCD - Caracteres personalizadosAndrés Alejandro Martínez GuerreroAún no hay calificaciones

- Animaciones MoviconDocumento11 páginasAnimaciones MoviconmarlonAún no hay calificaciones

- PIC16F877 - MicrocontroladoresDocumento140 páginasPIC16F877 - MicrocontroladoresJuniorChavezPeralta100% (1)

- Micro Control AdoresDocumento9 páginasMicro Control AdoresMiguelAngél Callási YucraAún no hay calificaciones

- Configuración de Softwares - IntouchDocumento23 páginasConfiguración de Softwares - IntouchDavid cuasiAún no hay calificaciones

- Informe Labo 9Documento12 páginasInforme Labo 9Fati EspindolaAún no hay calificaciones

- Lab MC P3 1618200Documento9 páginasLab MC P3 1618200luis gonzalezAún no hay calificaciones

- Uso Didactico Del ProteusDocumento6 páginasUso Didactico Del Proteusruben posadasAún no hay calificaciones

- Informe 4 MicrosDocumento6 páginasInforme 4 MicrosCamilo NasAún no hay calificaciones

- PLC FestoDocumento20 páginasPLC FestoEdu RodAún no hay calificaciones

- Examen Tema 3 - Circuitos Ii1111Documento4 páginasExamen Tema 3 - Circuitos Ii1111rijfbrhijAún no hay calificaciones

- Tarea 3.21111Documento8 páginasTarea 3.21111rijfbrhijAún no hay calificaciones

- Tarea 2.1 - Ce-Ii1111Documento3 páginasTarea 2.1 - Ce-Ii1111rijfbrhijAún no hay calificaciones

- 19480683-Puntos 3.5 y 3.6Documento10 páginas19480683-Puntos 3.5 y 3.6rijfbrhijAún no hay calificaciones

- Tarea 3.111111Documento5 páginasTarea 3.111111rijfbrhijAún no hay calificaciones

- Inforelevante Infinitum299Documento2 páginasInforelevante Infinitum299rijfbrhijAún no hay calificaciones

- Tarea 4.11111111Documento3 páginasTarea 4.11111111rijfbrhijAún no hay calificaciones

- EXAMEN TEMA 4zzzzzzzzzzzzzzzDocumento3 páginasEXAMEN TEMA 4zzzzzzzzzzzzzzzrijfbrhijAún no hay calificaciones

- Tarea 1.111111Documento5 páginasTarea 1.111111rijfbrhijAún no hay calificaciones

- PRÁCTICA No.Documento13 páginasPRÁCTICA No.rijfbrhijAún no hay calificaciones

- Tarea 5.11111111111Documento3 páginasTarea 5.11111111111rijfbrhijAún no hay calificaciones

- PRÁCTICA No. 555555555555555Documento4 páginasPRÁCTICA No. 555555555555555rijfbrhijAún no hay calificaciones

- Ejemplo 11111Documento4 páginasEjemplo 11111rijfbrhijAún no hay calificaciones

- Tarea 4.2222Documento3 páginasTarea 4.2222rijfbrhijAún no hay calificaciones

- Tarea 3.2 - 1111Documento4 páginasTarea 3.2 - 1111rijfbrhijAún no hay calificaciones

- Examen Tema 1 - Circuitos IDocumento4 páginasExamen Tema 1 - Circuitos IrijfbrhijAún no hay calificaciones

- PRÁCTICA No. 3 CIRCUITOS ELÉCTRICOS I111Documento3 páginasPRÁCTICA No. 3 CIRCUITOS ELÉCTRICOS I111rijfbrhijAún no hay calificaciones

- La Toma de Ciudad Juárez clave para el triunfo maderistaDocumento11 páginasLa Toma de Ciudad Juárez clave para el triunfo maderistarijfbrhijAún no hay calificaciones

- Termistor 11111111Documento2 páginasTermistor 11111111rijfbrhijAún no hay calificaciones

- PLC 1111Documento1 páginaPLC 1111rijfbrhijAún no hay calificaciones

- Tarea 1.2Documento7 páginasTarea 1.2rijfbrhijAún no hay calificaciones

- ProbabilidadDocumento8 páginasProbabilidadrijfbrhijAún no hay calificaciones

- Tarea 1.1Documento2 páginasTarea 1.1rijfbrhijAún no hay calificaciones

- Ejemplo 11Documento5 páginasEjemplo 11rijfbrhijAún no hay calificaciones

- Entre Vista 2222Documento2 páginasEntre Vista 2222rijfbrhijAún no hay calificaciones

- Etapa 3 Resumen de Los SensoresDocumento2 páginasEtapa 3 Resumen de Los SensoresrijfbrhijAún no hay calificaciones

- DocDocumento5 páginasDocrijfbrhijAún no hay calificaciones

- Ensayo Cyela111111111111111111Documento2 páginasEnsayo Cyela111111111111111111rijfbrhijAún no hay calificaciones

- El Joven y La MujerDocumento5 páginasEl Joven y La MujerrijfbrhijAún no hay calificaciones

- Actividad de MetacognicionDocumento2 páginasActividad de MetacognicionrijfbrhijAún no hay calificaciones

- Porque La AstronomiaDocumento14 páginasPorque La Astronomiaapi-3733788100% (1)

- ?5° LAS MATEMATICAS ESTÁN EN PROBLEMAS - BLOQUE 2 Esmeralda Te Enseña?Documento17 páginas?5° LAS MATEMATICAS ESTÁN EN PROBLEMAS - BLOQUE 2 Esmeralda Te Enseña?Sandy GuzAún no hay calificaciones

- Raz MatematicoDocumento12 páginasRaz MatematicoNoemi Velazque Zuñiga100% (1)

- Hydraulic Wellhead Drive Manual SpanishDocumento39 páginasHydraulic Wellhead Drive Manual SpanishrichardAún no hay calificaciones

- E.P. Thompson - Tiempo, Disciplina de Trabajo y Capitalismo Industrial PDFDocumento30 páginasE.P. Thompson - Tiempo, Disciplina de Trabajo y Capitalismo Industrial PDFSebastian LeonAún no hay calificaciones

- 8 Reglas para Brindar Un Buen Servicio Al ClienteDocumento4 páginas8 Reglas para Brindar Un Buen Servicio Al ClienteJuan BondAún no hay calificaciones

- ACELERACIÓN Mecanismos Ejercicios 1Documento10 páginasACELERACIÓN Mecanismos Ejercicios 1MauricioAún no hay calificaciones

- CatalogueDocumento200 páginasCatalogueYasmin AvelinoAún no hay calificaciones

- Sesion de Matematica Medimos El TiempoDocumento16 páginasSesion de Matematica Medimos El TiempoLourdes SanchezAún no hay calificaciones

- Una Bicicleta para El CocodriloDocumento50 páginasUna Bicicleta para El CocodriloO Dela S YeniAún no hay calificaciones

- A00di RM UNIDocumento3 páginasA00di RM UNIZel Melquiades Ccahuana BobadillaAún no hay calificaciones

- Los Acertijos de Sam LoydDocumento169 páginasLos Acertijos de Sam Loydcarmelo_maduro100% (4)

- Minicurso de Radiestesia-SFODocumento38 páginasMinicurso de Radiestesia-SFOghadweh100% (4)

- Manual SmartwatchDocumento11 páginasManual SmartwatchNirox XeoAún no hay calificaciones

- Cronometría y Calendarios: Problemas resueltos de relojes, horas, minutos y segundosDocumento4 páginasCronometría y Calendarios: Problemas resueltos de relojes, horas, minutos y segundosEfrain Jauregui LlancoAún no hay calificaciones

- (TM) Fiat Manual de Taller Fiat Ducato 2004Documento23 páginas(TM) Fiat Manual de Taller Fiat Ducato 2004raul33% (3)

- Manual Reloj Citizen Eco DriveDocumento14 páginasManual Reloj Citizen Eco DriveAdrian LererAún no hay calificaciones

- Curso Avanzado de Radionica y RadiestesiaDocumento48 páginasCurso Avanzado de Radionica y RadiestesiaXtna Di94% (18)

- Rolex Gmt-Master-Ii EsDocumento30 páginasRolex Gmt-Master-Ii Esjaime serranoAún no hay calificaciones

- INVENTOS Epoca Medieval OriginalDocumento56 páginasINVENTOS Epoca Medieval OriginalJuniorado HMSPAún no hay calificaciones

- Raz Matematico CRONOMETRIADocumento2 páginasRaz Matematico CRONOMETRIAMaria HuamaniAún no hay calificaciones

- 161 st305sh MDocumento20 páginas161 st305sh MMan Les100% (1)

- Un tiempo para todos: farsa sobre la obra de AsforaDocumento35 páginasUn tiempo para todos: farsa sobre la obra de AsforaFrancisco LizarazoAún no hay calificaciones

- Evaluación 1 de Matemática Unidad 3Documento6 páginasEvaluación 1 de Matemática Unidad 3Juanita FabresAún no hay calificaciones

- NX990 GPS Cardio Trainer SpanishDocumento6 páginasNX990 GPS Cardio Trainer SpanishJoel Saavedra GonzalezAún no hay calificaciones

- Arbol de RelojDocumento13 páginasArbol de RelojMatheusAún no hay calificaciones

- Reloj EsDocumento17 páginasReloj EsFabiola Reyes100% (1)

- Relojes TDDocumento2 páginasRelojes TDBERRIZ DESCARGASAún no hay calificaciones

- Cómo leer un reloj analógicoDocumento6 páginasCómo leer un reloj analógicoValentina LascarAún no hay calificaciones

- Manual de Intrucciones: Con Control CTR-2Documento1 páginaManual de Intrucciones: Con Control CTR-2Carlos Alberto AndreuAún no hay calificaciones