Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Parcial 1 ARQUITECTURA DE COMPUTADORAS

Cargado por

kokobeDescripción original:

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Parcial 1 ARQUITECTURA DE COMPUTADORAS

Cargado por

kokobeCopyright:

Formatos disponibles

Solicitud de curso Tutoriales Español

Área personal - Mis cursos - IS603-1700-3-2021-653814 - TEMA 2: ESTRUCTURAS DE INTERCONEXIÓN - EXAMEN I UNIDAD III PAC 2021 IS-603 SECCIÓN 1700

IS603-1700-3-2021-

653814

1700-ARQUITECTURA DE COMPUTADORES

Participantes

Insignias Comenzado el domingo, 7 de noviembre de 2021, 20:06

Navegación por el

cuestionario

Competencias

Estado Finalizado

1 2 3 4 5

Calificaciones

Finalizado en domingo, 7 de noviembre de 2021, 21:56

6 7 8 9 10

Secciones del curso

Tiempo

1 hora 49 minutos

General

empleado 11 12 13 14 15

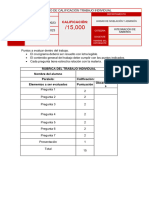

I UNIDAD Calificación 92 de 100 16 17 18 19 20

TEMA 1: CONCEPTOS

INTRODUCTORIOS

21 22 23 24

Pregunta 1

TEMA 2: ESTRUCTURAS DE

Mostrar una página cada vez

INTERCONEXIÓN

Correcta Se puntúa 3 sobre 3 Marcar pregunta

Finalizar revisión

Área personal

El bus PCI Utiliza temporización asíncrona y un esquema de arbitraje centralizado.

Inicio del sitio

Calendario

Seleccione una:

Archivos privados

Verdadero

Mis cursos

Falso

FS200-0901-3-2020-

503927

Es síncrono

DQ102-0700-3-2021- La respuesta correcta es 'Falso'

685910

IS912-2000-3-2021-

653831

IS902-1900-3-2021-

653826

Pregunta 2

Más ... Correcta Se puntúa 3 sobre 3 Marcar pregunta

Igual arquitectura y diferencias en la organización, da como resultado igual costo y rendimiento.

Seleccione una:

Verdadero

Falso

Diferente costo y rendimiento

La respuesta correcta es 'Falso'

Pregunta 3

Correcta Se puntúa 3 sobre 3 Marcar pregunta

La operación de procesamiento y almacenamiento de datos involucra únicamente al procesador y sus registros.

Seleccione una:

Verdadero

Falso

El procesador y toda la jerarquía de memoria, incluyendo los registros.

La respuesta correcta es 'Falso'

Pregunta 4

Correcta Se puntúa 3 sobre 3 Marcar pregunta

La Arquitectura del Conjunto de Instrucciones (ISA), es la interface entre el hardware y el software de alto nivel.

Seleccione una:

Verdadero

Falso

Software de bajo nivel.

La respuesta correcta es 'Falso'

Pregunta 5

Incorrecta Se puntúa 0 sobre 3 Marcar pregunta

La etapa de búsqueda de la instrucción implica varias operaciones y depende de la naturaleza de la instrucción.

Seleccione una:

Verdadero

Falso

La respuesta correcta es 'Falso'

Pregunta 6

Correcta Se puntúa 3 sobre 3 Marcar pregunta

El ancho del bus de direcciones determina la máxima capacidad de memoria posible en el sistema.

Seleccione una:

Verdadero

Falso

Su respuesta es correcta.

La respuesta correcta es 'Verdadero'

Pregunta 7

Correcta Se puntúa 3 sobre 3 Marcar pregunta

La organización de la computadora determina el software que el procesador puede ejecutar directamente.

Seleccione una:

Verdadero

Falso

Es la arquitectura

La respuesta correcta es 'Falso'

Pregunta 8

Correcta Se puntúa 3 sobre 3 Marcar pregunta

Las terminales de interrupción son líneas obligatorias del bus PCI.

Seleccione una:

Verdadero

Falso

Son opcionales

La respuesta correcta es 'Falso'

Pregunta 9

Correcta Se puntúa 3 sobre 3 Marcar pregunta

Interconectando muchas puertas lógicas que controlan el flujo de los datos, podemos construir una computadora.

Seleccione una:

Verdadero

Falso

Puertas lógicas y celdas de memoria

La respuesta correcta es 'Falso'

Pregunta 10

Correcta Se puntúa 3 sobre 3 Marcar pregunta

En la programación en hardware, para implementar un nuevo conjunto de instrucciones, el programador simplemente necesita un nuevo conjunto de señales de

control.

Seleccione una:

Verdadero

Falso

La respuesta correcta es 'Falso'

Pregunta 11

Correcta Se puntúa 5 sobre 5 Marcar pregunta

¿Cuál es el tiempo en nanosegundos requerido para transferir 1 MB desde el bus PCI hasta la memoria SDRAM, despreciar el retardo provocado por los interfaces de

bus (Host Bridge) en este caso.

a. 8.76 x 106

b. 7.51x106

c. 1.25x106

d. 4.38x106

Respuesta correcta

La respuesta correcta es:

8.76 x 106

Pregunta 12

Correcta Se puntúa 5 sobre 5 Marcar pregunta

La computadora IAS de Princeton utilizaba tecnología de:

a. Transistores

b. Tubos al vacío

c. Tubos al vacío y magnética

d. Relevadores Electromagnéticos

Respuesta correcta

La respuesta correcta es:

Tubos al vacío y magnética

Pregunta 13

Correcta Se puntúa 5 sobre 5 Marcar pregunta

Un microprocesador tiene una instrucción de incremento de memoria directo que suma 1 al valor almacenado en una posición de memoria. La instrucción tiene cinco etapas: Búsqueda de la instrucción

de (8 ciclos de reloj), calculo de la dirección del operando (6 ciclos de reloj), Búsqueda del operando (6 ciclos de reloj), suma de 1 al operando (6 ciclos de reloj), y

almacenar el operando (6 ciclos de reloj). Cuantos ciclos de reloj requiere la instrucción al insertar un 1 ciclo de reloj de espera en cada operación de lectura o

escritura?

Nota: Cuatro etapas requieren acceso a memoria

a. 24

b. 36

c. 40

d. 32

Respuesta correcta

La respuesta correcta es:

36

Pregunta 14

Correcta Se puntúa 5 sobre 5 Marcar pregunta

Disponemos de un computador con un bus de E/S que utiliza un protocolo de arbitraje Daisy Chaining. Existen cuatro (4) dispositivos periféricos conectados D1, D2, D3

y D4, siendo el dispositivo D1 el más cercano al árbitro y D4 el más alejado. En un determinado instante de tiempo D4 solicita el bus, 4 ns después lo solicita D2 y 4 ns

más tarde lo hace D1. Si las señales tardan 2 ns entre cada dispositivo. Qué dispositivo se hará con el control del bus y en qué instante de tiempo?

a. D1 en 60 ns

b. D4 en 6 ns

c. D3 en 18 ns

d. D2 en 6 ns

Respuesta correcta

La respuesta correcta es:

D2 en 6 ns

Pregunta 15

Correcta Se puntúa 5 sobre 5 Marcar pregunta

La siguiente Figura muestra el ciclo de lectura con sus señales y pasos para un protocolo de un determinado bus. Si la frecuencia de reloj es de 100 MHz, ¿cuál es el ancho de banda

alcanzado?

a. 66.66 MB/s

b. 133.32 MB/s

c. 266.66 MB/s

d. 33.33 MB/s

Respuesta correcta

La respuesta correcta es:

66.66 MB/s

Pregunta 16

Correcta Se puntúa 5 sobre 5 Marcar pregunta

Este método de arbitraje puede utilizar uno de cuatro protocolos para definir la prioridad de los dispositivos conectados al bus:

a. Daisy Chaining con una línea de prioridad

b. Centralizado Paralelo

c. Daisy Chaining con varias líneas de prioridad

d. Descentralizado

Respuesta correcta

La respuesta correcta es:

Centralizado Paralelo

Pregunta 17

Correcta Se puntúa 5 sobre 5 Marcar pregunta

La siguiente Figura muestra el ciclo de lectura con sus señales y pasos para un protocolo de un determinado bus. Si el ancho de banda es 600 MB/s. ¿Cuanto tiempo se

necesita para transferir 300 GB?

a. 536.87 segundos

b. 54.12 segundos

c. 218.43 segundos

d. 109.21 segundos

Respuesta correcta

La respuesta correcta es:

536.87 segundos

Pregunta 18

Correcta Se puntúa 5 sobre 5 Marcar pregunta

Es un ejemplo de Arquitectura:

a.

Interface entre la computadora y periféricos

b. Señales de control.

c. Codificación del ISA

d. Tecnología de memoria utilizada.

Respuesta correcta

La respuesta correcta es:

Codificación del ISA

Pregunta 19

Correcta Se puntúa 5 sobre 5 Marcar pregunta

Si las instrucciones y operandos son 32 bits y conectamos entre el procesador y memoria un bus de 8 bits. Cuántos accesos a memoria se tendrán que realizar para

transferir un dato?

a. 2

b. 4

c. 8

d. 32

Respuesta correcta

La respuesta correcta es:

4

Pregunta 20

Correcta Se puntúa 5 sobre 5 Marcar pregunta

Durante este estado del ciclo de instrucción no hay acceso a memoria:

a. Decodificación de la instrucción

b. Búsqueda operandos

c. Escritura de operando resultado

d. Búsqueda de instrucción

Respuesta correcta

La respuesta correcta es:

Decodificación de la instrucción

Pregunta 21

Correcta Se puntúa 5 sobre 5 Marcar pregunta

Etapa del ciclo de instrucción que involucra toda la jerarquía de memoria:

a. Decodificación

b. Calculo dirección de operandos

c. Ejecución

d. Búsqueda

Respuesta correcta

La respuesta correcta es:

Búsqueda

Pregunta 22

Correcta Se puntúa 5 sobre 5 Marcar pregunta

En la jerarquía de buses del sistema representado en la Figura, el número de dispositivos SCSI que se pueden conectar es:

Nota: SCSI es un bus dedicado funcional para varios dispositivos.

a. 4

b. 8

c. 16

d. 2

Respuesta correcta

La respuesta correcta es:

4

Pregunta 23

Correcta Se puntúa 5 sobre 5 Marcar pregunta

Es implementada con una memoria ROM:

a. Unidad Aritmética Lógica

b. Unidad de Control Microprogramada

c. Memoria Caché

d. Unidad de Control Cableada

Respuesta correcta

La respuesta correcta es:

Unidad de Control Microprogramada

Pregunta 24

Incorrecta Se puntúa 0 sobre 5 Marcar pregunta

Si la frecuencia del bus es de 200 MHZ y el ancho de banda es de 1600 MB/s. El número de líneas del bus de datos es:

a. 24

b. 32

c. 8

d. 64

Respuesta incorrecta.

La respuesta correcta es:

64

Finalizar revisión

Estructuras de Interconexión P… Ir a... SISTEMA DE MEMORIA PARTE 1

CAMPUS VIRTUAL ENLACES CONTÁCTENOS

Blog DEGT Repositorio T'zibal naah Dirección Ejecutiva de Gestión de Tecnología Ciudad Universitaria

Portal UNAH Repositorio Lilkaya Edificio de Biblioteca, 1er Piso

2216-3043, 2216-3044, 2216-3045, 2216-3046

Biblioteca virtual

Dirección Ejecutiva de Gestión de Tecnología

Campus Virtual Derechos Reservados 2020 Universidad Nacional Autónoma de Honduras - UNAH

También podría gustarte

- Actividad de Puntos Evaluables - Escenario 2 - Segundo Bloque-Virtual - Matemáticas - (Grupo b16)Documento6 páginasActividad de Puntos Evaluables - Escenario 2 - Segundo Bloque-Virtual - Matemáticas - (Grupo b16)valentina cardona33% (6)

- U4 - S8 - 1ra y 2da LT - Presencial - Tarea Calificada 6Documento25 páginasU4 - S8 - 1ra y 2da LT - Presencial - Tarea Calificada 6Christian Dominguez Vidaurre100% (1)

- Prueba 1 CalculoDocumento9 páginasPrueba 1 CalculoSilva AndrésAún no hay calificaciones

- Quiz Mate 1Documento6 páginasQuiz Mate 1Jorge Gomez0% (1)

- Eb Pai 3Documento104 páginasEb Pai 3LilaluAún no hay calificaciones

- Simulacro - Segundo Parcial Teórico - Preguntas A Desarrollar - Revisión Del IntentoDocumento1 páginaSimulacro - Segundo Parcial Teórico - Preguntas A Desarrollar - Revisión Del IntentoFernanda GarmendiaAún no hay calificaciones

- Prueba de Campo Eléctrico, Ley de Gauss y Potencial Eléctrico - Revisión Del IntentoDocumento1 páginaPrueba de Campo Eléctrico, Ley de Gauss y Potencial Eléctrico - Revisión Del IntentoDouglas Palma Jr.Aún no hay calificaciones

- TEST 2 - MATEMATICAS - Revisión Del IntentoDocumento1 páginaTEST 2 - MATEMATICAS - Revisión Del IntentoƳuleidƴ SanmartínAún no hay calificaciones

- TEST 1 - MATEMÁ - MergedDocumento2 páginasTEST 1 - MATEMÁ - MergedƳuleidƴ SanmartínAún no hay calificaciones

- ACTIVIDAD 6 - Aprendamos Sobre Arreglos en Programación Orientada A Objetos - Revisión Del IntentoDocumento1 páginaACTIVIDAD 6 - Aprendamos Sobre Arreglos en Programación Orientada A Objetos - Revisión Del Intentodaniel felipe charry fuentesAún no hay calificaciones

- Test 3 - MatematicasDocumento1 páginaTest 3 - MatematicasƳuleidƴ SanmartínAún no hay calificaciones

- Actividad 2 - Introducción Al Estudio de NIIF - Revisión Del IntentoDocumento1 páginaActividad 2 - Introducción Al Estudio de NIIF - Revisión Del IntentoEilleen FernandezAún no hay calificaciones

- Agenda - 80022 - CÁTEDRA UNADISTA - 2021 II PERIODO 16-4 (954) - SII 4.0Documento1 páginaAgenda - 80022 - CÁTEDRA UNADISTA - 2021 II PERIODO 16-4 (954) - SII 4.0MarCela Wilxes RodriGezAún no hay calificaciones

- EXAMEN IIB LyC 2021B - Revisión Del IntentoDocumento1 páginaEXAMEN IIB LyC 2021B - Revisión Del IntentoAriadna MarquezAún no hay calificaciones

- Mate SuperiorDocumento14 páginasMate Superiorjr sordoAún no hay calificaciones

- Revisión de Centrales2intentoDocumento1 páginaRevisión de Centrales2intentoSANTIAGO FABRICIO TORRES VACACELAAún no hay calificaciones

- (Acv-S01) Practica Calificada 01 - Calculo Avanzado para Ingenieria (47462)Documento5 páginas(Acv-S01) Practica Calificada 01 - Calculo Avanzado para Ingenieria (47462)Dennis Mejía MontalvoAún no hay calificaciones

- 2da MaquinasDocumento1 página2da MaquinasSANTIAGO FABRICIO TORRES VACACELAAún no hay calificaciones

- Tarea 4 Revision Del Intento PDFDocumento2 páginasTarea 4 Revision Del Intento PDFYordy Rodolfo Delgado RosarioAún no hay calificaciones

- Final (20pts) - Revisión Del Intento 2Documento1 páginaFinal (20pts) - Revisión Del Intento 2jeremias aquinoAún no hay calificaciones

- 4: Examen 3er. Parcial (Unidad 3.)Documento1 página4: Examen 3er. Parcial (Unidad 3.)Keyla OrtizAún no hay calificaciones

- FinalDocumento9 páginasFinalAarom Rojas LariosAún no hay calificaciones

- III Act. Evaluativa 2do. AñoDocumento4 páginasIII Act. Evaluativa 2do. AñosusanaAún no hay calificaciones

- Agenda - 112001 - Fundamentos en Gestión Integral - 2021 II Periodo 16-4 (954) - Sii 4.0Documento3 páginasAgenda - 112001 - Fundamentos en Gestión Integral - 2021 II Periodo 16-4 (954) - Sii 4.0Joice Ramos RamirezAún no hay calificaciones

- Ciclo - HV - 23-I - Qui - Semana 4Documento8 páginasCiclo - HV - 23-I - Qui - Semana 4PROFESOR ADOLFO RAMÓNAún no hay calificaciones

- NotasDocumento6 páginasNotasJOAQUIN ADRIAN SOTERO QUISPEAún no hay calificaciones

- Boleta de Notas - 171.2503.020Documento4 páginasBoleta de Notas - 171.2503.020wilson oncoyAún no hay calificaciones

- Primera Practica Calificada - Revisión Del IntentoDocumento9 páginasPrimera Practica Calificada - Revisión Del IntentoGino CaicedoAún no hay calificaciones

- Agenda - 80017 - CATEDRA UNADISTA - 2022 I PERIODO 16-01 (1141) - SII 4.0Documento3 páginasAgenda - 80017 - CATEDRA UNADISTA - 2022 I PERIODO 16-01 (1141) - SII 4.0CARLOS ANDRES SORIANO GONZALEZAún no hay calificaciones

- Actividad 1 - Introducción Al Estudio de La Contabilidad. - Revisión Del IntentoDocumento1 páginaActividad 1 - Introducción Al Estudio de La Contabilidad. - Revisión Del IntentoEilleen FernandezAún no hay calificaciones

- Rúbrica Trabajo Individual Bloque IiDocumento2 páginasRúbrica Trabajo Individual Bloque IiMateo ChalcoAún no hay calificaciones

- P2 - Tokio - Grado 9 - Idphu de Santa Marta PDFDocumento44 páginasP2 - Tokio - Grado 9 - Idphu de Santa Marta PDFLuis Alberto Rodríguez PeinadoAún no hay calificaciones

- Ciclo - HV - 23-I - Qui - Semana 5Documento10 páginasCiclo - HV - 23-I - Qui - Semana 5PROFESOR ADOLFO RAMÓNAún no hay calificaciones

- TareaDocumento7 páginasTareaWalter MendezAún no hay calificaciones

- Calendario de Actividades Académicas Jun-Jul-Ago 2022Documento3 páginasCalendario de Actividades Académicas Jun-Jul-Ago 2022Victor OchoaAún no hay calificaciones

- Cronograma Fase PlaneacionDocumento3 páginasCronograma Fase PlaneacionNeida Maria Jimenez Pabon0% (1)

- Agenda - 212033 - DISEÑO DE PLANTA - 2021 II PERIODO 16-4 (954) - SII 4.0Documento1 páginaAgenda - 212033 - DISEÑO DE PLANTA - 2021 II PERIODO 16-4 (954) - SII 4.0marcos perezAún no hay calificaciones

- Ciclo - HV - 23-I - Qui - Semana 2Documento9 páginasCiclo - HV - 23-I - Qui - Semana 2PROFESOR ADOLFO RAMÓNAún no hay calificaciones

- Idaepy 2016 31dpr0125y Región Ticul Zona 065Documento4 páginasIdaepy 2016 31dpr0125y Región Ticul Zona 065גאַבריעלאַלדאַנאַAún no hay calificaciones

- (ACV-S01) Practica Calificada 1 - CALCULO AVANZADO PARA INGENIERIA (11553)Documento6 páginas(ACV-S01) Practica Calificada 1 - CALCULO AVANZADO PARA INGENIERIA (11553)Kevin Christopher Palomino ZavalaAún no hay calificaciones

- Quimica Organica 2Documento1 páginaQuimica Organica 2Carlos YsabelAún no hay calificaciones

- Actividades 9-3 Fisica Periodo 3Documento1 páginaActividades 9-3 Fisica Periodo 3Ana Milena Alvarez RiosAún no hay calificaciones

- 1 Pract Taller ElectromecánicoDocumento5 páginas1 Pract Taller ElectromecánicoRaul RodriguezAún no hay calificaciones

- Agenda - 40002 - ETICA Y CIUDADANIA (PREGRADO) - 2021 II PERIODO 16-4 (954) - SII 4.0Documento1 páginaAgenda - 40002 - ETICA Y CIUDADANIA (PREGRADO) - 2021 II PERIODO 16-4 (954) - SII 4.0andreaAún no hay calificaciones

- CarlosDocumento8 páginasCarlosJersonAún no hay calificaciones

- Evaluación Final: Ingeniería de Métodos 1 Ingenieria IndustrialDocumento5 páginasEvaluación Final: Ingeniería de Métodos 1 Ingenieria IndustrialDenis MalquichaguaAún no hay calificaciones

- Catedra Unadista - 2021 II Periodo 16-05 (955) - Sii 4.0Documento2 páginasCatedra Unadista - 2021 II Periodo 16-05 (955) - Sii 4.0Alejandro CareAún no hay calificaciones

- Mat Exm3Documento6 páginasMat Exm3Alexander TomaláAún no hay calificaciones

- (ACV-S06) Evaluación Calificada en Linea 3 - EP2 - CALCULO AVANZADO PARA INGENIERIA (19019)Documento5 páginas(ACV-S06) Evaluación Calificada en Linea 3 - EP2 - CALCULO AVANZADO PARA INGENIERIA (19019)Elias QcheAún no hay calificaciones

- Segundo Examen Parcial PDFDocumento1 páginaSegundo Examen Parcial PDFJosé Daniel Espinal GarcíaAún no hay calificaciones

- Evaluación en Línea Unidad 1 - Revisión Del IntentoDocumento9 páginasEvaluación en Línea Unidad 1 - Revisión Del IntentoSteven DanielAún no hay calificaciones

- Agenda - 100103 - METODOLOGÍA DE LA INVESTIGACIÓN - 2021 II PERIODO 16-4 (954) - SII 4.0Documento1 páginaAgenda - 100103 - METODOLOGÍA DE LA INVESTIGACIÓN - 2021 II PERIODO 16-4 (954) - SII 4.0andreaAún no hay calificaciones

- PAT Agosto - Diciembre 2022 FinalDocumento10 páginasPAT Agosto - Diciembre 2022 FinalTroskr GallegosAún no hay calificaciones

- P2-2020 OcrDocumento20 páginasP2-2020 OcrAngelAún no hay calificaciones

- Documentos Fin de Año 2019 PDFDocumento22 páginasDocumentos Fin de Año 2019 PDFHormenio Rojas IdrogoAún no hay calificaciones

- Cronograma GeneralDocumento6 páginasCronograma GeneralNeida Maria Jimenez PabonAún no hay calificaciones

- Malla CurricuralDocumento4 páginasMalla Curricuralduvan camilo chaparroAún no hay calificaciones

- Encargatura Tercera Etapa Cuadro de Merito FinalDocumento3 páginasEncargatura Tercera Etapa Cuadro de Merito FinalWalter TurpoAún no hay calificaciones

- Evaluación 4 - Teleprocesos 2021-3Documento2 páginasEvaluación 4 - Teleprocesos 2021-3Will. MonzantAún no hay calificaciones

- Informe Eval PolitecnicaDocumento2 páginasInforme Eval PolitecnicaMiguel RamblaAún no hay calificaciones

- La isla de los delfines azules - Kit de Literatura Gr. 5-6De EverandLa isla de los delfines azules - Kit de Literatura Gr. 5-6Aún no hay calificaciones

- 27 Lineas de Vida HorizontalesDocumento13 páginas27 Lineas de Vida Horizontalesnewboy01Aún no hay calificaciones

- TALLER FINAL. Sistemas de Deteccion y Extincion de IncendiosDocumento11 páginasTALLER FINAL. Sistemas de Deteccion y Extincion de IncendiosMiltonAún no hay calificaciones

- Prueba de Evaluacion Tecnicas de Prevencion de RL IiDocumento6 páginasPrueba de Evaluacion Tecnicas de Prevencion de RL IiLIZ CIELO PAZAún no hay calificaciones

- Valores FormDocumento4 páginasValores Formadriana portelaAún no hay calificaciones

- Dimensiones de Un Producto y ServicioDocumento2 páginasDimensiones de Un Producto y ServicioCarla Natalia Quispe Alvarez100% (1)

- El Concepto Del Lenguaje. BelinchónDocumento4 páginasEl Concepto Del Lenguaje. BelinchónJuan David Diaz PaniaguaAún no hay calificaciones

- Tesis DoctoralDocumento400 páginasTesis DoctoralEsteban30Aún no hay calificaciones

- Introduccion 1Documento7 páginasIntroduccion 1Georgina RizzottoAún no hay calificaciones

- Pensamos Mal - El Gato y La CajaDocumento10 páginasPensamos Mal - El Gato y La CajaTamara GonzalezAún no hay calificaciones

- Cuaderno-De-Trabajo-Del-EstudianteDocumento169 páginasCuaderno-De-Trabajo-Del-EstudianteFERNANDO REYES FUENTESAún no hay calificaciones

- Anexo 1. Uso Del CormixDocumento67 páginasAnexo 1. Uso Del Cormixjean miguel oscorima celisAún no hay calificaciones

- El Signo Lingüístico. Clase N°1-Marzo18Documento9 páginasEl Signo Lingüístico. Clase N°1-Marzo18luis vladimir cubillos sanchezAún no hay calificaciones

- Anexo 2 - Ecuaciones Desarrollo Etapa 3 PDFDocumento4 páginasAnexo 2 - Ecuaciones Desarrollo Etapa 3 PDFJairo HurtatisAún no hay calificaciones

- La Cadena Del Valor de PorterDocumento17 páginasLa Cadena Del Valor de PorterManuel AlejandroAún no hay calificaciones

- Taller de Calculo de Varias VariablesDocumento2 páginasTaller de Calculo de Varias VariablesRonaldo Rafael Puma PillcoAún no hay calificaciones

- Diseño Construcción y Reparación de Embarcaciones NavalesDocumento2 páginasDiseño Construcción y Reparación de Embarcaciones NavalesƤeřež HelmuthAún no hay calificaciones

- Factores de Riesgo Trabajo FinalDocumento14 páginasFactores de Riesgo Trabajo FinalFrancisca MendozaAún no hay calificaciones

- Moda CircularDocumento35 páginasModa Circulartaniatrevino514Aún no hay calificaciones

- Analisis Y RESUMEN de La Obra Padre Rico Padre PobreDocumento29 páginasAnalisis Y RESUMEN de La Obra Padre Rico Padre PobreAngel Noe Castillo Mogollon100% (2)

- Manejo Integral de Malezas PDFDocumento60 páginasManejo Integral de Malezas PDFKevin PAún no hay calificaciones

- Territorios, Paisajes y Arquitectura Vernácula Sevilla PDFDocumento20 páginasTerritorios, Paisajes y Arquitectura Vernácula Sevilla PDFLina IbañezAún no hay calificaciones

- Reyno 2006 Responsabilidad SocialDocumento145 páginasReyno 2006 Responsabilidad SocialCynthiaAún no hay calificaciones

- Proyecto Interdisciplinario - Actividades - Cientifico - 8voDocumento11 páginasProyecto Interdisciplinario - Actividades - Cientifico - 8voVIDEOS JUAN PABLO IIAún no hay calificaciones

- Poi 2021Documento97 páginasPoi 2021Franz Lopez MontoyaAún no hay calificaciones

- Taller de Signos de PuntuacionDocumento2 páginasTaller de Signos de PuntuacionYirley DiazAún no hay calificaciones

- Glosario Transporte AereoDocumento10 páginasGlosario Transporte AereoMacarena BerriosAún no hay calificaciones

- Dosier Administracion Post Pandemia PDFDocumento254 páginasDosier Administracion Post Pandemia PDFJessica Alessandra Medellin RodríguezAún no hay calificaciones

- ContratoDocumento1 páginaContratoWilson DávilaAún no hay calificaciones

- Que Es Un FormatoDocumento7 páginasQue Es Un FormatojermanAún no hay calificaciones