Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Diseño de un amplificador multietapas con TBJ para aplicaciones de audio

Cargado por

Maria GonzalesDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Diseño de un amplificador multietapas con TBJ para aplicaciones de audio

Cargado por

Maria GonzalesCopyright:

Formatos disponibles

Apuntes para el diseño de un

amplificador multietapas con TBJs

Autor: Ing. Aída A. Olmos

Cátedra: Electrónica I

- Junio 2005 -

Facultad de Ciencias Exactas y Tecnología

UNIVERSIDAD NACIONAL DE TUCUMAN

Diseño de un amplificador multietapas con TBJ

Para explicar el diseño de un amplificador multietapas de audio, se planteará un

problema:

Se desea amplificar la señal de salida de auriculares de un discman para excitar

parlantes. Para ello se usará un pre-amplificador de audio, el que excitará una

etapa amplificadora de potencia. Se solicita el diseño de la etapa pre-

amplificadora, la que deberá tener las siguientes características:

Amplitud de la señal de entrada 50 [mV

Ganancia de tensión Av ≥ 100

Impedancia de entrada Zin ≥ 5 KΩ

Impedancia de salida Zout≤ 50Ω

Frecuencia de corte inferor fL< 20Hz

Frecuencia de corte superior fH>30 KHz

Resolución:

Como se necesita una ganancia mayor a 100, seguramente se necesitará más de

una etapa para lograrlo, puesto que los amplificadores de ganancia grande son

inestables. Por este motivo, se debe pensar en colocar dos etapas idénticas en

cascada para lograr que la ganancia total sea mayor a 100, como lo solicitado, y

una tercera etapa cuya impedancia de salida sea chica. Entonces, el diagrama de

bloques total será:

Elección de la fuente de alimentación:

Para comenzar con el diseño se elegirá el valor de la tensión de la fuente de

alimentación, con el siguiente criterio:

Como la señal que excitará el amplificador es de 50mV y se solicita que la

ganancia sea de 100, entonces el valor de pico de la señal de salida será:

100 x50 10−3 [V ] = 5 [V ] ;

La tensión sinusoidal de salida, se desarrollará alrededor del punto de

polarización VCE, el límite superior estará dado por el valor de VCC y el límite

inferior por la tensión de saturación de colector – emisor VCE SAT. Esto se puede

observar en la figura de abajo:

AAO Electrónica I FACET-UNT

- Página 2-

En base a lo arriba descrito, entonces la tensón de fuente deberá ser mayor o

igual que el doble de la tensión de pico. O sea :

VCC ≥ 2 x5 [V ] ≥ 10 [V ]

Por lo tanto se adopta: VCC = 12 [V ]

Cálculo de la primera etapa

A continuación se elige una configuración de amplificador. Se propone:

Esta configuración es elegida por sus conocidas características de estabilidad y

linealidad. Las características principales de esta configuración son: Ganancia

chica e impedancia de entrada y de salida grande.

AAO Electrónica I FACET-UNT

- Página 3-

Para comenzar el diseño de la etapa amplificadora propuesta, se elegirá el

elemento activo. Para ello se tendrá en cuenta el rango de frecuencia en el que

debe trabajar. En base a ello se elige el BC548B, cuyos parámetros son: β = hfe =

330, hie = 3200Ω, hre = 0; 1/hoe= 0Ω.

A continuación se adoptará:

VRC = 6[V]; para garantizar máxima excursión de salida

IC = 5 [mA]; ya que IC máx = 200[mA] según hojas de dato

Con estos dos valores se calcula R3 :

VR3

R3 = = 1.2K Ω

IC

Cálculo de la ganancia de la primera etapa

Como se solicita que la ganancia total del pre-amplificador es de 100 y se conoce

que el tipo de configuración elegida es muy estable pero su ganancia no es muy

grande, entonces, se deberá poner dos etapas idénticas en cascada, para que

ganen como mínimo 100 entre ambas. Por lo tanto cada una de ellas, debe ganar

como mínimo 10 veces o 20dB.

Se calcula la ganancia de esta etapa. Para ello se dibuja el modelo para pequeñas

señales:

En él se puede ver que:

VS = ib . hie + ie . R4 = ib . hie + (1 + h fe ) . ib . R4 = ib . hie + (1 + h fe ) . R4

VS ≈ ib . hie + h fe . R4

Esta aproximación: 1 + h fe ≈ h fe ; se puede realizar ya que hfe >>1

VO = iC . R3 = h f e . ib . R3

AAO Electrónica I FACET-UNT

- Página 4-

−iC . R3 −ib . h fe R3 − h fe R3 R3

(1) AV = = = ≈−

ib . hie + h fe . R4 ib . hie + h fe . R4 hie + h fe . R4 R4

Por lo tanto, se adopta:

R3 R

AV = − > −10 ⇒ R4 < 3 ⇒ R4 = 100Ω

R4 10

A continuación se plantea la malla externa:

(2) VCC = I p . ( R1 + R2 )

I p ≥ 10. I B

IC

I p ≥ 10. ≥ 151.5 [ µ A]

β

Como:

I p R2 = VBE + I C R4

reemplazando por el valor de Ip, se obtiene:

R2 ≤ 8580Ω , por lo tanto adopto R2 = 7200Ω

Reemplazando en (2) se obtiene: R1 = 72000Ω

Esta etapa debe excitar a otra etapa idéntica por lo tanto el modelo es:

AAO Electrónica I FACET-UNT

- Página 5-

Como se observa, la impedancia de entrada de la segunda etapa es la carga de la

primera y por lo tanto influirá en el cálculo de la ganancia de la primera etapa, ya

que se pone en paralelo con la resistencia que está en colector R3.

Al realizar el modelo híbrido de la primera etapa cargada, este queda:

Por esto, es imprescindible calcular la impedancia de entrada de la segunda

etapa, pero como la primera y la segunda etapas son idénticas:

Zi1= Zi2.

Del modelo híbrido:

Vs is ( R1 // R2 //( hie + (1 + h fe ) R4 ))

Zi = =

is is

Reemplazando por los valores correspondientes, se obtiene:

Zi = 5700Ω

Como se dijo, esta impedancia, se pone en paralelo con R3 y la ganancia de la

primera etapa queda:

R // Z i

AV =≈ − 3

R4

Al realizar los cálculos:

AV =≈ −9.9

Cálculo de la segunda etapa

La segunda etapa, será excitada por la salida de la primera etapa. A esta, no es

necesario calcularla ya que será idéntica a la primera, pero la ganancia será

distinta por que la carga de esta etapa es distinta, a ello se volverá luego de

diseñar la tercera etapa.

Cálculo de la tercera etapa

AAO Electrónica I FACET-UNT

- Página 6-

La tercera etapa debe proporcionar una impedancia de salida baja, su ganancia

no es importante ya que el requisito de ganancia será cumplido por la primera y

la segunda etapa. Por esto se elige la siguiente configuración:

Para el diseño de esta etapa, se trabajará con el mismo elemento activo que en las

anteriores. Se adopta:

VCE = 6[V]

R7 = 1200Ω

IC =5 [mA]

Se plantea una malla:

VR 6 = VBE + VR 7 = 0.7 + 6 = 6.7[V ]

Como las corrientes de colector son iguales en las tres etapas, las corrientes de

polarización también los serán:

VR 6

R6 = = 44 KΩ

Ip

VCC −V R 6

R5 = = 35 KΩ

Ip

Una vez calculados los componentes del circuito es necesario calcular la

impedancia de entrada, para recalcular la ganancia de la etapa 2, y la impedancia

de salida a fin de verificar lo solicitado.

Para el cálculo de la ganancia de tensión y de la impedancia de entrada, se realiza

el modelo del circuito:

AAO Electrónica I FACET-UNT

- Página 7-

Cálculo de la ganancia de tensión:

Vo (1 + h f e )ib R7

Av 3 = = ≅1

VS [

hie + (1 + h fe ) R7 ib ]

Cálculo de la impedancia de entrada:

Z i 3 = R5 // R6 //[hie 3 + (1 + h fe ) R7

Z i 3 = 13.4 KΩ

Cálculo de la impedancia de salida:

Para ello, se coloca un generador VO en la salida, de amplitud conocida y se

cortocircuita la entrada ya que en ese nodo había un generador de tensión.

Vo

Zo =

Io

io = ib + ie + ib h fe

Vo = ib .hie 3 = ie .R7

Reemplazando en io:

hie 3

io = (1 + h fe + )ib

R7

Reemplazando en Zo:

AAO Electrónica I FACET-UNT

- Página 8-

h

R7 ie

ib .h ie 1+ h

=

fe

Zo =

h hie

1 + h fe + ie ib R7 +

R7 1 + h fe

Calculando:

Z o = 9.7Ω

Por lo tanto se verifica lo solicitado en el enunciado

Cálculo de la ganancia total:

Con el valor de la impedancia de entrada de la tercera etapa se calcula la

ganancia de la etapa 2. Se recuerda que este es caso es idéntico al planteado para

el cálculo de la ganancia de la etapa 1.

R3 // Z i 3

AV 2 = −

R4

AV 2 = −11

Por lo tanto la ganancia total del pre-amplificador será:

AV = AV 1 . AV 2 . AV 3 = 108.9 = 40.74dB

Se observa que se cumple con el requisito de ganancia.

Cálculo de los capacitores de desacople

Para el capacitor de entrada el circuito que se ve es:

Cs y Zi1 configuran un filtro pasa alto, que la señal senoidal Vs debe pasar. La

característica aproximada de este filtro es:

AAO Electrónica I FACET-UNT

- Página 9-

Como se dijo, VS es una señal senoidal cuyas frecuencias están comprendidas

entre 20 Hz y 30 KHz. Debido a la respuesta del filtro las frecuencias altas no

tendrán problema en sobrepasarlo, pero las bajas sí. Por ende, se debe diseñar el

filtro para que la mínima frecuencia pase, o sea:

f mín ≥ f c

donde fmín=20 Hz

Como:

1

τ c= CS .Zi1 =

ωc

Entonces:

1

Cs ≥

2 π Z i1 f mín

Se adopta:

Cs = 10 µF

El capacitor de desacople, ubicado entre las etapas 1 y 2 será de idéntico valor al

ya calculado, por que Zi1= Zi2.

El capacitor de desacople ubicado entre las etapas 2 y 3 también será igual.

Con esto concluye el diseño del preamplificador. El circuito total queda:

AAO Electrónica I FACET-UNT

- Página 10-

2.2.- Excite el circuito con una señal senoidal Vs = 0.05 [V] y frecuencia de 1

KHz. Obtenga la curva AV vs f. Verifique el rango de frecuencia en el que el

amplificador puede operar.

Al realizar el barrido en frecuencia del pre-amplificador se obtienen los

siguientes gráficos:

En el gráfico de amplitud se observa que:

La ganancia es de 40 dB en la zona de planicie

Los puntos de media potencia (-3dB) están en aproximadamente en 5Hz y

2MHz, los que determinan el ancho de banda. Dentro de este rango no

existirá distorsión de frecuencia.

AAO Electrónica I FACET-UNT

- Página 11-

En el gráfico de fase, se observa que la fase es de 360º, en el intervalo de 40 Hz a

400 KHz.

Quienes determinan el ancho de banda son principalmente los capacitores de

desacople y el elemento activo.

Para analizar la influencia de los capacitores se cambiarán en el circuito por otros

de menor valor.

Si se cambia el capacitor de entrada por uno de valor 1µF, se obtiene:

En el gráfico de ganancia se observa que la frecuencia de corte inferior aumentó

a 30Hz, mientras que la de corte superior se mantiene en 2 MHz. En el gráfico de

fase se ve que la fase es de 360º desde los 300Hz hasta los 400 KHz

aproximadamente. En ambos gráficos la variación se dio en las frecuencias

inferiores.

Si se realiza una variación de este capacitor desde 0.1µF a 10µF, se obtiene:

AAO Electrónica I FACET-UNT

- Página 12-

Se nota en el gráfico de ganancia que cuanto menor es el capacitor de entrada

mayor es la frecuencia de corte inferior, mientras que la frecuencia de corte

superior no sufre modificaciones puesto que ésta es fijada por el elemento activo.

Si se cambia además los otros dos capacitores, de acople, por 1µF, y se mantiene

el de entrada en 10µF, se obtiene:

Se observa que el valor de estos, influye de la misma manera que el capacitor de

entrada, aumentando el valor de la frecuencia de corte superior y por lo tanto

disminuyendo el ancho de banda.

2.3.- Calcule y mida los valores de Zin y Zo.

Los cálculos de impedancia de entrada y de salida se realizaron en los puntos

anteriores. Los valores calculados fueron:

Zi = 5700Ω y Z o = 9.7Ω

Si se realiza un gráfico de la impedancia de entrada en función de la frecuencia,

se logra:

AAO Electrónica I FACET-UNT

- Página 13-

Loas valores obtenidos son próximos a los calculados.

Si se cambian los capacitores por otros de valor 1µF, la gráfica cambia de la

siguiente manera:

Donde se ve, que la impedancia cambió en el rango de las frecuencias bajas.

En cuanto a la impedancia de salida, el gráfico es:

Se observa que efectivamente esta es pequeña, del orden de los 9Ω, según lo

medido y en concordancia con lo calculado.

AAO Electrónica I FACET-UNT

- Página 14-

También podría gustarte

- Armónicas en Sistemas Eléctricos IndustrialesDe EverandArmónicas en Sistemas Eléctricos IndustrialesCalificación: 4.5 de 5 estrellas4.5/5 (12)

- Problemas resueltos de Hidráulica de CanalesDe EverandProblemas resueltos de Hidráulica de CanalesCalificación: 4.5 de 5 estrellas4.5/5 (7)

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiDe EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiCalificación: 5 de 5 estrellas5/5 (1)

- Cálculo de Amplificador de AudioDocumento11 páginasCálculo de Amplificador de Audiomariano zapata100% (1)

- Experiencias sobre circuitos eléctricos en serie operados por corriente directaDe EverandExperiencias sobre circuitos eléctricos en serie operados por corriente directaAún no hay calificaciones

- Sistemas de Soporte A DecisionesDocumento6 páginasSistemas de Soporte A DecisionesERamosAún no hay calificaciones

- LimitesDocumento11 páginasLimitesHectorAún no hay calificaciones

- 1.2.2amplificador en Emisor ComunDocumento12 páginas1.2.2amplificador en Emisor ComunOz MGAún no hay calificaciones

- Polarizacion BJT Problemas ResueltosDocumento15 páginasPolarizacion BJT Problemas ResueltosPaintball-Rodaj Park90% (21)

- Presentacion 777FDocumento140 páginasPresentacion 777FFrancisco MirandaAún no hay calificaciones

- Aplicaciones de Los Amplificadores OperacionalesDocumento126 páginasAplicaciones de Los Amplificadores OperacionalesJohn Fapper100% (1)

- Ejercicios de Integrales de Línea, Superficie y VolumenDe EverandEjercicios de Integrales de Línea, Superficie y VolumenCalificación: 4 de 5 estrellas4/5 (2)

- S3 - La Estructura Organizacional - Sesión 3 - Grupo 1Documento2 páginasS3 - La Estructura Organizacional - Sesión 3 - Grupo 1Daniela Saravia CondorAún no hay calificaciones

- Termodinamica Basica Libro Guia de Clase PDFDocumento310 páginasTermodinamica Basica Libro Guia de Clase PDFsergio zeballos100% (1)

- OTA Multiplicador AnalógicoDocumento12 páginasOTA Multiplicador AnalógicoFernando Pastor AsteckerAún no hay calificaciones

- Desarrollo de Examen Circuitos Analógicos 2Documento7 páginasDesarrollo de Examen Circuitos Analógicos 2Anonymous OqWlAx100% (1)

- Practica 2 Electronica IIDocumento5 páginasPractica 2 Electronica IIJennifer Cox100% (1)

- Practica 2 Electronica 2Documento11 páginasPractica 2 Electronica 2assembleruoAún no hay calificaciones

- Diseño Amplificador Con Rectas de Cargas DC y AC - Calculos en MathcadDocumento7 páginasDiseño Amplificador Con Rectas de Cargas DC y AC - Calculos en MathcadJairo Vargas CaleñoAún no hay calificaciones

- Ejercicios de amplificadores con transistores BJT y MOSFETDocumento10 páginasEjercicios de amplificadores con transistores BJT y MOSFETPablo V SalazarAún no hay calificaciones

- Ejercicios Con BJT Elizabeth Arevalo-2020Documento29 páginasEjercicios Con BJT Elizabeth Arevalo-2020JohnAún no hay calificaciones

- Prob 15 1Documento4 páginasProb 15 1Chentito Magana SanchezAún no hay calificaciones

- Inf 3 Lab AnalogDocumento11 páginasInf 3 Lab AnalogMicky PsmAún no hay calificaciones

- Practica 5Documento6 páginasPractica 5Mariangel BaezAún no hay calificaciones

- 7 Problemas de AmplificaciónDocumento10 páginas7 Problemas de AmplificaciónEdwin BardalesAún no hay calificaciones

- Antologia Practica 7 Amplificador en EcDocumento27 páginasAntologia Practica 7 Amplificador en EcAngie JiménezAún no hay calificaciones

- Aplicación de Lo AprendidoDocumento3 páginasAplicación de Lo Aprendidopedroantoni22100% (1)

- Tarea 2 - Fabian Escobar - 99Documento4 páginasTarea 2 - Fabian Escobar - 99Alexis EscobarAún no hay calificaciones

- Circuito BJT NPN con polarización de emisor común - Solución Práctica 2Documento4 páginasCircuito BJT NPN con polarización de emisor común - Solución Práctica 2Yacson Ruiz SanchezAún no hay calificaciones

- Amplificador BJTDocumento11 páginasAmplificador BJTGerman Redondo MendozaAún no hay calificaciones

- TPN1 Introd a los Amp y Caract Reales de los AmpOpDocumento9 páginasTPN1 Introd a los Amp y Caract Reales de los AmpOpjulioAún no hay calificaciones

- G8 - TEV2 - Bruno y CzemkoDocumento23 páginasG8 - TEV2 - Bruno y CzemkoFederico BrunoAún no hay calificaciones

- 4 PD 09 Opamp 1Documento3 páginas4 PD 09 Opamp 1nessus joshua aragonés salazarAún no hay calificaciones

- 2PC 2017 10 Cirana2 SoluccDocumento6 páginas2PC 2017 10 Cirana2 SoluccCholaza ProduccionesAún no hay calificaciones

- Nuevo Documento de Microsoft WordDocumento13 páginasNuevo Documento de Microsoft WordJesus Gallardo RamirezAún no hay calificaciones

- Pre Informe N2Documento9 páginasPre Informe N2Walter QuispeAún no hay calificaciones

- Pre Informe N2Documento9 páginasPre Informe N2Walter QuispeAún no hay calificaciones

- Amplificadores operacionales: Configuraciones básicas y análisis de parámetrosDocumento22 páginasAmplificadores operacionales: Configuraciones básicas y análisis de parámetrosBeda Lisa SaezAún no hay calificaciones

- Electronica I Prueba 1-2Documento52 páginasElectronica I Prueba 1-2EIEE100% (2)

- Solución de Taller BJT en ACDocumento19 páginasSolución de Taller BJT en ACAlexander VidalAún no hay calificaciones

- TP OsciladoresDocumento10 páginasTP OsciladoresLmGamAún no hay calificaciones

- Análisis de amplificadores en cascada con transistores NPNDocumento14 páginasAnálisis de amplificadores en cascada con transistores NPNAlvaro HuanccoAún no hay calificaciones

- 1.2.4 Amplificador en Base Común PDFDocumento12 páginas1.2.4 Amplificador en Base Común PDFangelAún no hay calificaciones

- Amplificador en Emisor ComunDocumento9 páginasAmplificador en Emisor ComunAnder Ramos InfantesAún no hay calificaciones

- Diseño de un amplificador multietapa con etapa de potenciaDocumento21 páginasDiseño de un amplificador multietapa con etapa de potenciajosdeda13Aún no hay calificaciones

- Laboratorio 1 CascadaDocumento25 páginasLaboratorio 1 CascadaJOAQUIN ALESSANDRO CABRERA CHAMORROAún no hay calificaciones

- Ejercicio MultietapaDocumento4 páginasEjercicio MultietapaGonzalo BerardoAún no hay calificaciones

- Informe Practica 3 Se Gerardo RodriguesDocumento16 páginasInforme Practica 3 Se Gerardo RodriguesGerardo Rodrigues FlammiaAún no hay calificaciones

- Informe Previo 01 C. Electronicos 2Documento11 páginasInforme Previo 01 C. Electronicos 2Ruben Sandro100% (3)

- Amplificador Emisor Común BJTDocumento15 páginasAmplificador Emisor Común BJTDaniela Marañón RodriguezAún no hay calificaciones

- Configuracion Cascada P1Documento5 páginasConfiguracion Cascada P1Daniel SalazarAún no hay calificaciones

- Informe Amplificador Diferenciador e IntegradorDocumento14 páginasInforme Amplificador Diferenciador e IntegradorNico PerezAún no hay calificaciones

- Guia 1 Esc. Mecatronica.Documento6 páginasGuia 1 Esc. Mecatronica.JoseCruzSeguraAún no hay calificaciones

- Amplificador operacional: introducción, características y tipos de realimentaciónDocumento109 páginasAmplificador operacional: introducción, características y tipos de realimentaciónALEXISAún no hay calificaciones

- Aplicaciones No Lineales Del Amplificador OperacionalDocumento9 páginasAplicaciones No Lineales Del Amplificador OperacionalIsabel50% (2)

- Limitaciones de Amplificadores OperacionalesDocumento10 páginasLimitaciones de Amplificadores OperacionalesChristian BohórquezAún no hay calificaciones

- Problemas 5 EBopampDocumento10 páginasProblemas 5 EBopampFreddy Hernandez BecerraAún no hay calificaciones

- Diseño de Amplificador MultietapaDocumento7 páginasDiseño de Amplificador MultietapaJose Fernando Fuentes RoaAún no hay calificaciones

- Mediciones Sobre El Amplificador Operacional (OPAM)Documento52 páginasMediciones Sobre El Amplificador Operacional (OPAM)Gabriel LozadaAún no hay calificaciones

- Construccion Del Amplificador OperacionalDocumento14 páginasConstruccion Del Amplificador OperacionalJuan JofreAún no hay calificaciones

- Taller 2Documento1 páginaTaller 2Maria GonzalesAún no hay calificaciones

- SISTEMAS ANALOGOS No LinealesDocumento37 páginasSISTEMAS ANALOGOS No LinealesMaria GonzalesAún no hay calificaciones

- Informe ControlDocumento7 páginasInforme ControlMaria GonzalesAún no hay calificaciones

- Proyecto Respuesta en FrecuenciaDocumento14 páginasProyecto Respuesta en FrecuenciaMaria GonzalesAún no hay calificaciones

- Cristalizacion y SublimacionDocumento4 páginasCristalizacion y SublimacionanaAún no hay calificaciones

- EquidadDocumento1 páginaEquidadDc GladysAún no hay calificaciones

- EyM3 4 PDFDocumento12 páginasEyM3 4 PDFAnonymous 2V0WjoHuLAún no hay calificaciones

- Gases IdealesDocumento13 páginasGases IdealesAnonymous R7TD0zNAún no hay calificaciones

- APUNTES Estudio de ImanesDocumento3 páginasAPUNTES Estudio de ImanesMaria GonzalesAún no hay calificaciones

- Modelo de Negocio PuntonetDocumento2 páginasModelo de Negocio PuntonetJhony Xavier MendozaAún no hay calificaciones

- Sesión 6Documento17 páginasSesión 6Edgar Mauricio Lopez RojasAún no hay calificaciones

- Pract 2 WSDocumento11 páginasPract 2 WSCarlos Alberto Vidales SotoAún no hay calificaciones

- Taller Sobre Comercializadora Pyd S.A.SDocumento27 páginasTaller Sobre Comercializadora Pyd S.A.SStefani GonzalezAún no hay calificaciones

- Anexo - 1 - Proveedor - D - Link PDFDocumento36 páginasAnexo - 1 - Proveedor - D - Link PDFjorgequatroAún no hay calificaciones

- 23.00 Valvula de control-VC - 02Documento1 página23.00 Valvula de control-VC - 02Dilver Joel Cieza QuirozAún no hay calificaciones

- Expediente Chanquil-Tincona-ImpresoDocumento148 páginasExpediente Chanquil-Tincona-ImpresoRocio Santiago AlaniaAún no hay calificaciones

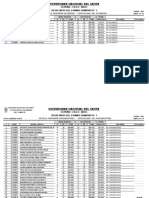

- RESULTADOS POR ESPECIALIDAD EXAMEN SuMATIVO 01 - CEPUNS 2023-IDocumento40 páginasRESULTADOS POR ESPECIALIDAD EXAMEN SuMATIVO 01 - CEPUNS 2023-IValentinovich ValeraAún no hay calificaciones

- Brochure1 PDFDocumento17 páginasBrochure1 PDFsimon nuñezAún no hay calificaciones

- Determinación de la polaridad de un transformador mediante tres métodosDocumento3 páginasDeterminación de la polaridad de un transformador mediante tres métodosEuiler Diego Diaz LuqueAún no hay calificaciones

- Análisis de los procesos de negocios de un sistema empresarial químicoDocumento8 páginasAnálisis de los procesos de negocios de un sistema empresarial químicoyonsonAún no hay calificaciones

- Importar Inventor A AnsysDocumento4 páginasImportar Inventor A AnsysJoseAún no hay calificaciones

- Contorno, Dintorno EntornoDocumento22 páginasContorno, Dintorno EntornoAnita Parra ClaveríaAún no hay calificaciones

- LOGISTICA - PROYECTO DE AULA - Tanque de AlmacenamientoDocumento14 páginasLOGISTICA - PROYECTO DE AULA - Tanque de AlmacenamientoSergio Andres MedellinAún no hay calificaciones

- Manual de Mantenimiento de Mescladora de Arena para Uso Industrial GNDocumento12 páginasManual de Mantenimiento de Mescladora de Arena para Uso Industrial GNJonathan Alejandro Rivera AltamiranoAún no hay calificaciones

- Conector Metalico Barra T/Marco Pro6004Documento10 páginasConector Metalico Barra T/Marco Pro6004camilo sepulveda novoaAún no hay calificaciones

- Curso Symfony 2Documento262 páginasCurso Symfony 2Marina LeonAún no hay calificaciones

- Matriz Foda Grupo Gloria 1 PDFDocumento2 páginasMatriz Foda Grupo Gloria 1 PDFBarreto Noa Dany DarioAún no hay calificaciones

- Uso Del MicrocomputadorDocumento5 páginasUso Del MicrocomputadorDANELISAún no hay calificaciones

- GeneradorCD_DerivacionDocumento9 páginasGeneradorCD_DerivacionGeraAún no hay calificaciones

- ADMINISTRACIONDocumento4 páginasADMINISTRACIONjclopezsAún no hay calificaciones

- Ficha - Tecnica Mazda mx-5Documento2 páginasFicha - Tecnica Mazda mx-5Karla GonzalezAún no hay calificaciones

- Cuestionario - Ruta de La CalidadDocumento3 páginasCuestionario - Ruta de La CalidadImpulso CrackAún no hay calificaciones

- Tarea para SOM03Documento4 páginasTarea para SOM03Alejandro RamosAún no hay calificaciones

- Comparación de MicrófonosDocumento1 páginaComparación de MicrófonosDubán Sánchez GonzálezAún no hay calificaciones

- Monografia Teconly Smarthome TerminadoDocumento17 páginasMonografia Teconly Smarthome TerminadoMaria Huancapaza mamaniAún no hay calificaciones

- Solucionario - Guia de Practica 07Documento8 páginasSolucionario - Guia de Practica 07PEDRO LUIS BOZA SULLCAAún no hay calificaciones