Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Tarea4 AndreaVaquiro

Cargado por

gabriel tejadaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Tarea4 AndreaVaquiro

Cargado por

gabriel tejadaCopyright:

Formatos disponibles

Tarea 4: Diseño de circuitos combinacionales y secuenciales.

Presentado por: Andrea Maritza Váquiro Diaz.

Grupo: 243004_10

Código: 1.030.552.597.

Presentado a: Sandra Milena García

Universidad Nacional Abierta y a Distancia UNAD.

Bogotá D.C.

Abril del 2020.

INTRODUCCIÓN

En este trabajo a través del Diseño de circuitos combinaciones y secuenciales, se

crea un cronometro de cuenta regresiva en donde la edad del estudiante es el

valor inicial del conteo, se muestra el diagrama de bloques del circuito a

implementar y se realiza la Simulación de circuitos combinacionales y

secuenciales, mediante el desarrollo del ejercicio práctico con el software Eda

PLayGround evidenciando la descripción en VHDL, y finalmente la ejecución

mostrando el resultado como soporte de la apropiación de los conceptos teóricos a

que tiene lugar este tema.

OBJETIVOS

El estudiante entiende, interioriza y desarrolla ejercicios prácticos del diseño de un

cronometro de cuenta egresiva, basado en el diagrama de bloques ilustrado.

Resolver ejercicios con aplicaciones de circuitos digitales combinacionales y

secuenciales, ampliando los conocimientos teóricos y practica en el uso del

software Eda Playground por medio de ejercicios prácticos.

Actividades a desarrollar

Diseñar un cronómetro de cuenta regresiva. El valor inicial del contero será la

edad del estudiante. Por ejemplo, si el estudiante tiene 32 años, el cronómetro

deberá contar desde de 32 hasta 0 (32,31, 30, … 2,1,0).

Se debe tener en cuenta que el reset (R*) del Registro_conteo debe reiniciar el

conteo a su valor inicial, es decir, la edad del estudiante. Los otros reset deben

poner la salida a cero.

El funcionamiento del cronómetro es el siguiente:

El cronómetro tendrá un pulsador inicio que permitirá iniciar y detener el

conteo.

El cronómetro también tendrá un pulsador reinicio que llevará el

cronómetro a su conteo inicial, es decir, la edad del estudiante y detener el

conteo.

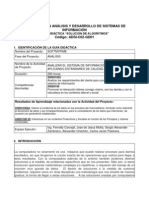

La figura 1, muestra el diagrama de bloques del circuito a implementar

Edad del estudiante 31 años.

Figura 1: Cicuito a implementar

Se debe hacer la implementación en VHDL del circuito propuesto.

Estudiante con 31 años de edad “011111”

Adicionalmente se debe simular para comprobar que efectivamente el

circuito funciona como se ha descrito.

CONCLUSIONES

La interacción con los temas y ejercicios prácticos que en esta guía se desarrolló,

enriquecen y aumentan nuestros conocimientos en lo concerniente al diseño de un

contador de cuenta regresiva mediante la ilustración de un diagrama de bloque,

que organizadamente conllevan a la consecución de la tarea propuesta.

La implementación del diseño en la herramienta de software EDA Playground,

fortalece los conocimientos adquiridos una vez se llevó a la practica la ejecución

del VHDL arrojando satisfactoriamente el resultado que el ejercicio solicitaba.

BIBLIOGRAFÍA

Muñoz, J. (2012). Introducción a los Sistemas Digitales: Un enfoque usando

Lenguajes de Descripción de Hardware. (Capítulos 7, 9 y 10, pp. 135-149,177-

208). Madrid. Recuperado de https://openlibra.com/es/book/introduccion-a-los-

sistemas-digitales

Flórez, F. H. A. (2010). Diseño lógico: fundamentos de electrónica digital.

(Capítulos 5,6 pp. 109-145). Recuperado de http://

bibliotecavirtual.unad.edu.co:2460/lib/unadsp/detail.action?docID=3199073

Fajardo, C. (2016, diciembre 17), Divisores de Frecuencia. [Archivo de video].

Recuperado de http://hdl.handle.net/10596/9855

Chu, P.P. (2006). RTL Hardware Design Using VHDL: Coding for Efficiency,

Portability, and Scalability. Hoboken, N.J.: Wiley-IEEE Press. Recuperado

de: http://bibliotecavirtual.unad.edu.co:2051/login.aspx?

direct=true&db=e000xww&AN=158127&lang=es&site=ehost-live

También podría gustarte

- Manual de implementación de herramientas digitales para el desarrollo sostenibleDe EverandManual de implementación de herramientas digitales para el desarrollo sostenibleCalificación: 5 de 5 estrellas5/5 (1)

- Electrónica análoga: Diseño de circuitosDe EverandElectrónica análoga: Diseño de circuitosCalificación: 4.5 de 5 estrellas4.5/5 (15)

- Tarea 4 - Grupo56Documento16 páginasTarea 4 - Grupo56Jairo HurtatisAún no hay calificaciones

- Tarea 4 - Grupo - 41Documento25 páginasTarea 4 - Grupo - 41pedroAún no hay calificaciones

- Robinson Salas Tarea 5Documento9 páginasRobinson Salas Tarea 5Robinson Salas DiazAún no hay calificaciones

- Tarea 4 Jorge RuizDocumento7 páginasTarea 4 Jorge RuizMiGue DAzaAún no hay calificaciones

- Tarea 4 Jorge RuizDocumento7 páginasTarea 4 Jorge RuizGINA ISABEL ARANGUREN ARAQUEAún no hay calificaciones

- Unidad 4 - Tarea 4 - Geovanny Culma 3Documento5 páginasUnidad 4 - Tarea 4 - Geovanny Culma 3GeovannyAún no hay calificaciones

- Tarea 5Documento12 páginasTarea 5Jose M Caballero67% (3)

- Tarea 4 Felipe SanchezDocumento9 páginasTarea 4 Felipe Sanchezfelipe sanchezAún no hay calificaciones

- Tarea 4 - Sadak CharryDocumento6 páginasTarea 4 - Sadak CharryAndresAmayaAún no hay calificaciones

- Manuel Alejandro Rincon SanchezDocumento5 páginasManuel Alejandro Rincon SanchezAndres PerezAún no hay calificaciones

- ELECTRONICA DIGITAL Tarea 4 DanielDocumento5 páginasELECTRONICA DIGITAL Tarea 4 DanielAndres PerezAún no hay calificaciones

- Aporte - Tarea 4Documento4 páginasAporte - Tarea 4Richard Mejia AcevedoAún no hay calificaciones

- SAYAYINDocumento7 páginasSAYAYINAndrea PulgarinAún no hay calificaciones

- Tarea 4 G 17Documento7 páginasTarea 4 G 17javier martinezAún no hay calificaciones

- Equipob B01Documento11 páginasEquipob B01Fisio VitalAún no hay calificaciones

- Guía de Actividades y Rúbrica de Evaluación - Tarea 1 - Sistemas de Numeración y Simplificación de Funciones LógicasDocumento12 páginasGuía de Actividades y Rúbrica de Evaluación - Tarea 1 - Sistemas de Numeración y Simplificación de Funciones LógicasJavier MendezAún no hay calificaciones

- Tarea 6 - Grupo8 - Jhonattan Toro.Documento12 páginasTarea 6 - Grupo8 - Jhonattan Toro.Woflgang GangflowAún no hay calificaciones

- Tarea 4 Carlos PatiñoDocumento7 páginasTarea 4 Carlos PatiñoClaudio Santiago Condor DiestraAún no hay calificaciones

- Unidad 4 - Tarea 4 - Geovanny Culma 2Documento3 páginasUnidad 4 - Tarea 4 - Geovanny Culma 2GeovannyAún no hay calificaciones

- Actividad 2 Cuadrados Con Triángulos 6toDocumento6 páginasActividad 2 Cuadrados Con Triángulos 6tosecretariaterapias1Aún no hay calificaciones

- UntitledDocumento30 páginasUntitledSandra BertolinoAún no hay calificaciones

- Taller Aplicando Funciones y Procedimientos Solucion AlgoritmosDocumento9 páginasTaller Aplicando Funciones y Procedimientos Solucion AlgoritmosEdwin Alexander Ospina PennaAún no hay calificaciones

- JAGF - Unidad Didáctica Programación en PythonDocumento40 páginasJAGF - Unidad Didáctica Programación en PythonJ. Adán GonzalezAún no hay calificaciones

- Electronica DigitalDocumento9 páginasElectronica DigitalRoloAún no hay calificaciones

- Valtierra Zamorano Enrique TEMA.3 - ACTIVIDAD.B SimulaciónDocumento9 páginasValtierra Zamorano Enrique TEMA.3 - ACTIVIDAD.B SimulaciónEmma OrozcoAún no hay calificaciones

- INFORMATICADocumento5 páginasINFORMATICAwilson100% (1)

- Proyecto 1 Grupo 2Documento13 páginasProyecto 1 Grupo 2Trejo BernardoAún no hay calificaciones

- LalalaDocumento84 páginasLalalaDreyko Perez GarzaAún no hay calificaciones

- José Ferney Cortés GarnicaDocumento12 páginasJosé Ferney Cortés Garnicazumy brainovskiAún no hay calificaciones

- Desarrollo Electronica Digital Fase 3 Sergio Murcia CompletoDocumento22 páginasDesarrollo Electronica Digital Fase 3 Sergio Murcia CompletoServi Tec Net50% (2)

- Tarea 3 - Fundamentos de Electrónica Digital - CristyMielesDocumento4 páginasTarea 3 - Fundamentos de Electrónica Digital - CristyMielesPaula MielesAún no hay calificaciones

- Adsi-c02-Gd01 Guia Solucion de AlgoritmosDocumento9 páginasAdsi-c02-Gd01 Guia Solucion de AlgoritmosMiguel AndradeAún no hay calificaciones

- Guia para El Desarrollo Del Componente PrácticoDocumento7 páginasGuia para El Desarrollo Del Componente PrácticoELIANA SANCHEZAún no hay calificaciones

- Electronica DigitalDocumento19 páginasElectronica DigitalComark Ponguta100% (1)

- Guia para El Estudiante DLP 2015 PDFDocumento13 páginasGuia para El Estudiante DLP 2015 PDFMiguelMartinezAún no hay calificaciones

- Tarea-2 Carlos VelasquezDocumento10 páginasTarea-2 Carlos Velasquezcarlos mario velasquez guisadoAún no hay calificaciones

- Planificación de InformáticaDocumento10 páginasPlanificación de Informáticajuands16440% (1)

- Ttarea6 Grupo24Documento13 páginasTtarea6 Grupo24Carlos Eduardo Rengifo AvilaAún no hay calificaciones

- Corporación Unificada Nacional de Educación Superior CUN: Bogotá D.C 2024Documento23 páginasCorporación Unificada Nacional de Educación Superior CUN: Bogotá D.C 2024juanpablolombo283Aún no hay calificaciones

- UntitledDocumento13 páginasUntitledRafael Jurado LagosAún no hay calificaciones

- JasonDocumento4 páginasJasonLirisha Anima ignisAún no hay calificaciones

- BASE Proyecto Física 1Documento3 páginasBASE Proyecto Física 1Enrique Talavera ChávezAún no hay calificaciones

- Guía de Actividades y Rúbrica de Evaluación - Tarea 1 - Sistemas de Numeración y Simplificación de Funciones LógicasDocumento11 páginasGuía de Actividades y Rúbrica de Evaluación - Tarea 1 - Sistemas de Numeración y Simplificación de Funciones LógicasAnonymous f54GFvsPgRAún no hay calificaciones

- Reporte de PracticaDocumento19 páginasReporte de PracticaDulce Gonzalez VeraAún no hay calificaciones

- 51Documento7 páginas51Eduardo Prado GalindoAún no hay calificaciones

- Tarea 3 - Jose BernalDocumento8 páginasTarea 3 - Jose BernalJackson GiraldoAún no hay calificaciones

- Tarea - 5 - Grupo - 243004 - 30Documento8 páginasTarea - 5 - Grupo - 243004 - 30قخرتشقي دثنخشAún no hay calificaciones

- Proyecto 3 Robotica Ev3 Core 1 29 PDFDocumento29 páginasProyecto 3 Robotica Ev3 Core 1 29 PDFVictor Rafael JSAún no hay calificaciones

- Torres Gonzalez Paloma Florisel - Practica 7Documento5 páginasTorres Gonzalez Paloma Florisel - Practica 7Paloma TorresAún no hay calificaciones

- Guía de Actividades y Rúbrica de Evaluación - Fase 2Documento5 páginasGuía de Actividades y Rúbrica de Evaluación - Fase 2davidAún no hay calificaciones

- Asignaciones 1er Corte 2-2023 Calculo Numerico Temas Unidad 1Documento5 páginasAsignaciones 1er Corte 2-2023 Calculo Numerico Temas Unidad 1Cesar Enexis RodriguezAún no hay calificaciones

- TA1 CI61 Barriga Sanches Robles Grupo6Documento7 páginasTA1 CI61 Barriga Sanches Robles Grupo6cristian barrigaAún no hay calificaciones

- Guía para El Desarrollo Del Componente Práctico - Unidad 3 - Paso 5 - Componente Práctico e Implementación Del Proyecto - Práctica de LaboratorioDocumento27 páginasGuía para El Desarrollo Del Componente Práctico - Unidad 3 - Paso 5 - Componente Práctico e Implementación Del Proyecto - Práctica de LaboratorioJulieth MurciaAún no hay calificaciones

- Guía de Actividades y Rúbrica de Evaluación - Tarea 5 - Aplicaciones Con Circuitos CombiDocumento9 páginasGuía de Actividades y Rúbrica de Evaluación - Tarea 5 - Aplicaciones Con Circuitos Combijuan diegoAún no hay calificaciones

- Tarea 1 Eduar Fuentes Torrenegra 1049924811Documento11 páginasTarea 1 Eduar Fuentes Torrenegra 1049924811Karen MoralesAún no hay calificaciones

- Portafolio Programacion I 2012Documento351 páginasPortafolio Programacion I 2012mariuxipaolazeaAún no hay calificaciones

- Proyecto de SoftwareDocumento14 páginasProyecto de SoftwareRicardo Aca0% (1)

- Actividad 0Documento9 páginasActividad 0Diego MontoyaAún no hay calificaciones

- Guía de Actividades y Rúbrica de Evaluación - Tarea 4 - Análisis de Aplicaciones Con Ctos Combinacionales y SecuencialesDocumento9 páginasGuía de Actividades y Rúbrica de Evaluación - Tarea 4 - Análisis de Aplicaciones Con Ctos Combinacionales y SecuencialesMARCOAún no hay calificaciones

- Desarollo ActividadDocumento3 páginasDesarollo Actividadgabriel tejadaAún no hay calificaciones

- Electronica DigitalDocumento9 páginasElectronica Digitalgabriel tejadaAún no hay calificaciones

- 13 - Diego - Caviedes - Tarea 4 (1 y 2)Documento10 páginas13 - Diego - Caviedes - Tarea 4 (1 y 2)jorge eduardo aza sanchezAún no hay calificaciones

- Ejercicio Estudiante 1Documento4 páginasEjercicio Estudiante 1gabriel tejadaAún no hay calificaciones

- Fase 4 - Daniel Antonio NuñezDocumento8 páginasFase 4 - Daniel Antonio Nuñezgabriel tejadaAún no hay calificaciones

- Plantilla Sustentación - TdODocumento11 páginasPlantilla Sustentación - TdOgabriel tejadaAún no hay calificaciones

- Fase 4 - Daniel Antonio NuñezDocumento8 páginasFase 4 - Daniel Antonio Nuñezgabriel tejadaAún no hay calificaciones

- Guía de Actividades y Rúbrica de Evaluación - Fase 4 - Presentar Solución Al Problema de Luces Audio Rítmicas de 3 CanalesDocumento13 páginasGuía de Actividades y Rúbrica de Evaluación - Fase 4 - Presentar Solución Al Problema de Luces Audio Rítmicas de 3 CanalesManuel MaciasAún no hay calificaciones

- Fase 6 - Daniel Antonio NuñesDocumento7 páginasFase 6 - Daniel Antonio Nuñesgabriel tejadaAún no hay calificaciones

- Informe Final Practicas de Laboratorio Electrónica AnálogaDocumento10 páginasInforme Final Practicas de Laboratorio Electrónica Análogajorge eduardo aza sanchezAún no hay calificaciones

- Guía de Actividades y Rúbrica de Evaluación - Paso 5 - Presentación de ResultadosDocumento17 páginasGuía de Actividades y Rúbrica de Evaluación - Paso 5 - Presentación de Resultadoskaren andrea callesuarezAún no hay calificaciones

- Electronica DigitalDocumento9 páginasElectronica Digitalgabriel tejadaAún no hay calificaciones

- EnsayoDocumento4 páginasEnsayogabriel tejadaAún no hay calificaciones

- Guía de Electronica DigitalDocumento11 páginasGuía de Electronica Digitalgabriel tejadaAún no hay calificaciones

- Manual de Instrucciones de EOS Utility Ver.3.12 para Macintosh (Spanish Edition)Documento117 páginasManual de Instrucciones de EOS Utility Ver.3.12 para Macintosh (Spanish Edition)alexisfpcAún no hay calificaciones

- Evidencia 3Documento2 páginasEvidencia 3Javi GarciaAún no hay calificaciones

- Aplicacions Motion Na IndustriaDocumento54 páginasAplicacions Motion Na IndustriaYOHAN ALEXANDER SALAMANCA ARBOLEDAAún no hay calificaciones

- Y550-L03 V100R001ARGC25B249 - SLA - Claro - SW - Upgrade - Guide - +Ý+ + +ÂÍ©Á+-Ú.en - EsDocumento9 páginasY550-L03 V100R001ARGC25B249 - SLA - Claro - SW - Upgrade - Guide - +Ý+ + +ÂÍ©Á+-Ú.en - EsAbraham Gomez CordovaAún no hay calificaciones

- 1 2 Estructura Basica Del ComputadorDocumento12 páginas1 2 Estructura Basica Del ComputadorRosy GuerraAún no hay calificaciones

- InformeDocumento5 páginasInformebryan lozanoAún no hay calificaciones

- 1 Introducción A Medios Tecnológicos para CursoDocumento29 páginas1 Introducción A Medios Tecnológicos para Cursoleocab123100% (5)

- Laboratorio 9Documento6 páginasLaboratorio 9Ana LuisaAún no hay calificaciones

- Definicion de Automatas ProgramablesDocumento8 páginasDefinicion de Automatas ProgramablesScott MelgarejoAún no hay calificaciones

- PresentaciónDocumento22 páginasPresentaciónJosé Antoni LedezmaAún no hay calificaciones

- DefinicionesDocumento9 páginasDefinicionesSantiagoFigueroaAún no hay calificaciones

- Red de IptvDocumento188 páginasRed de IptvHenry CapachoAún no hay calificaciones

- Air FiberDocumento74 páginasAir Fiberluis rodriguezAún no hay calificaciones

- Silabo Programacion EstructuradaDocumento7 páginasSilabo Programacion EstructuradaGABRIEL UNACINO DLSTAún no hay calificaciones

- Diagramas de Flujo y Pseudocódigos 1Documento12 páginasDiagramas de Flujo y Pseudocódigos 1SMITH HERRERA JIMENEZAún no hay calificaciones

- Convertidor B-H P4Documento17 páginasConvertidor B-H P4Jorge Alberto Ortiz GalloAún no hay calificaciones

- Práctica Calificada 2-2Documento7 páginasPráctica Calificada 2-2Blas coillo mamaniAún no hay calificaciones

- Práctica 1. Intro Al Lab de AutomatizaciónDocumento15 páginasPráctica 1. Intro Al Lab de AutomatizaciónAraceli OrtizAún no hay calificaciones

- PROBLEMASDocumento4 páginasPROBLEMASeddy pomaAún no hay calificaciones

- Reporte NMAPDocumento12 páginasReporte NMAPRicardo de la ParraAún no hay calificaciones

- SKF QuickCollect SensorDocumento5 páginasSKF QuickCollect SensorFreddy ZabalaAún no hay calificaciones

- Examen Del Capítulo 2Documento2 páginasExamen Del Capítulo 2Adrian Alejandro LLanos ZentenoAún no hay calificaciones

- 1.3 FiltrosDocumento4 páginas1.3 FiltrosJosueAún no hay calificaciones

- 16.3.1 Packet Tracer - Troubleshoot Static and Default Routes - ILMDocumento3 páginas16.3.1 Packet Tracer - Troubleshoot Static and Default Routes - ILMmarcelo tanimucaAún no hay calificaciones

- Procedimiento de Limpieza de Oficinas - JORGE SORIADocumento6 páginasProcedimiento de Limpieza de Oficinas - JORGE SORIAJorge Luis SoriaAún no hay calificaciones

- Catálogo Kaadas 2023 DTDocumento14 páginasCatálogo Kaadas 2023 DTCarmen Rivero MoralesAún no hay calificaciones

- Tu To Oracle FormDocumento60 páginasTu To Oracle FormAlvaro CalderonAún no hay calificaciones

- Introducción A La TecnologíaDocumento34 páginasIntroducción A La Tecnologíaplanilla Tribe COAún no hay calificaciones

- Arranque Desde RedDocumento11 páginasArranque Desde RedMiguel Angel PalaciosAún no hay calificaciones

- Ventajas y Desventajas de Windows 7Documento6 páginasVentajas y Desventajas de Windows 7Andres ArroyoAún no hay calificaciones