Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Practica2 Diseño

Cargado por

Cesar Lopez ReyesTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Practica2 Diseño

Cargado por

Cesar Lopez ReyesCopyright:

Formatos disponibles

Benemérita Universidad Autónoma De Puebla

Diseño Lógico y Digital

Otoño 2018

Practica #2

“Diseño del juego piedra, papel, tijera”

J. Eduardo Gonzalez B., Joyce Aguilar M., Ricardo Romero S., Roberto Castillo M.,

Facultad de Ciencias de la Computación.

Ciudad Universitaria, Edif. CCO5-201, Col. San Manuel, C.P. 72570, Puebla, Pue., México.

jose.eduardo.gonzalez.barbosa@gmail.com

joyce.amarquez@live.com

Fecha: 28/08/2018

Resumen – Para esta practica se planteo el empate deberá de mostrarse por medio de un 11

siguiente problema;* en la salida.

En el caso de que no se oprima J (J=0) las

Diseñe un sistema electrónico digital capaz de salidas SA y SB serán igual a cero.

mostrar al ganador entre dos adversarios

del tradicional concurso piedra, papel o tijera. Introducción

El sistema estará definido por las entradas de

los jugadores A (A1, A2) y B (B1, B2) y dos Este documento habla sobre la resolución de un

salidas Sa y Sb, Se recomienda usar el siguiente problema, el diseño de un sistema

código para identificar cada propuesta: combinacional, con su respectivo modelo

optimizado y su posterior emulación utilizando

codigo Propuesta código VHDL

0 0 No hay El problema plantea que se necesitan de al

propuesta

menos cuatro votos, para decidir que elección

0 1 piedra se tomara, sin embargo, si ningún regidor vota

a favor, no se tomara la decisión como válida

1 0 Papel

aunque cuente con la cantidad de votos

1 1 Tijera necesarios.

Con lo cual se propone la siguiente tabla de

Se requiere de un botón adicional llamado J verdad:

(juego) de modo que solo al oprimirlo muestre

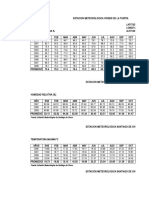

J A1 A2 B1 B2 Sa Sb

por medio de dos salidas SA y SB indique que

jugador gano, en el caso de que uno o los dos

1 0 0 0 0 0 0

concursantes no tengan propuesta el resultado

será nulo indicando la salidas 00, en caso de 1 0 0 0 1 0 1

1 0 0 1 0 0 1 A┐B m16 m17 m19 m18

1 0 0 1 1 0 1

1 0 1 0 0 1 0

S0 ┐C┐D ┐CD C C

D ┐D

1 0 1 0 1 1 1

┐A┐B 0 1 0 1

1 0 1 1 0 0 1

1 0 1 1 1 1 0 ┐AB 0 1 0 1

1 1 0 0 0 1 0 AB 0 1 0 1

1 1 0 0 1 1 0 A┐B 0 1 0 1

1 1 0 1 0 1 1

1 1 0 1 1 0 1

S1 ┐C┐D ┐CD C C

D ┐D

1 1 1 0 0 1 0

┐A┐B 0 0 0 1

1 1 1 0 1 0 1

┐AB 1 1 1 0

1 1 1 1 0 1 0

1 1 1 1 1 1 1 AB 1 1 1 0

A┐B 0 0 0 1

S2 ┐C┐D ┐CD C C

𝐹 = ┐𝐴𝑆┐𝑅1𝑅2𝑅3 + ┐𝐴𝑆𝑅1𝑅2┐𝑅3 D ┐D

+ ┐𝐴𝑆𝑅1┐𝑅2𝑅3

┐A┐B 0 0 1 0

+ ┐𝐴𝑆𝑅1𝑅2𝑅3 + 𝐴𝑆𝑅1𝑅2𝑅3

+ 𝐴𝑆𝑅1𝑅2┐𝑅3 + 𝐴𝑆𝑅1┐𝑅2𝑅3 ┐AB 0 0 1 1

+ 𝐴𝑆𝑅1┐𝑅2┐𝑅3 AB 1 1 0 0

+ 𝐴𝑆┐𝑅1𝑅2𝑅3

A┐B 1 1 0 1

+ 𝐴𝑆┐𝑅1┐𝑅2𝑅3

+ 𝐴𝑆┐𝑅1┐𝑅2𝑅3

+ 𝐴┐𝑆𝑅1𝑅2𝑅3

S3 ┐C┐D ┐CD C C

+ 𝐴┐𝑆𝑅1𝑅2┐𝑅3 D ┐D

+ 𝐴┐𝑆𝑅1┐𝑅2𝑅3

┐A┐B 0 0 0 0

+ 𝐴┐𝑆𝑅1┐𝑅2┐𝑅3

+ 𝐴┐𝑆┐𝑅1𝑅2𝑅3 ┐AB 0 0 0 0

+ 𝐴┐𝑆┐𝑅1┐𝑅2𝑅3 AB 0 0 1 1

+ 𝐴┐𝑆┐𝑅1𝑅2┐𝑅3

A┐B 0 0 1 0

Mapa de Karnaugh.

//robert Ecuación:

┐C┐D ┐CD C C

D ┐D

//robert

┐A┐B m0 m1 m3 m2 S0= notC and D or C and not D

S1= B and not C or B and D or not B and C and D

┐AB m8 m9 m11 m10

S2= A and not C or not A and C and D or not A

AB m24 m25 m27 m26

and B and C or A and not B and not C electromecánicos, y actualmente es usado para

S3= A and C and D or A and B and C facilitar la corrección de errores en los sistemas

de comunicaciones, tales como algunos

sistemas de televisión por cable y la televisión

Marco Teórico digital terrestre.

Binario: El sistema binario, llamado también VHDL: es un lenguaje de especificación

sistema diádicoenciencias de la computación, definido por el IEEE (Institute of Electrical and

es un sistema de numeración en el que los Electronics Engineers) (ANSI/IEEE 1076-1993)

números se representan utilizando solamente utilizado para describir circuitos digitales y para

dos cifras: cero y uno (0 y 1). la automatización de diseño electrónico.

Es uno de los sistemas que se utilizan en las VHDL es acrónimo proveniente de la

computadoras, debido a que estas trabajan combinación de dos acrónimos: VHSIC (Very

internamente con dos niveles de voltaje, por lo High Speed Integrated Circuit) y HDL

cual su sistema de numeración natural es el (Hardware Description Language). Aunque

sistema binario. puede ser usado de forma general para

describir cualquier circuito digital se usa

Tabla de verdad: Una tabla de verdad, o tabla principalmente para programar PLD

de valores de verdad, es una tabla que muestra (Programmable Logic Device - Dispositivo

el valor de verdad de una proposición Lógico Programable), FPGA (Field

compuesta, para cada combinación de verdad Programmable Gate Array), ASIC y similares.

que se pueda asignar. Fue desarrollada por

Charles Sanders Peirce por los años 1880, pero Nexys 4: es una plataforma de desarrollo de

el formato más popular es el que introdujo circuito digital completa, lista para usar, basada

Ludwig Wittgenstein en su Tractatus logico- en la última matriz de compuerta programable

philosophicus, publicado en 1921. de campo (FPGA) Artix-7 ™ de Xilinx®.Con FPGA

de gran capacidad, generosas memorias

Mapa de Karnaugh: Un mapa de Karnaugh externas y colección de USB, Ethernet y otros

(también conocido como tabla de Karnaugh o puertos, el Nexys4 puede alojar diseños que

diagrama de Veitch, abreviado como Mapa-K o van desde circuitos combinatorios

Mapa-KV) es un diagrama utilizado para la introductorios hasta potentes procesadores

simplificación de funciones algebraicas integrados. Varios periféricos incorporados, que

Booleanas. El mapa de Karnaugh fue inventado incluyen un acelerómetro, sensor de

en 1950 por Maurice Karnaugh, un físico y temperatura, micrófono digital MEMs, un

matemático de los laboratorios Bell. amplificador de altavoz y varios dispositivos de

Código Gray: El código binario reflejado o E/S, permiten utilizar el Nexys4 para una amplia

código Gray, nombrado así en honor del gama de diseños sin necesidad de otros

investigador Frank Gray, es un sistema de componentes.

numeración binario en el que dos palabras Desarrollo del trabajo experimental

consecutivas difieren solamente en uno de sus

dígitos. Diagrama optimizado:

El código Gray fue diseñado originalmente para

prevenir señales ilegales (señales falsas o

viciadas en la representación) de los switches

//robert

Código VHDL:

---------------------------------------

---------------------------------------

---

-- Company:

-- Engineer:

--

-- Create Date: 20:27:40 29/06/2018

-- Design Name:

-- Module Name: Votacion - a1 :

Behavioral in

-- Project Name:

-- Target Devices: STD_LOGIC;

-- Tool versions: a2 : in STD_LOGIC;

-- Description: b1 : in STD_LOGIC;

-- b2 : in STD_LOGIC;

-- Dependencies: sa : out STD_LOGIC;

-- sb : out STD_LOGIC);

-- end pp;

architecture Behavioral of Votacion is

begin

sa <=(j and a1 and not a2 and b1)or (j

and a1 and a2 and b2)or

(j and a2 and not b1 and b2);

sb <= (j and a1 and not a2 and not b1

and b2)or

(j and a1 and b1 and not b2)or

(j and a1 and a2 and b1)or

(j and a2 and b1 and b2)or

(j and not a1 and a2 and b2);

end Behavioral;

Revision: Resultados

-- Revision 0.01 - File Created

-- Additional Comments: //robert

--

---------------------------------------

---------------------------------------

--- library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library

declaration if using -- arithmetic

functions with Signed or Unsigned

values --use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library

declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity pp is

Port ( j : in STD_LOGIC;

Conclusión

El conocimiento de la teoría es una ventaja en

el momento de programación, no solo para la

implementación de este, sino también para la

resolución de problemas, buscando la

respuesta optima (la que mejor se acople a la

resolución del problema).

Referencias

Anónimo. (2018). Código Gray. 07-06-2018, de

Wikipedia Sitio web:

https://es.wikipedia.org/wiki/C%C3%B3digo_Gr

ay

Anónimo. (2018). Mapa de Karnaugh. 07-06-

2018, de Wikipedia Sitio web:

https://es.wikipedia.org/wiki/Mapa_de_Karnau

gh

Anónimo. (2018). Tabla de verdad. 07-06-2018,

de Wikipedia Sitio web:

https://es.wikipedia.org/wiki/Tabla_de_verdad

Anónimo. (2018). Sistema binario. 07-06-2018,

de Wikipedia Sitio web:

https://es.wikipedia.org/wiki/Sistema_binario

Anónimo. (2018). VHDL. 07-06-2018, de

Wikipedia Sitio web:

https://es.wikipedia.org/wiki/VHDL

Anónimo. (2018). Nexys 4 DDR. 07-06-2018, de

DIGILENT Sitio web:

https://reference.digilentinc.com/reference/pr

ogrammable-logic/nexys-4-ddr/start

También podría gustarte

- Actividad #3 Investiga Sobre La RSEDocumento11 páginasActividad #3 Investiga Sobre La RSEoliver mauricio oliva suarezAún no hay calificaciones

- TAREA1Documento6 páginasTAREA1ricardo monteroAún no hay calificaciones

- Diseño de decodificador BCD a decimalDocumento5 páginasDiseño de decodificador BCD a decimalOlivia De Guevara MorenoAún no hay calificaciones

- Contador JohnsonDocumento7 páginasContador JohnsonNelson Pato Suárez0% (1)

- Test de Manejo de ConflictosDocumento15 páginasTest de Manejo de Conflictosorientacion-escolar1Aún no hay calificaciones

- 02 - Practica Dirigida-Tema 03 Series de FourierDocumento10 páginas02 - Practica Dirigida-Tema 03 Series de FourierSteven Boris Soriano CláudioAún no hay calificaciones

- Operacion de Una Micro-Red PDFDocumento26 páginasOperacion de Una Micro-Red PDFDaniel Ochoa YepesAún no hay calificaciones

- BioestadisticaDocumento2 páginasBioestadisticaMARIA GUADALUPE PECH PEREZAún no hay calificaciones

- Interpolacion Metodo DirectoDocumento10 páginasInterpolacion Metodo DirectoXavy ZuritaAún no hay calificaciones

- Ontologia de La TrascendenciaDocumento28 páginasOntologia de La TrascendenciaRaúl García CastilloAún no hay calificaciones

- Simulacro Química General 1 revisión intentoDocumento4 páginasSimulacro Química General 1 revisión intentoRACHEL MARLEN GRAMAJO GARCIAAún no hay calificaciones

- Sumador de 3 bits con display y decodificador 7447Documento6 páginasSumador de 3 bits con display y decodificador 7447Saul Maza AcaroAún no hay calificaciones

- TrabajoDocumento2 páginasTrabajoWisinSanchezAún no hay calificaciones

- Instrumentacion Unidad 4 Parte 3 - Probabilidad y EstadisticaDocumento14 páginasInstrumentacion Unidad 4 Parte 3 - Probabilidad y EstadisticaJuan Jose Ángel GutiérrezAún no hay calificaciones

- Ejercicios Hipótesis Dos MuestrasDocumento7 páginasEjercicios Hipótesis Dos MuestrasLENIN VLADIMIR INGA HINOSTROZAAún no hay calificaciones

- La Curva Característica de Un Diodo Zener y Un Diodo TúnelDocumento2 páginasLa Curva Característica de Un Diodo Zener y Un Diodo TúnelEDGARAún no hay calificaciones

- Practica 4Documento7 páginasPractica 4David AckermanAún no hay calificaciones

- Solución de Ejercicios Metodos Numericos ChaprasDocumento10 páginasSolución de Ejercicios Metodos Numericos ChaprasAlbrecht HerradoraAún no hay calificaciones

- Pendulo TripleDocumento5 páginasPendulo Triplejorge molinaAún no hay calificaciones

- Sintesis Del Trabajo: A Bernoulli's Law Lab in A BottleDocumento5 páginasSintesis Del Trabajo: A Bernoulli's Law Lab in A BottleEduardoAún no hay calificaciones

- Práctica 1 - Probabilidades Tarea ResueltaDocumento10 páginasPráctica 1 - Probabilidades Tarea ResueltaJen Elena PeredaAún no hay calificaciones

- Práctica 2Documento23 páginasPráctica 2Carlos MoralesAún no hay calificaciones

- La Ley de Faraday Caracteriza La Caída Del Voltaje A Través de Un InductorDocumento4 páginasLa Ley de Faraday Caracteriza La Caída Del Voltaje A Través de Un InductorStefanía Beltrán CruzAún no hay calificaciones

- Parcial Ecuaciones DiferencialesDocumento4 páginasParcial Ecuaciones DiferencialesAlexander NievesAún no hay calificaciones

- Circuitos lógicos: expresiones booleanas, tablas de verdad y diseñoDocumento2 páginasCircuitos lógicos: expresiones booleanas, tablas de verdad y diseñoDaniel GutierrezAún no hay calificaciones

- Hoja 6 Anthony Collaguazo PDFDocumento6 páginasHoja 6 Anthony Collaguazo PDFAnthony CollaguazoAún no hay calificaciones

- Diseño y Aplicación de Un Sistema Secuencial Con GAL22V10DDocumento17 páginasDiseño y Aplicación de Un Sistema Secuencial Con GAL22V10DIván Herrera0% (1)

- Pensamiento, Sentimiento, Benevolencia y Justicia en Los Actos HumanosDocumento3 páginasPensamiento, Sentimiento, Benevolencia y Justicia en Los Actos HumanosLuis Daniel Mendez SosaAún no hay calificaciones

- Tarea COMPLETA INTER 2 VACAS JUNIO-2020Documento10 páginasTarea COMPLETA INTER 2 VACAS JUNIO-2020Erick Noe Gómez LópezAún no hay calificaciones

- EstrocturasDocumento45 páginasEstrocturasWiichoo GArcia AriiasAún no hay calificaciones

- Ejercicios Resueltos de InterpolacionDocumento7 páginasEjercicios Resueltos de InterpolacionJael RuizAún no hay calificaciones

- Reporte de laboratorio sobre compuertas lógicas y álgebra de Boole de la UNIDocumento4 páginasReporte de laboratorio sobre compuertas lógicas y álgebra de Boole de la UNIAder Hariel Treminio Montoya100% (1)

- Teclado PianoDocumento8 páginasTeclado PianoDarla MercadoAún no hay calificaciones

- Practica de Calculo 2 PDFDocumento47 páginasPractica de Calculo 2 PDFsergio zeballosAún no hay calificaciones

- Diseño de Elementos de Maquinas II-Problemas Engranajes Rectos - JOSE BLANCO MARACAYO 2012-0997Documento2 páginasDiseño de Elementos de Maquinas II-Problemas Engranajes Rectos - JOSE BLANCO MARACAYO 2012-0997Jose MaracayoAún no hay calificaciones

- FSM Moore MealyDocumento4 páginasFSM Moore MealyChongjavi LoorAún no hay calificaciones

- Problemas 1 y 2Documento5 páginasProblemas 1 y 2Jehiel LópezAún no hay calificaciones

- HT1 - AP3N - Sergio Garzaro - 201700542Documento3 páginasHT1 - AP3N - Sergio Garzaro - 201700542Sergio RafaelAún no hay calificaciones

- Proyecto 2Documento8 páginasProyecto 2juanitoAún no hay calificaciones

- Taller 1Documento3 páginasTaller 1mandingo avelardoAún no hay calificaciones

- AngryBirdsVelocidadParabólicaDocumento13 páginasAngryBirdsVelocidadParabólicaAndres PaterninaAún no hay calificaciones

- Ecuaciones DiferencialesDocumento13 páginasEcuaciones DiferencialesG-sus V-gaAún no hay calificaciones

- Taller 2 202102 - CE86 - Sol - v2Documento5 páginasTaller 2 202102 - CE86 - Sol - v2Angélica Aroni AllccaAún no hay calificaciones

- 2.3.8 Lab Navigate The Ios by Using Tera Term For Console Connectivity Es XLDocumento9 páginas2.3.8 Lab Navigate The Ios by Using Tera Term For Console Connectivity Es XLForne Marc Ric EnriqueAún no hay calificaciones

- ProblemDocumento4 páginasProblemViridiana Arias0% (1)

- Homouniones y Heterouniones LaserDocumento7 páginasHomouniones y Heterouniones LaserDiego HDAún no hay calificaciones

- Practica-Contador de 0-7 VHDLDocumento13 páginasPractica-Contador de 0-7 VHDLR He MaAún no hay calificaciones

- Amplificador de audio de dos etapas con transistoresDocumento5 páginasAmplificador de audio de dos etapas con transistoresMijail GarriazoAún no hay calificaciones

- Investigaciones de Nodos, Estrella-Delta & SuperposiciónDocumento3 páginasInvestigaciones de Nodos, Estrella-Delta & SuperposiciónSerna ReynaAún no hay calificaciones

- Lab Masa-Resorte PenduloDocumento11 páginasLab Masa-Resorte PenduloDiego ArdilaAún no hay calificaciones

- Laboratorio 2 de Sistemas Digitales 1 UNIDocumento5 páginasLaboratorio 2 de Sistemas Digitales 1 UNIDaniel Zavala100% (1)

- Taller 1Documento2 páginasTaller 1Melani Vasquez100% (1)

- Week2 ZTALLER2Documento1 páginaWeek2 ZTALLER2JORGE FREJA MACIAS0% (1)

- Onda Plana en Medio Sin PerdidasDocumento4 páginasOnda Plana en Medio Sin PerdidasNacion xsAún no hay calificaciones

- Practica Inf 111Documento8 páginasPractica Inf 111Oliver ApalaAún no hay calificaciones

- Preinforme SistemasDocumento3 páginasPreinforme Sistemaslokillo100% (1)

- Características del transistor y sus aplicacionesDocumento11 páginasCaracterísticas del transistor y sus aplicacionesMichaelAlejandroPomaAún no hay calificaciones

- Pauta Examen I MM401 PDFDocumento4 páginasPauta Examen I MM401 PDFCristhian Josué Rápalo100% (1)

- Solucionario Del Examen Parcial II de Electronic A DigitalDocumento4 páginasSolucionario Del Examen Parcial II de Electronic A DigitalLuis Armando LozadaAún no hay calificaciones

- Solucionario Del Examen Parcial II de Electronic A DigitalDocumento5 páginasSolucionario Del Examen Parcial II de Electronic A Digitalsuperminded50% (2)

- Practica 1 - Decodificadores y CodificadoresDocumento9 páginasPractica 1 - Decodificadores y CodificadoresdiegoAún no hay calificaciones

- Práctica Microondas Electrónica DigitalDocumento18 páginasPráctica Microondas Electrónica DigitalEduardo Canto0% (1)

- Laboratorio de Circuitos Combinacionales - 1103147Documento9 páginasLaboratorio de Circuitos Combinacionales - 1103147CARLOSAún no hay calificaciones

- Definicion de FritasDocumento15 páginasDefinicion de FritasIngrid ContrerasAún no hay calificaciones

- Arenas 13Documento157 páginasArenas 13Liga Intersindical UASAún no hay calificaciones

- Cimentaciones SuperficialesDocumento8 páginasCimentaciones SuperficialesWilsonDELACruzOvandoAún no hay calificaciones

- Agregar imagen y mejora continuaDocumento75 páginasAgregar imagen y mejora continuaFrank Santamaria RamosAún no hay calificaciones

- Lengua Clase Ndeg9 Del 11 de Junio de 2022Documento4 páginasLengua Clase Ndeg9 Del 11 de Junio de 2022María de los Ángeles Pérez BlancoAún no hay calificaciones

- Algebra Lineal Taller 7Documento15 páginasAlgebra Lineal Taller 7Eduarda AllanAún no hay calificaciones

- Geografía Sem4Documento17 páginasGeografía Sem4cubjerhct1Aún no hay calificaciones

- Estudio de caso sobre ansiedad y orientación sexualDocumento12 páginasEstudio de caso sobre ansiedad y orientación sexualJOSE PACHECOAún no hay calificaciones

- Cuadernillo Del Serums 2015Documento32 páginasCuadernillo Del Serums 2015Patricia Jessel Lopez MarinAún no hay calificaciones

- Check list diario inspección arnes línea anclajeDocumento1 páginaCheck list diario inspección arnes línea anclajeAnderson Alejandro Benites ZelayaAún no hay calificaciones

- De La Neurodiversidad A La Neurodidactica. Prof. Aldo Ocampo GonzalezDocumento22 páginasDe La Neurodiversidad A La Neurodidactica. Prof. Aldo Ocampo GonzalezAnonymous PaxF8KppVAún no hay calificaciones

- Construcción de OrbialesDocumento5 páginasConstrucción de Orbialeshechicera2104Aún no hay calificaciones

- La Lengua Oculta. Vargas Llosa. El País. Diciembre 2020Documento4 páginasLa Lengua Oculta. Vargas Llosa. El País. Diciembre 2020julia bayleAún no hay calificaciones

- Sistemas de Producción de Rumiantes ParametrosDocumento14 páginasSistemas de Producción de Rumiantes ParametrosCynthia Rebeca Monge-EguezAún no hay calificaciones

- Recepción de la obra de Judith ButlerDocumento3 páginasRecepción de la obra de Judith ButlerYelliAgustinaAún no hay calificaciones

- Modulo 7.2 PDFDocumento11 páginasModulo 7.2 PDFKIESER DE LA PEÑA GASPARAún no hay calificaciones

- MS-01-176 - AntiretornoDocumento17 páginasMS-01-176 - AntiretornoqmasdaAún no hay calificaciones

- PCM, Logica de FuncionamientoDocumento18 páginasPCM, Logica de FuncionamientoEdison MoralesAún no hay calificaciones

- Actividad Evaluativa - Proyectar El Mercado PDFDocumento5 páginasActividad Evaluativa - Proyectar El Mercado PDFAldair EspitiaAún no hay calificaciones

- Story CubesDocumento7 páginasStory CubesMaría Auxiliadora Jácome OrtegaAún no hay calificaciones

- 01salud MentalDocumento3 páginas01salud MentalAntonio TepoxAún no hay calificaciones

- 06 Textos ReferenciasDocumento24 páginas06 Textos ReferenciasSamy PaezAún no hay calificaciones

- Balance de Materia. Etapas. CascadasDocumento11 páginasBalance de Materia. Etapas. CascadasJimmy Sierra CcorahuaAún no hay calificaciones

- Bases de La Hemodinamia PDFDocumento25 páginasBases de La Hemodinamia PDFLina PeñarandaAún no hay calificaciones

- EVAPOTRANSPIRACIÓNDocumento25 páginasEVAPOTRANSPIRACIÓNKevin MorenoAún no hay calificaciones

- Ejercicios 4 - Resueltos Perdida Deposito-TanqueDocumento12 páginasEjercicios 4 - Resueltos Perdida Deposito-TanqueJORGE LORENZO CHUQUIMIA CALDERONAún no hay calificaciones