Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Flip Flop

Flip Flop

Cargado por

Johann Caceres FloresTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Flip Flop

Flip Flop

Cargado por

Johann Caceres FloresCopyright:

Formatos disponibles

Universidad nacional mayor de san marcos - FIEE

LABORATORIO 2 – CIRCUITOS LATCH Y FLIP – FLOPS

I. OBJETIVO:

- Analizar el principio de funcionamiento de diferentes tipos de Flip-Flops utilizados comercialmente.

- Implementar circuitos secuenciales utilizando estoso dispositivos de almacenamiento

II. MATERIALES Y EQUIPO:

- Protoboard, cables de conexión.

- CI: 74LS00, 74LS02, 74LS74, 74LS76

- Diodos LED

- Fuente DC +5v, VOM, generador de pulsos

III. PARTE EXPERIMENTAL:

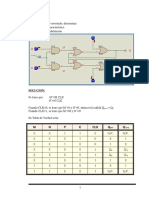

1. Completar para los circuitos mostrados su tabla de verdad Y su diagrama de señales

CIRCUITO 1

-

Si R Q Q

0 0 1 0

0 1 0 1

1 0 1 0

1 1 no no

CIRCUITO 2

- -

Si R Q

-

Q

0 0 NO NO

0 1 1 0

1 0 0 1

1 1 1 0

Circuitos digitales laboratorio Página 1

Universidad nacional mayor de san marcos - FIEE

Diagrama de señales

CIRCUITO 3

EN R S Qn+1

0 X X Qn

1 0 0 Qn

1 0 1 1

1 1 0 0

1 1 1 NP(1 y 1)

CIRCUITOS 1, 2 Y 3

Circuitos digitales laboratorio Página 2

Universidad nacional mayor de san marcos - FIEE

2. Verificar la operación de un FLIP FLOP tipo D

CIRCUITO 4

PR CL D CLK Qn+1

1 1 X X Qn

1 0 X X 1

0 1 X X 0

0 0 0 TPP 0

0 0 1 TPP 1

3. Verificar la operación de un FLIP FLOP tipo JK

CIRCUITO 5

PR CL J K CLK Qn+1

1 1 X X X 1

1 0 X X X 1

0 1 X X X 0

0 0 0 0 TPN Qn

0 0 0 1 TPN 0

0 0 1 0 TPN 1

0 0 1 1 TPN ∼Qn

Circuitos digitales laboratorio Página 3

Universidad nacional mayor de san marcos - FIEE

IV. CUESTIONARIO FINAL

1. Utilizando mapas de Karnaugh, obtenga las ecuaciones características a partir de las

tablas para los biestables SR, JK, D, T

BIESTABLE SR (CIRCUITO 1)

R S Qn Qn+1

0 0 0 0

0 0 1 1

0 1 X 1

1 0 X 0

1 1 X X

RS\Qn 0 1 Qn+1 = S + (∼R)*Qn

00 0 1

01 1 1

11 X X

10 0 0

BIESTABLE D (CIRCUITO 4)

D Qn Qn+1

0 X 0

1 X 1

D\Qn 0 1

0 0 0

1 1 1

Qn+1 = D

Circuitos digitales laboratorio Página 4

Universidad nacional mayor de san marcos - FIEE

BIESTABLE JK (CIRCUITO 5)

J K Qn Qn+1

0 0 0 0

0 0 1 1

0 1 X 0

1 0 X 1

1 1 0 1

1 1 1 0

JK\Qn 0 1

00 0 1

01 0 0 Qn+1 = J*(∼Qn) + (∼K)*Qn

11 1 0

10 1 1

BIESTABLE T

T Qn Qn+1

0 0 0

0 1 1

1 0 1

1 1 0

T\Qn 0 1

0 0 1

1 1 0 Qn+1 = T*(∼Qn) + (∼T)*Qn = T (+) Qn

2. ¿Cuál es el nivel lógico requerido en la entrada CLK para permitir la transferencia del

valor D a la salida Q del FLIP FLOP tipo D?

Para que se transfiera el valor D a la salida Q del FLIP FLOP, se necesitará una transición, ésta

debe ser de pendiente positiva (TPP), de modo que, en el mismo instante en que CLK cambie de 0

a 1, cambiará también la salida Q de acuerdo a lo especificado en D.

Circuitos digitales laboratorio Página 5

Universidad nacional mayor de san marcos - FIEE

3. Indique en el siguiente circuito RS maestro esclavo, ¿Por qué las señales CP1 y CP2 deben

ser complementarias? Muestre posibles circuitos para obtener estas señales CP1 y CP2

En el circuito mostrado, podemos ver dos habilitadores, los cuales funcionan junto con dos

LATCH, observamos que, si los dos habilitadores (CP1 Y CP2) están en estado 1 al mismo tiempo,

entonces Q1 cambiará simultáneamente con la activación de CP2, entonces, en la salida de la

compuerta U2A se generarán cambios repentinos debido a la inestabilidad que se producirá en el

circuito, dándonos respuestas inesperadas.

Por el contrario, si tenemos por ejemplo CP1 activado y CP2 desactivado, obtendremos la salida

Q1, luego, al desactivar CP1 y activar CP2 obtendremos la salida Q2, haciendo este procedimiento

aseguramos el correcto traslado de datos del LATCH 1(maestro) al LATCH 2(esclavo)

Para citar un caso del FLIP FLOP SR un posible circuito para obtener que las señales CP1 y CP2

sean complementarias sería:

La compuerta NO asegurará que CP1 Y CP2 sean complementarias, así, el bit asignado a set

pasará a Q1 cuando CP1 esté en ON, y cuando CP1 este en OFF pasará a la salida Q2, este es el

principio de la transferencia de datos en los registros.

Circuitos digitales laboratorio Página 6

Universidad nacional mayor de san marcos - FIEE

¿Qué sucedería en el caso del FLIP FLOP JK Maestro-Esclavo?

En este caso para que las dos entradas habilitadoras (en este caso CLK) sean complementarias, la

configuración sería la siguiente:

4. Analizar los resultados obtenidos en la parte experimental.

Los datos recogidos en el laboratorio concordaron en todo aspecto con los previstos en el informe

previo y las simulaciones, se observó que cada biestable y cada FLIP FLOP responden distinto a

las diferentes señales lógicas de entrada.

V. CONCLUSIONES Y OBSERVACIONES

- Concluimos que los LATCH son la base de los FLIP FLOP, que haciendo modificaciones en éstos

lograremos distintos tipos de FLIP FLOP.

- Se pudo observar y verificar los contactos de los siguientes integrados:

74LS02 (compuertas NOR), 74LS00 (compuertas NAND), 74LS74 (FLIP FLOP tipo D), 74LS76

(FLIP FLOP TIPO JK).

- Las configuraciones de MAESTRO-ESCLAVO son usadas en situaciones en la que se ve un

riesgo de secuencia en la transferencia de datos, actualmente, la mayoría de CI no presentan

esta dificultad, por lo cual ya no se usa mucho.

Circuitos digitales laboratorio Página 7

También podría gustarte

- Tarea Capitulo 2 EconomiaDocumento13 páginasTarea Capitulo 2 EconomiaJohann Caceres Flores77% (13)

- BiestablesDocumento8 páginasBiestablesanon_251086732Aún no hay calificaciones

- Redes IndustrialesDocumento186 páginasRedes IndustrialesJT 230% (1)

- Actividades de LaboratorioDocumento5 páginasActividades de LaboratorioEliazar Delgado CollantesAún no hay calificaciones

- Tarea de Sistemas DigitalesDocumento22 páginasTarea de Sistemas DigitalesXavier PalaciosAún no hay calificaciones

- Preguntas de Repaso Capitulo 2Documento5 páginasPreguntas de Repaso Capitulo 2Johann Caceres Flores88% (8)

- Ejercicios para ResolverDocumento10 páginasEjercicios para ResolverKevin ContrerasAún no hay calificaciones

- Cálculo y diseño de estructuras de materiales compuestos de fibra de vidrioDe EverandCálculo y diseño de estructuras de materiales compuestos de fibra de vidrioAún no hay calificaciones

- Transformadores ElectricosDocumento31 páginasTransformadores ElectricosJohann Caceres Flores100% (1)

- Relés ProgramablesDocumento7 páginasRelés ProgramablesdranzerAún no hay calificaciones

- Informe Digitales 1Documento6 páginasInforme Digitales 1Raul Guillen PeñaAún no hay calificaciones

- Automatismos SecuencialesDocumento18 páginasAutomatismos SecuencialesPEDRO JAIR NAVAS CUADROS100% (1)

- Informe 2, SdiiDocumento25 páginasInforme 2, SdiiCarlos Perez SalcedoAún no hay calificaciones

- Conversiones Entre BiestablesDocumento90 páginasConversiones Entre BiestablesManuel CoaguilaAún no hay calificaciones

- Informe Digitales 4Documento10 páginasInforme Digitales 4Rodrigo ZuñigaAún no hay calificaciones

- Informe Final 4 (Digitales 2)Documento10 páginasInforme Final 4 (Digitales 2)Leonardo Ponce GarciaAún no hay calificaciones

- Sistemas Digitales III Laboratorio 1Documento10 páginasSistemas Digitales III Laboratorio 1Pamela KarenAún no hay calificaciones

- Informe 6 Flip FlopDocumento10 páginasInforme 6 Flip FlopEddy Fuentes CasteloAún no hay calificaciones

- Diseño Logico T4Documento43 páginasDiseño Logico T4Isthar D AvilaAún no hay calificaciones

- Pre Informe 1Documento9 páginasPre Informe 1Angelo CruzAún no hay calificaciones

- Sistemas Digitales Lab 1Documento11 páginasSistemas Digitales Lab 1Pamela KarenAún no hay calificaciones

- Informe 4 Flip FlopsDocumento16 páginasInforme 4 Flip FlopsJonathan Harold Quevedo PulidoAún no hay calificaciones

- Hoja de Datos 8Documento3 páginasHoja de Datos 8Diego ChitupantaAún no hay calificaciones

- TEMA 4 Circuito AntirrboteDocumento12 páginasTEMA 4 Circuito AntirrboteWenAn MeriosAún no hay calificaciones

- Preguntas Sobre Flip Flop (Correjido)Documento3 páginasPreguntas Sobre Flip Flop (Correjido)Steve LopezAún no hay calificaciones

- Reconocimiento de Los Flip FlopsDocumento4 páginasReconocimiento de Los Flip FlopsJherico RetesAún no hay calificaciones

- Informe 4 Flip FlopsDocumento16 páginasInforme 4 Flip FlopsMarco Antonio Ergueta YujraAún no hay calificaciones

- Informe N1 de Laboratorio Sistemas DigitalesDocumento14 páginasInforme N1 de Laboratorio Sistemas DigitalesWilmer Cubas SolanoAún no hay calificaciones

- Desarrollo de La Sesion - N°08 EyeDocumento41 páginasDesarrollo de La Sesion - N°08 Eyewarcraf realAún no hay calificaciones

- Flip FlopsDocumento5 páginasFlip FlopsFabricio Fabián Fernández BáezAún no hay calificaciones

- Informe DigitalesDocumento6 páginasInforme Digitalesxavier SAún no hay calificaciones

- Flip FlopsDocumento2 páginasFlip FlopsDivarAún no hay calificaciones

- ResoluciónDocumento21 páginasResoluciónValeria Andrea Nina ArrescurenagaAún no hay calificaciones

- UNIDAD III Contadores SINCRONOSDocumento10 páginasUNIDAD III Contadores SINCRONOSLuel MarquezAún no hay calificaciones

- EJ T4Ftos SolucionesDocumento3 páginasEJ T4Ftos SolucionesPatiño JAún no hay calificaciones

- Sistemas DigitalesDocumento19 páginasSistemas DigitalesPerez AldairAún no hay calificaciones

- Desarrollo de La Sesion - N°08 CoDocumento43 páginasDesarrollo de La Sesion - N°08 CoTHIAGO MORALES TORRESAún no hay calificaciones

- Laboratorio4 EE644 Galindez Granados Honorio Rosales1Documento25 páginasLaboratorio4 EE644 Galindez Granados Honorio Rosales1geraldine.versionAún no hay calificaciones

- Tarea Domic SistemasDocumento29 páginasTarea Domic SistemasMichael Infantes HuacancaAún no hay calificaciones

- EXaDigII FINAL24 06 10Documento2 páginasEXaDigII FINAL24 06 10jhonAún no hay calificaciones

- Tarea Domiciliaria 1 PDFDocumento26 páginasTarea Domiciliaria 1 PDFDenni'z H. YrigoinAún no hay calificaciones

- Informe RegistroDocumento11 páginasInforme Registroxavier SAún no hay calificaciones

- Unidad IV - Circuitos SecuencialesDocumento30 páginasUnidad IV - Circuitos SecuencialesGerardo TelloAún no hay calificaciones

- Lab12 - C16A - Quispe Romero, Steven, Alvarez CahuanaDocumento12 páginasLab12 - C16A - Quispe Romero, Steven, Alvarez CahuanaSteven Dave QRAún no hay calificaciones

- Informe Latch y Flip FlopDocumento11 páginasInforme Latch y Flip FlopAlex Vin0% (1)

- 8-4 Control de Ciclo de Taladrado y Control de Dos Soldadoras - Ramos Pastrana Gary GabrielDocumento18 páginas8-4 Control de Ciclo de Taladrado y Control de Dos Soldadoras - Ramos Pastrana Gary GabrielGARY GABRIEL RAMOS PASTRANAAún no hay calificaciones

- 8-4 Control de Ciclo de Taladrado y Control de Dos Soldadoras - Ramos Pastrana Gary GabrielDocumento18 páginas8-4 Control de Ciclo de Taladrado y Control de Dos Soldadoras - Ramos Pastrana Gary GabrielGARY GABRIEL RAMOS PASTRANAAún no hay calificaciones

- PrevioDocumento13 páginasPrevioSel13Aún no hay calificaciones

- Sistemas Digitales I Previo IDocumento8 páginasSistemas Digitales I Previo IPamela KarenAún no hay calificaciones

- Reporte Proyecto Final SemaforoDocumento11 páginasReporte Proyecto Final SemaforoManuel GómezAún no hay calificaciones

- Cdi Experiencia 5 - 2020 TareaDocumento13 páginasCdi Experiencia 5 - 2020 TareaDanilo Andre LuqueAún no hay calificaciones

- Final 4Documento11 páginasFinal 4Angelo Francescoli Castillo GuerreroAún no hay calificaciones

- PrÁcticas de Laboratorio (E.d.)Documento12 páginasPrÁcticas de Laboratorio (E.d.)Néstor GaleraAún no hay calificaciones

- EJ T4Ftos SolucionesDocumento3 páginasEJ T4Ftos SolucionesRaquel GómezAún no hay calificaciones

- Laboratorio 4 (E. Digital)Documento7 páginasLaboratorio 4 (E. Digital)NiltonRamírezAún no hay calificaciones

- Sistemas Digitales Problemas 2 PDFDocumento27 páginasSistemas Digitales Problemas 2 PDFElmer525Aún no hay calificaciones

- Pre-Informe 7Documento10 páginasPre-Informe 7Raúl A.Aún no hay calificaciones

- Soluciones Ejercicios de Sistemas Digitales SecuencialesDocumento3 páginasSoluciones Ejercicios de Sistemas Digitales SecuencialesMaria Elena SalgadoAún no hay calificaciones

- Archivorubrica 202061491415Documento4 páginasArchivorubrica 202061491415Giovanni LoaizaAún no hay calificaciones

- Sistemas DigitalesDocumento29 páginasSistemas DigitalesdardozAún no hay calificaciones

- Domo TicaDocumento14 páginasDomo TicaAndrea ParadaAún no hay calificaciones

- Laboratorio 2Documento3 páginasLaboratorio 2Alain ChambiAún no hay calificaciones

- Actividad de Aprendizaje No 3 Analisis y Diseno de CircuitosDocumento4 páginasActividad de Aprendizaje No 3 Analisis y Diseno de CircuitosDark Angel26Aún no hay calificaciones

- Actividad 3. Análisis y Diseño de CircuitosDocumento4 páginasActividad 3. Análisis y Diseño de CircuitosDark Angel26Aún no hay calificaciones

- Trabajo Práctico #6 FINALDocumento34 páginasTrabajo Práctico #6 FINALANTHONY VALENCIA ZUTAAún no hay calificaciones

- Diseño Digital Actividad 3Documento5 páginasDiseño Digital Actividad 3ALfredo PAún no hay calificaciones

- Parcial 2 Tipo BDocumento1 páginaParcial 2 Tipo BjonaAún no hay calificaciones

- EasyPact EZC - EZC250N3250Documento3 páginasEasyPact EZC - EZC250N3250Johann Caceres FloresAún no hay calificaciones

- Memoria DescriptivaDocumento2 páginasMemoria DescriptivaJohann Caceres FloresAún no hay calificaciones

- Lampara de Emergencia Led SMD 9707ulDocumento1 páginaLampara de Emergencia Led SMD 9707ulJohann Caceres FloresAún no hay calificaciones

- Ficha Tecnica Solaris Parte 1Documento4 páginasFicha Tecnica Solaris Parte 1Johann Caceres FloresAún no hay calificaciones

- Formulacion Proyecto Baldosa Avance 2.2Documento19 páginasFormulacion Proyecto Baldosa Avance 2.2Johann Caceres FloresAún no hay calificaciones

- BC Tes TMP 2684 PDFDocumento101 páginasBC Tes TMP 2684 PDFJohann Caceres FloresAún no hay calificaciones

- Ficha Tecnica Ecco Parte 1Documento1 páginaFicha Tecnica Ecco Parte 1Johann Caceres FloresAún no hay calificaciones

- Practica 7 TurbomaquinasDocumento7 páginasPractica 7 TurbomaquinasJohann Caceres FloresAún no hay calificaciones

- Trafos de AislamientoDocumento2 páginasTrafos de AislamientoJohann Caceres FloresAún no hay calificaciones

- R1.2 Separata2 de Turbomaquinas Uc3 PDFDocumento47 páginasR1.2 Separata2 de Turbomaquinas Uc3 PDFJohann Caceres FloresAún no hay calificaciones

- Cuaderno de Sistema Electrico de Potencia IDocumento70 páginasCuaderno de Sistema Electrico de Potencia IGersonBetancourtJimenez100% (4)

- Microeconomia Preguntas de Repaso Organizacion de La ProduccionDocumento3 páginasMicroeconomia Preguntas de Repaso Organizacion de La ProduccionJohann Caceres FloresAún no hay calificaciones

- Practica 2 TermicasDocumento3 páginasPractica 2 TermicasJohann Caceres FloresAún no hay calificaciones

- Practica Calificada 1Documento4 páginasPractica Calificada 1Johann Caceres FloresAún no hay calificaciones

- Upgrade The Ericsson Node B SoftwareDocumento8 páginasUpgrade The Ericsson Node B SoftwareheruAún no hay calificaciones

- Telesat Junio Julio10Documento132 páginasTelesat Junio Julio10formicheAún no hay calificaciones

- Principales Programas de WindowsDocumento14 páginasPrincipales Programas de Windowsinter conexionAún no hay calificaciones

- Parcial 1Documento6 páginasParcial 1alexandra garciaAún no hay calificaciones

- Regulador de Potencia en Ac Gestionado Por MicrocontroladorDocumento156 páginasRegulador de Potencia en Ac Gestionado Por Microcontroladordaniel borbonAún no hay calificaciones

- Tema #6 Introduccion A Sistemas de Control DigitalDocumento72 páginasTema #6 Introduccion A Sistemas de Control DigitalJmvMarceloVediaVargasAún no hay calificaciones

- Como FormatearDocumento5 páginasComo FormatearMaycol DundanDuAún no hay calificaciones

- Laboratorio 2 CE3 FinalDocumento16 páginasLaboratorio 2 CE3 FinalDiego Gutierrez AyalaAún no hay calificaciones

- MANTENIMIENTO PREVENTIVO HARDWARE Y SOFTWARE - Ensamble y Mantenimiento de Equipo de ComputoDocumento9 páginasMANTENIMIENTO PREVENTIVO HARDWARE Y SOFTWARE - Ensamble y Mantenimiento de Equipo de ComputoJuanita Nava LeyvaAún no hay calificaciones

- Como Separar Textos de Números y Números de Texto Usando Una FórmulaDocumento9 páginasComo Separar Textos de Números y Números de Texto Usando Una FórmulaysabelhynAún no hay calificaciones

- Asm PracticasDocumento18 páginasAsm Practicastlaloc125Aún no hay calificaciones

- Cat AvDocumento52 páginasCat AvAlereAún no hay calificaciones

- 2do. Básico Examen 2da UnidadDocumento7 páginas2do. Básico Examen 2da UnidadMargarita Igpa ScmAún no hay calificaciones

- CASO 1 - UPS - Global Operations With DIAD and WorldportDocumento3 páginasCASO 1 - UPS - Global Operations With DIAD and WorldportVivi SanchezAún no hay calificaciones

- ComputacionDocumento499 páginasComputacionValdr Nilsen StiglitzAún no hay calificaciones

- Fuentes Conmutadas en Televisores Sony Chasis BA3Documento15 páginasFuentes Conmutadas en Televisores Sony Chasis BA3maverik123100% (2)

- Acordeon Tecnología 180224Documento2 páginasAcordeon Tecnología 180224ALEJANDRA REYESAún no hay calificaciones

- Práctica de Laboratorio Huaman Barrientos Diego AlbertoDocumento4 páginasPráctica de Laboratorio Huaman Barrientos Diego AlbertoBrenda Brihit Maldonado de la CruzAún no hay calificaciones

- Ailg - Ev 2.2 - DNTDocumento11 páginasAilg - Ev 2.2 - DNTAndrea LealAún no hay calificaciones

- 5.1. Sensor Ultrasónico HC-SR04, Crear Una Alarma Con Arduino - HETPRODocumento15 páginas5.1. Sensor Ultrasónico HC-SR04, Crear Una Alarma Con Arduino - HETPROJorge Antonio GuerreroAún no hay calificaciones

- Manual Movistar Uno - Internet 2017Documento57 páginasManual Movistar Uno - Internet 2017Hernan ErasmoAún no hay calificaciones

- 1.3 MD Sistema de Conectividad y Seguridad InformaticaDocumento4 páginas1.3 MD Sistema de Conectividad y Seguridad InformaticaAlejandro CorderoAún no hay calificaciones

- Investigacion Instrucciones StringDocumento3 páginasInvestigacion Instrucciones StringJosé LozanoAún no hay calificaciones

- S15.s1 - Práctica Calificada 03Documento7 páginasS15.s1 - Práctica Calificada 03JEFERSON NUÑEZAún no hay calificaciones

- skyworthSmartTV43 QSGDocumento2 páginasskyworthSmartTV43 QSGgerman cassinottiAún no hay calificaciones

- Redes Frame RelayDocumento9 páginasRedes Frame RelayEstefany Gil NestarezAún no hay calificaciones