Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Test Lógica-Computadores-2014 PDF

Cargado por

Pilar PilarTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Test Lógica-Computadores-2014 PDF

Cargado por

Pilar PilarCopyright:

Formatos disponibles

Universitat Rovira i Virgili (URV) 5.

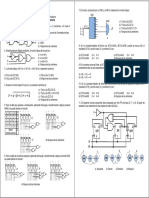

El circuito de la figura implementa la función lógica F(a,b,c) es:

Escola Tecnica Superior d’Enginyeria (ETSE)

Grau Enginyeria

Fonaments de Computadors, 2014 Q2 (1ª Conv.) a) Σ(0,2,4,5)

b) Σ(1,3,6,7)

Respuesta correcta +1, respuesta incorrecta –1/3 c) (0,2,4,5)

d) Ninguno de los anteriores

1. Usando el Algebra de Boole, el circuito equivale a:

a) Una AND de 3 entradas

b) Una NAND de 3 entradas 6. Para la siguiente tabla de verdad, aplicando Karnaugh y transformando a

c) Una NOR de 3 entradas lógica universal NAND, se obtiene:

d) Ninguna de las anteriores

a b c d F

X X X 0 0

2. Evaluar la función lógica F=/d+/(a*(/a*b+/b+c)) ( F d a (a b b c) ) X X 0 1 X

0 X 1 1 1

X 0 1 1 1

a) F(a,b,c,d)=(9,11,15)

1 1 1 1 0

b) F(a,b,c,d)=Σ(1,11,13,14,15)

c) F(a,b,c,d)=Σ(0,1,2,3,4,5,6,7,9,11,13,15)

d) Ninguna de las anteriores

3. La expresión lógica de F(a,b,c,d)=(3,4,10) es:

a) F=(/a+/b+c+d)*(/a+b+/c+/d)*(a+/b+c+/d)

b) F=(/a*/b*c*d)+(/a*b*/c*/d)+(a*/b*c*/d)

c) F=(a*b*/c*/d)+(a*/b*c*d)+(/a*b*/c*d)

d) Ninguna de las anteriores

4. La función lógica F(a,b,c)=Σ(2,3,5,6) se puede implementar con:

a) El de arriba-izquierda

b) El de arriba-derecha

c) El de abajo-izquierda

d) Ninguna de los anteriores

7. En un sumador/restador de 8-bits con A(7:0)=0x71 y B(7:0)=0x19, cuando se

suma A+B, el resultado O(7:0) y los bits carry (C) y overflow (V) son

a) O(7:0)=0x8A C=0 V=1 c) O(7:0)=0x81 C=1 V=0

b) O(7:0)=0x80 C=0 V=0 d) Ninguno de los anteriores

a) Sólo el de la izquierda b) Sólo el de la derecha

c) Cualquiera de los dos d) Ninguno de los dos 8. En un sumador/restador de 8-bits con A(7:0)=0x71y B(7:0)=0x19, cuando se

resta A-B, el resultado O(7:0) y los bits carry (C) y overflow (V) son

a) O(7:0)=0x56 C=0 V=1 c) O(7:0)=0x58 C=1 V=0

b) O(7:0)=0x57 C=1 V=1 d) Ninguno de los anteriores

9. El grafo de estados del siguiente circuito es (se representa en los estados el

orden Q2,Q1,Q0):

0 1

a o

1 X X

p S0/00 S1/10 S2/10 S3/01

FSM

clk 0

Q1 Q0

S0 0 0

rst S1 0 1

aa

state/o,p

state/o,p

S2 1 0

S3 1 1

J1 Q1

J Q

C1 K1 K JKFF C2 o

1

C

a) El izquierdo b) El central c) El derecho d) Ninguno

10. En el anterior circuito, la frecuencia máxima del reloj es:

J0 Q0

Parámetros temporales de los FF: tdelay-FF=0.5 ns tsetup-FF=0.5 ns thold-FF=0.5 ns J Q

C0 K0 p

Parámetros temporales las puertas lógicas: tdelay-NOT=1 ns tdelay-OR= tdelay-XOR =2 ns K JKFF

0

C3

C

a) 250 MHz c) 166.6 MHz

b) 200 MHz d) Ninguno de los anteriores

a clk rst

11. En el circuito anterior, se cambia la entrada S (Set) de los FFs por R

(Reset). El nuevo grafo de estados es: Figura 1 (arriba) FSM, grafo de estados y su codificación. Circuito síncrono

(abajo) con los circuitos combinacionales C0, C1, C2, C3

12. Las funciones lógicas de los circuitos C2 y C3 de la Figura 1 pueden ser:

a) o=/Q1+Q0 p=Q1+/Q0

b) o=/Q1+/Q0 p=/Q1*/Q0

c) o=Q1Q0 p=Q1*Q0

d) Ninguna de las anteriores

a) No cambia (es igual al anterior grafo de estados) 13. Las funciones lógicas del circuito C1 de la Figura 1 puede ser:

b) El izquierdo a) J1=Q1+a K1=/Q1+/a

c) El derecho b) J1=/Q0 K1=Q1*/a

d) Ninguna de las anteriores respuestas c) J1=Q1*/a K1=/Q0*a

d) Ninguna de las anteriores

14. Las funciones lógicas del circuito C0 de la Figura 1 puede ser:

a) J0=Q1+a K0=/Q1+/a

b) J0=/Q0 K0=Q1*/a

c) J0=Q1*/a K0=/Q0*a

d) Ninguna de las anteriores

15. La forma de onda (ideal) de Q1 y Q0 , para el circuito de la Figura 1, es:

Respuestas

DNI:____________

clk Cognoms:___________________________________Nom________________

rst

a b c d

a 1 X

2 X

3 X

(a) Q[1:0] 00 01 10 11 00 01 10 11 00

4 X

(b) Q[1:0] 00 01 10 11 00 01 10 11 5 X

6 X

(c) Q[1:0] 00 01 10 11 00 01 10 11 7 X

8 X

(d) Ninguna de las anteriores 9 X

10 X

16 La forma de onda (ideal) de o, para el circuito de la Figura 1, es: 11 X

12 X

13 X

clk 14 X

15 X

rst

16 X

a

(a) o

(b) o

(c) o

(d) Ninguna de las anteriores

También podría gustarte

- Test Lógica-Computadores-2015 PDFDocumento3 páginasTest Lógica-Computadores-2015 PDFPilar PilarAún no hay calificaciones

- A C B O: Fonaments de Computadors, 2021/22 Q2 (1a Convocatoria)Documento2 páginasA C B O: Fonaments de Computadors, 2021/22 Q2 (1a Convocatoria)Pilar PilarAún no hay calificaciones

- Geometric modeling in computer: Aided geometric designDe EverandGeometric modeling in computer: Aided geometric designAún no hay calificaciones

- Test Lógica-Computadores-2013 PDFDocumento2 páginasTest Lógica-Computadores-2013 PDFPilar PilarAún no hay calificaciones

- Fonaments de Computadors, 2022/23 Q2 (1a Convocatoria)Documento2 páginasFonaments de Computadors, 2022/23 Q2 (1a Convocatoria)Pilar PilarAún no hay calificaciones

- Test Lógica-Computadores-2012Documento3 páginasTest Lógica-Computadores-2012Pilar PilarAún no hay calificaciones

- Test Lógica-Computadores-2017 PDFDocumento1 páginaTest Lógica-Computadores-2017 PDFPilar PilarAún no hay calificaciones

- Algebra1819 Parcial3 SOLDocumento8 páginasAlgebra1819 Parcial3 SOLasashasaAún no hay calificaciones

- Lista 2 - Matemática para La Ciencia de DatosDocumento6 páginasLista 2 - Matemática para La Ciencia de DatosAdriana Zúñiga RomeroAún no hay calificaciones

- PreguntasDocumento4 páginasPreguntasFernando ParéAún no hay calificaciones

- Geometria Analitica 1 EjDocumento2 páginasGeometria Analitica 1 EjMasters AkademyAún no hay calificaciones

- Práctica #10 - LOGARITMOSDocumento3 páginasPráctica #10 - LOGARITMOSAlgebra Pre UniversitaAún no hay calificaciones

- MI Sep2015 TipoADocumento1 páginaMI Sep2015 TipoAmartak1207Aún no hay calificaciones

- Banco Por Áreas - Ciencias A - PRUEBA 2Documento10 páginasBanco Por Áreas - Ciencias A - PRUEBA 2renzo chirinos50% (2)

- 1 Unidades y VectoresDocumento2 páginas1 Unidades y VectoresGuille SanchezAún no hay calificaciones

- 04 - Algebra - Repaso San Marcos 2006 II - C2Documento5 páginas04 - Algebra - Repaso San Marcos 2006 II - C2Zoila Maria Alvino HuancaAún no hay calificaciones

- Examen de AdmicionDocumento9 páginasExamen de AdmicionMonse CastilloAún no hay calificaciones

- Concurso de Matemática Galois-NoetherDocumento5 páginasConcurso de Matemática Galois-NoetherVictor HenriqueAún no hay calificaciones

- ExamenOrdinario SolDocumento9 páginasExamenOrdinario SolJose FranciscoAún no hay calificaciones

- Cuestionario ResueltoDocumento7 páginasCuestionario ResueltoEdison JamiAún no hay calificaciones

- Banco Por Áreas - Ciencias B - PRUEBA 2Documento12 páginasBanco Por Áreas - Ciencias B - PRUEBA 2Jorge LimaAún no hay calificaciones

- Examen Trimestral (Academia Lideres)Documento4 páginasExamen Trimestral (Academia Lideres)EDU EDUARDO HUAMAN CUSIAún no hay calificaciones

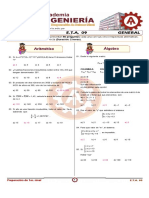

- E.T.A. 09 GeneralDocumento11 páginasE.T.A. 09 GeneralPaola PHAún no hay calificaciones

- Pre 2005 3Documento8 páginasPre 2005 3sting bacusoyAún no hay calificaciones

- Matematicas 4Documento4 páginasMatematicas 4Ruben AragonAún no hay calificaciones

- Actividad 8 Eduardo ValenciaDocumento7 páginasActividad 8 Eduardo ValenciaEduardo HerreraAún no hay calificaciones

- 1 L Umbreras: WWW Ich Edu - PeDocumento14 páginas1 L Umbreras: WWW Ich Edu - PeAnonymous 3NwLtd8hAún no hay calificaciones

- Trigonometria 3Documento2 páginasTrigonometria 3Capuñay Diaz Christian0% (1)

- Test2 - 2Documento2 páginasTest2 - 2albadoval1805Aún no hay calificaciones

- Algebra de BooleDocumento7 páginasAlgebra de BooleHeriberto ToledoAún no hay calificaciones

- 4761-Jma Ol-05-2017 - Web PDFDocumento24 páginas4761-Jma Ol-05-2017 - Web PDFgvhgvhvAún no hay calificaciones

- ExamenAlternativas Version2015Documento17 páginasExamenAlternativas Version2015Cris GuajardoAún no hay calificaciones

- Circunferenca TrigonométricaDocumento4 páginasCircunferenca TrigonométricaLUZ AMIRA NAVARRO HUARECCALLOAún no hay calificaciones

- Test Lógica-Computadores-2018 PDFDocumento2 páginasTest Lógica-Computadores-2018 PDFPilar PilarAún no hay calificaciones

- EVALUACION III CORTE CALCULO Ciclo VIDocumento2 páginasEVALUACION III CORTE CALCULO Ciclo VIOscar Andrés Vidal GamaAún no hay calificaciones

- Taller 02 ExpresionesDocumento5 páginasTaller 02 ExpresionesJuan Sebastian MayorgaAún no hay calificaciones

- Práctica #01 - Álgebra - Teoría de Exponentes en R PDFDocumento4 páginasPráctica #01 - Álgebra - Teoría de Exponentes en R PDFYoni Espinoza RiveraAún no hay calificaciones

- 1 Jornada OL MADocumento28 páginas1 Jornada OL MAcamilaAún no hay calificaciones

- CT 1Documento3 páginasCT 1RuyelMasgoCampos0% (1)

- Ejercicios de EconometriaDocumento8 páginasEjercicios de EconometriaYuri David Fernández0% (1)

- Cuadernillo-20220115 140515xozgDocumento4 páginasCuadernillo-20220115 140515xozgS Cristian ItoAún no hay calificaciones

- Práctica #03 - Álgebra - Binomio de NewtonDocumento4 páginasPráctica #03 - Álgebra - Binomio de NewtonAlgebra Pre UniversitaAún no hay calificaciones

- Exa. de Salida # (Matemática)Documento1 páginaExa. de Salida # (Matemática)nfnAún no hay calificaciones

- 2015 TDI - P1 RecDocumento3 páginas2015 TDI - P1 RecMagali GutierrezAún no hay calificaciones

- TG32 A02Documento2 páginasTG32 A02ederAún no hay calificaciones

- Semana 09 - Matematica IIDocumento4 páginasSemana 09 - Matematica IIElmo Jaime SALAS YAÑEZAún no hay calificaciones

- ALGEBRADocumento2 páginasALGEBRATotti Di Franchesco PelaezAún no hay calificaciones

- Repaso (Ficha 07) Ciencias 2021-II OkDocumento5 páginasRepaso (Ficha 07) Ciencias 2021-II OkDiego AymitumaAún no hay calificaciones

- SemanaDocumento6 páginasSemanaAlejandro ChambiAún no hay calificaciones

- Aritmetica 20 Numeros Racionales IIDocumento4 páginasAritmetica 20 Numeros Racionales IIDiego A. PérezAún no hay calificaciones

- EP - MB535 - 2005 - 2 - Solucionario - PDFDocumento6 páginasEP - MB535 - 2005 - 2 - Solucionario - PDFAnonymous 6ZVBcXy7nrAún no hay calificaciones

- Ensayo Paes Mate 1Documento21 páginasEnsayo Paes Mate 1Niko Drb100% (1)

- Curso de Electronica Digital - Trabajos Practicos 2 Al 6 (2022 1C)Documento37 páginasCurso de Electronica Digital - Trabajos Practicos 2 Al 6 (2022 1C)morena.2012.dpAún no hay calificaciones

- Dix 2Documento22 páginasDix 2ticsblancoAún no hay calificaciones

- Fisica 01-VectoresDocumento2 páginasFisica 01-VectoresEdward AndradeAún no hay calificaciones

- Exam 3Documento5 páginasExam 3MitzyAún no hay calificaciones

- Matemática 1 PDFDocumento35 páginasMatemática 1 PDFWilson Fernando Yaselga AuzAún no hay calificaciones

- Examen Fonaments de ComputadorsDocumento5 páginasExamen Fonaments de ComputadorsPilar PilarAún no hay calificaciones

- 2020 Parte2-V4Documento3 páginas2020 Parte2-V4Pilar PilarAún no hay calificaciones

- Test Lógica-Computadores-2016 PDFDocumento2 páginasTest Lógica-Computadores-2016 PDFPilar PilarAún no hay calificaciones

- Test Lógica-Computadores-2017 PDFDocumento1 páginaTest Lógica-Computadores-2017 PDFPilar PilarAún no hay calificaciones

- Test Lógica-Computadores-2018 PDFDocumento2 páginasTest Lógica-Computadores-2018 PDFPilar PilarAún no hay calificaciones

- 5-Regenerating Human Epithelia With Cultured Stem Cells 2018Documento12 páginas5-Regenerating Human Epithelia With Cultured Stem Cells 2018Pilar PilarAún no hay calificaciones

- Tema 2.1 Estructura AtómicaDocumento41 páginasTema 2.1 Estructura AtómicaPilar PilarAún no hay calificaciones

- 02 Rush - Samantha TowleDocumento215 páginas02 Rush - Samantha TowleVane LucioAún no hay calificaciones

- Un Amplificador Operacional EquilibradoDocumento5 páginasUn Amplificador Operacional Equilibradodeviluck19Aún no hay calificaciones

- Compuertas LogicasDocumento12 páginasCompuertas LogicasRuby Aracellys CorreaAún no hay calificaciones

- Sistema de Dados DidácticosDocumento4 páginasSistema de Dados Didácticosluismena09051982Aún no hay calificaciones

- Informe Previo 6 - Circuitos Digitales IDocumento9 páginasInforme Previo 6 - Circuitos Digitales IJames Lizonde PeredoAún no hay calificaciones

- Circuitos Integrados - Ppt.ppsDocumento29 páginasCircuitos Integrados - Ppt.ppstiburon53Aún no hay calificaciones

- Practica de Electronica IIDocumento4 páginasPractica de Electronica IIDIEGO ARMANDO COLQUE BAUTISTAAún no hay calificaciones

- 1184 Compuertas LogicasDocumento15 páginas1184 Compuertas LogicasOdilon JuarezAún no hay calificaciones

- Tema 3, Problemas Con Solución (IC, TSI)Documento69 páginasTema 3, Problemas Con Solución (IC, TSI)PabloAún no hay calificaciones

- Diseñe Un Amplificador Multietapa para Una Ganancia Total de 100. Puede UDocumento1 páginaDiseñe Un Amplificador Multietapa para Una Ganancia Total de 100. Puede UAlejandroAún no hay calificaciones

- 09 Moduladores y Transmisores de FM 2018Documento28 páginas09 Moduladores y Transmisores de FM 2018Gustavo CarraroAún no hay calificaciones

- Familias LogicasDocumento15 páginasFamilias LogicasAlonso Sanchez DominguezAún no hay calificaciones

- Deber Primer IntercicloDocumento20 páginasDeber Primer IntercicloMaria JoseAún no hay calificaciones

- Conversor DA Por Suma PonderadaDocumento3 páginasConversor DA Por Suma PonderadaShady EspinosaAún no hay calificaciones

- Chicaiza SimbañaC Suntaxi L3.1 8188Documento12 páginasChicaiza SimbañaC Suntaxi L3.1 8188CarliTos JavierAún no hay calificaciones

- Red RDocumento7 páginasRed RSergio Limck PlnckkAún no hay calificaciones

- Lab 07Documento5 páginasLab 07Juan CuervoAún no hay calificaciones

- TH ImpedanciaDocumento23 páginasTH ImpedanciaJuan CarreraAún no hay calificaciones

- Taller 1Documento3 páginasTaller 1LïïzMōnrôyVïïlläbon100% (1)

- Informe 3 Sistemas de ControlDocumento11 páginasInforme 3 Sistemas de ControlPablo Sandoval UrionaAún no hay calificaciones

- Universalidad NAND y NORDocumento8 páginasUniversalidad NAND y NOROmar Gallardo100% (1)

- Amplificadores Operacionales.Documento1 páginaAmplificadores Operacionales.Daniel MálagaAún no hay calificaciones

- LatexDocumento9 páginasLatexLaura FariñasAún no hay calificaciones

- Analisis de Circuitos Fase 2Documento12 páginasAnalisis de Circuitos Fase 2eduar gomezAún no hay calificaciones

- Lab 1 (Ad623-Ad620)Documento8 páginasLab 1 (Ad623-Ad620)Cristhian LeonAún no hay calificaciones

- Practica 3 - 1852552Documento3 páginasPractica 3 - 1852552Fermin AcostaAún no hay calificaciones

- Estudio Experimental Del Método de Los Potenciales de NodosDocumento5 páginasEstudio Experimental Del Método de Los Potenciales de NodosEdsn Samuel UrdayAún no hay calificaciones

- Controladores Logicos Programables PLC I - Actividad 1Documento7 páginasControladores Logicos Programables PLC I - Actividad 1Jhon DiazAún no hay calificaciones

- Solución: Ejercicio 13.24Documento3 páginasSolución: Ejercicio 13.24Shanella ChallcoAún no hay calificaciones

- Practica 3Documento9 páginasPractica 3Josfres KanayaAún no hay calificaciones

- Contadores Sincronos y AsíncronosDocumento30 páginasContadores Sincronos y AsíncronosChristian Ramírez Vargas50% (2)

- Clics contra la humanidad: Libertad y resistencia en la era de la distracción tecnológicaDe EverandClics contra la humanidad: Libertad y resistencia en la era de la distracción tecnológicaCalificación: 4.5 de 5 estrellas4.5/5 (117)

- Influencia. La psicología de la persuasiónDe EverandInfluencia. La psicología de la persuasiónCalificación: 4.5 de 5 estrellas4.5/5 (14)

- 7 tendencias digitales que cambiarán el mundoDe Everand7 tendencias digitales que cambiarán el mundoCalificación: 4.5 de 5 estrellas4.5/5 (87)

- Excel para principiantes: Aprenda a utilizar Excel 2016, incluyendo una introducción a fórmulas, funciones, gráficos, cuadros, macros, modelado, informes, estadísticas, Excel Power Query y másDe EverandExcel para principiantes: Aprenda a utilizar Excel 2016, incluyendo una introducción a fórmulas, funciones, gráficos, cuadros, macros, modelado, informes, estadísticas, Excel Power Query y másCalificación: 2.5 de 5 estrellas2.5/5 (3)

- Guía de cálculo y diseño de conductos para ventilación y climatizaciónDe EverandGuía de cálculo y diseño de conductos para ventilación y climatizaciónCalificación: 5 de 5 estrellas5/5 (1)

- UF2246 - Reparación de pequeños electrodomésticos y herramientas eléctricasDe EverandUF2246 - Reparación de pequeños electrodomésticos y herramientas eléctricasCalificación: 2.5 de 5 estrellas2.5/5 (3)

- EL PLAN DE MARKETING EN 4 PASOS. Estrategias y pasos clave para redactar un plan de marketing eficaz.De EverandEL PLAN DE MARKETING EN 4 PASOS. Estrategias y pasos clave para redactar un plan de marketing eficaz.Calificación: 4 de 5 estrellas4/5 (51)

- Excel y SQL de la mano: Trabajo con bases de datos en Excel de forma eficienteDe EverandExcel y SQL de la mano: Trabajo con bases de datos en Excel de forma eficienteCalificación: 1 de 5 estrellas1/5 (1)

- Guía para la crianza en un mundo digital: Cómo educar para un uso sano y seguro de la tecnologíaDe EverandGuía para la crianza en un mundo digital: Cómo educar para un uso sano y seguro de la tecnologíaCalificación: 3.5 de 5 estrellas3.5/5 (2)

- Mentalidades matemáticas: Cómo liberar el potencial de los estudiantes mediante las matemáticas creativas, mensajes inspiradores y una enseñanza innovadoraDe EverandMentalidades matemáticas: Cómo liberar el potencial de los estudiantes mediante las matemáticas creativas, mensajes inspiradores y una enseñanza innovadoraCalificación: 4.5 de 5 estrellas4.5/5 (5)

- Excel 2021 y 365 Paso a Paso: Paso a PasoDe EverandExcel 2021 y 365 Paso a Paso: Paso a PasoCalificación: 5 de 5 estrellas5/5 (12)

- Comunicaciones industriales y WinCCDe EverandComunicaciones industriales y WinCCCalificación: 5 de 5 estrellas5/5 (4)

- Todo Sobre Tecnología Blockchain: La Guía Definitiva Para Principiantes Sobre Monederos BlockchainDe EverandTodo Sobre Tecnología Blockchain: La Guía Definitiva Para Principiantes Sobre Monederos BlockchainAún no hay calificaciones

- Lógica de programación: Solucionario en pseudocódigo – Ejercicios resueltosDe EverandLógica de programación: Solucionario en pseudocódigo – Ejercicios resueltosCalificación: 3.5 de 5 estrellas3.5/5 (7)

- Didáctica de la matemática en la escuela primariaDe EverandDidáctica de la matemática en la escuela primariaCalificación: 2.5 de 5 estrellas2.5/5 (3)

- El Tao de la física: Una exploración de los paralelismos entre la física moderna y el misticismo orientalDe EverandEl Tao de la física: Una exploración de los paralelismos entre la física moderna y el misticismo orientalCalificación: 5 de 5 estrellas5/5 (3)

- Manual Técnico del Automóvil - Diccionario Ilustrado de las Nuevas TecnologíasDe EverandManual Técnico del Automóvil - Diccionario Ilustrado de las Nuevas TecnologíasCalificación: 4.5 de 5 estrellas4.5/5 (14)

- La psicología del trading de una forma sencilla: Cómo aplicar las estrategias psicológicas y las actitudes de los comerciantes ganadores para operar con éxito en línea.De EverandLa psicología del trading de una forma sencilla: Cómo aplicar las estrategias psicológicas y las actitudes de los comerciantes ganadores para operar con éxito en línea.Calificación: 4.5 de 5 estrellas4.5/5 (3)

- 100 circuitos de shields para arduino (español)De Everand100 circuitos de shields para arduino (español)Calificación: 3.5 de 5 estrellas3.5/5 (3)

- UF0349: ATENCIÓN AL CLIENTE EN EL PROCESO COMERCIAL (ADGG0208) (ADGD0308)De EverandUF0349: ATENCIÓN AL CLIENTE EN EL PROCESO COMERCIAL (ADGG0208) (ADGD0308)Calificación: 2 de 5 estrellas2/5 (1)

- LAS VELAS JAPONESAS DE UNA FORMA SENCILLA. La guía de introducción a las velas japonesas y a las estrategias de análisis técnico más eficaces.De EverandLAS VELAS JAPONESAS DE UNA FORMA SENCILLA. La guía de introducción a las velas japonesas y a las estrategias de análisis técnico más eficaces.Calificación: 4.5 de 5 estrellas4.5/5 (54)

- Inteligencia artificial: Análisis de datos e innovación para principiantesDe EverandInteligencia artificial: Análisis de datos e innovación para principiantesCalificación: 4 de 5 estrellas4/5 (3)

- El mito de la inteligencia artificial: Por qué las máquinas no pueden pensar como nosotros lo hacemosDe EverandEl mito de la inteligencia artificial: Por qué las máquinas no pueden pensar como nosotros lo hacemosCalificación: 5 de 5 estrellas5/5 (2)

- Estructura de Argumento: Secretos de los Mejores Debatientes del Mundo - Domine la Estructura de los ArgumentosDe EverandEstructura de Argumento: Secretos de los Mejores Debatientes del Mundo - Domine la Estructura de los ArgumentosCalificación: 4 de 5 estrellas4/5 (1)