Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Clase4 Regimen Protegido

Clase4 Regimen Protegido

Cargado por

Jhrs TaipeTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Clase4 Regimen Protegido

Clase4 Regimen Protegido

Cargado por

Jhrs TaipeCopyright:

Formatos disponibles

Universidad Nacional del Callao

Facultad de Ingeniería Industrial y de

Sistemas

Escuela Profesional de Ingeniería de Sistemas

Arquitectura y organización del

computador

Tema de la

clase:

Control de la

memoria en

régimen protegido

Mg. Msc. Ing. Sally Torres

sktorresa@unac.edu.pe

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Contenido

Control de la Memoria

Segmentación y Paginación

Modos de Direccionamiento de la

memoria

Región de Entrada y salida

Región de memoria reservada

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Control de la memoria

• El espacio de direccionamiento de un sistema

basado en un MP, se denomina memoria lógica o

memoria física.

• La estructura de la memoria lógica es diferente, en

casi todos los casos que la estructura de la

memoria física. La memoria lógica es el sistema de

memoria tal como lo ve el programador, mientras

que la memoria física, es la estructura real en el

hardware en el sistema de memoria.

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Control de la memoria

• El acceso a las direcciones de memoria de los MP

de la INTEL se realiza con 1 byte (8bits), una

palabra (16 bits) y doble palabra (32 bits) La

palabra se conserva en dos bytes vecinos. El byte

superior en la dirección superior; el byte inferior

en la dirección inferior.

• Complementando esta estructura básica de datos

el MP tiene otras 2 estructuras de memoria que

son la segmentación y la paginación.

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Distribución del Mapa de memoria

Lógica

MP Empieza Termina Memoria

Disponible

8086,8088, 80186 00000h FFFFFh 1 Mb

286, 386SX 000000h FFFFFFh 16 Mb

386DX, 486SX, 00000000h FFFFFFFFh 4 Gb

486DX

Figura 4.1 Mapa de la distribución lógica de la memoria RAM

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Modos de Direccionamiento de la Memoria

En el MP existen 3 diferentes modos de direccionamiento:

• Lógico

• Lineal

• Físico.

1.- La dirección lógica también conocida como virtual esta

formada por un selector y un desplazamiento.

2.- El dispositivo de segmentación transforma la región de

dirección lógica en 32 bits de región de dirección lineal.

3.- La dirección física es la dirección la cual aparece a la

salida del MP.

10000h 1FFFFH 10FFEFh

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Modos de Direccionamiento de la Memoria

Organización paginada.-

Es un recurso complementario de control de la

memoria. El cual actúa solo en régimen protegido.

La paginación permite controlar un gran segmento

en el MP. La organización paginada trabaja bajo el

control de la organización segmentada .El dispositivo

de paginación transforma la dirección lineal del

Régimen Protegido la cual se obtuvo del dispositivo

de segmentación en dirección física.

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Región de entrada y salida

• los Dispositivos externos están distribuidos en la memoria

y en una determinada región de E/S. Aunque el MP

soporta este direccionamiento la entrada y salida se

encuentra en otra región.

• Para la región de entrada y salida se da 64Kb los cuales

pueden ser divididos en 64 puertos de 8 bits c/u; 32

puertos de 16 bits c/u ó 16 puertos de 32 bits c/u. Estos

puertos son accesibles mediante las instrucciones de E/S

IN y OUT mas la dirección del puerto.

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Región de memoria reservada

• La región de inicialización del Sistema (BIOS) , que se

encuentra en las direcciones FFFFFFF0h hasta FFFFFFFFh

(640Kb hasta 1Mb).

• La región de la tabla de vectores de interrupción , que se

encuentra en las direcciones 000h hasta 3FFh (primeros

1024b=1Kb).

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

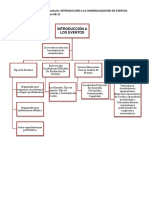

Régimen protegido en los

Microprocesadores

Control de la memoria en Régimen

protegido

Conversión de Paginas

Dirección Lineal

Tabla de Paginas

Elementos de la Tabla de paginas

Memoria Cache de Conversión de

paginas

Tratamiento de la excepción falta

de pagina

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Introducción

En el régimen protegido los medios de control de la

memoria de los MP permiten al SO aislar las tareas unas de

otras y de esta manera evitar la influencia entre las tareas y

el SO. Además permiten ejecutar los programas en

diferentes lugares de memoria. De este modo el SO optimiza

la utilización de la memoria mediante el desplazamiento de

las tareas.

Básicamente durante el control de la memoria se realiza la

transformación de direcciones, utilizados por los programas

en direcciones físicas. El direccionamiento de la memoria en

modo protegido permite al MP acceder a los datos y

programas ubicados arriba del primer Mbyte de memoria.

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Introducción

La diferencia entre los dos modos radica en el

cálculo de la dirección inicial del segmento.

En modo protegido el selector se utiliza para

especificar un índice en una tabla definida por el

sistema operativo. La tabla contiene la dirección

base de un segmento dado. La dirección física se

obtiene sumando la dirección base hallada en la

tabla con el offset.

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Control de la memoria en Regimen

Protegido

En el proceso de Transformación de direcciones el MP utiliza

las siguientes estructuras de datos:

• Descriptores

• Tabla de Descriptores (GDT, LDT, IDT)

• Selectores

• Registros de Segmentos

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Transformación de direcciones

Dirección

Selector Desplazamiento

Lógica

Transformación del

segmento

Esta permitido la

paginación

CRO=1

Dirección

Catalogo Página Desplazamiento

Lineal

Transformación de

Páginas

Dirección Física

Figura 4.3 Transformación de direcciones en régimen protegido

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Transformación de Segmentos

15 0 31 0

Dirección

Selector Desplazamiento

Lógica

Descriptor del

segmento +

Dirección

Catalogo Página Desplazamiento

Lineal

Figura 4.4 Transformación de segmentos en régimen protegido

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Transformación de Paginas

Dirección

Catalogo Página Desplazamiento

Lineal

Elemento del Elemento de la Memoria

catálolog tabla de página Fisica

CR3

Figura 4.5 Transformación de paginas en régimen protegido

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Elementos de la Tabla de Paginas

P- Bandera de Existencia.

R/W - Bandera de lectura/escritura

U/S - Bandera de Usuario/ Supervisor

A - Bandera de acceso.

D - Bandera de desperdicio.

AVAIL - Bandera, Accesible solo a los programadores del

Sistema.

O - Reservado para la Intel, No se utiliza.

31 12 11 0

Dirección página AVAIL 00 D A 00 U/S R/W P

Figura 4.2 Elementos de la tabla de paginas

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Memoria cache de conversión de paginas

También se le conoce como "Buffer de traducciones

anticipadas (TLB). Para aumentar la Potencia

durante la transformación de direcciones el MP

conserva las direcciones de la tabla de paginas

mas utilizadas en la memoria cache, esto

específicamente en los descriptores soportados

en el TLB serán los que contienen las direcciones

de las paginas que más reciente hayan sido

referenciadas.

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Memoria cache de conversión de paginas

Además del descriptor de página, cada entrada del TLB

consta de un campo de búsqueda que contiene el número

de página al que corresponde el descriptor y de un bit d

validación (V), que indica si la información que contiene

dicha entrada es válida o no. El bit V de la TLB tiene un

significado análogo al del bit P de la tabla de página.

Si la información de la tabla de paginas necesaria no se

encuentra en la memoria cache de conversión de paginas,

entonces es necesario acceder a los 2 niveles de tablas

(catalogo y pagina).

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Memoria cache de conversión de paginas

• Si no se encuentra ninguna entrada libre en el TLB (bit

V=0) sera necesario expulsar algunos descriptores ; por

ejemplo aquel que más tiempo lleva sin haber sido

referenciado.

• La memoria cache solo es accesible a los programas del

Sistema Operativo mas no a los programas de aplicación.

Los Programas del Sistema Operativo cada vez que

cambian las tablas de paginas tienen que cambiar la

memoria.

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Memoria cache de conversión de paginas

La memoria cache de transformación de paginas

puede ser desconectada mediante 2 métodos:

• Cargando el Registro CR3 con ayuda de la

instrucción MOV por ejemplo: MOV CR3 , EAX

• Conectando hacia otra tarea, la cual tiene un

contenido diferente del registro CR3.

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

organigrama de un sistema de control

de memoria virtual con TLB para los

siguientes casos:

• Cuando el descriptor se encuentra en el TLB.

• Cuando el descriptor no se encuentra en el TLB pero la

página esta en la memoria Principal.

• Cuando el descriptor de página no se encuentra ni en TLB

y la página no esta en memoria principal.

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Tratamiento de la excepción falta de

pagina

• Reconocer la excepción falta de página, si la página

referenciada no está presente en memoria principal.

• Abortar la ejecución de la instrucción en curso y guardar

el estado de la maquina para recuperarlo posteriormente.

• Saltar a la rutina del SO que trata la excepción falta de

página, la cual se encarga de transferir la página desde la

TLB la memoria principal.

• Restaurar el estado (guardado anteriormente) del proceso

interrumpido y proseguir su ejecución como si nada

hubiera ocurrido.

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Un proceso realiza un Inicio

Figura 4.6 acceso a memoria

Sistema de CPU accede a MMU

control de Descriptor en TLB

si

no

memoria con Acceso a la TP en

busca del descriptor

TLB no

Pag. cargada en MP

si

Rutina de tratamiento de la Actualizar TLB Formar dir. real

excepción falta de pagina

El SO suspende al

proceso

Se activa el Hw de E/S

se realiza la

transferencia disco- MP

no

Hay TPI libre

si Aplicar algoritmo de

sustitución

El SO actualiza la TP

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

Figura 4.6 Sistema de control

de memoria con TLB

Arquitectura y Organización de la PC FIIS-UNAC Mg. Msc. Sally Torres

También podría gustarte

- Base de Datos MatriculaDocumento10 páginasBase de Datos MatriculaMery Love50% (2)

- Calificación Paso A Paso Del Soldador D1.1 SMAW 3GDocumento16 páginasCalificación Paso A Paso Del Soldador D1.1 SMAW 3GAvelino Santiago86% (36)

- Clase3Regimenes de Trabajo Del MPDocumento18 páginasClase3Regimenes de Trabajo Del MPJhrs TaipeAún no hay calificaciones

- Clase1 - EvolucionPC - Arquitecturas de ComputadorasDocumento28 páginasClase1 - EvolucionPC - Arquitecturas de ComputadorasJhrs TaipeAún no hay calificaciones

- Laboratorio1Documento4 páginasLaboratorio1Jhrs TaipeAún no hay calificaciones

- Clase 7 - CuartanormalDocumento30 páginasClase 7 - CuartanormalJhrs TaipeAún no hay calificaciones

- TMD2Documento54 páginasTMD2Jhrs TaipeAún no hay calificaciones

- Pru9 - DMLiudDocumento8 páginasPru9 - DMLiudJhrs TaipeAún no hay calificaciones

- Base de DatossssDocumento10 páginasBase de DatossssJhrs TaipeAún no hay calificaciones

- Pru10 - DMLselectDocumento11 páginasPru10 - DMLselectJhrs TaipeAún no hay calificaciones

- Clase 1Documento5 páginasClase 1Jhrs TaipeAún no hay calificaciones

- Ficha Inversor Must 3000W 24V MPPT50Documento1 páginaFicha Inversor Must 3000W 24V MPPT50HARLEY DAVIDSON ARCINIEGAS ARIASAún no hay calificaciones

- Introducción A Los EventosDocumento2 páginasIntroducción A Los EventosLuisa LópezAún no hay calificaciones

- 16 (PS-CT-16) Puente Grúa y Pórtico de Viga Simple o Múltiple Con Carro ElevadoDocumento9 páginas16 (PS-CT-16) Puente Grúa y Pórtico de Viga Simple o Múltiple Con Carro ElevadoGial TidiAún no hay calificaciones

- Temario PRLDocumento145 páginasTemario PRLRafael Perez RodriguezAún no hay calificaciones

- Finanzas CorporativasDocumento4 páginasFinanzas CorporativasClaudia SolanoAún no hay calificaciones

- Guia Reclamos PDFDocumento7 páginasGuia Reclamos PDFLuis JoseAún no hay calificaciones

- Tarea 3 Cultura OrganizacionalDocumento3 páginasTarea 3 Cultura OrganizacionalDaniela Zavala50% (2)

- 222-03 Parámetros Visibilidad-1Documento18 páginas222-03 Parámetros Visibilidad-1JavierAún no hay calificaciones

- Gobernabilidad JAVIERDocumento16 páginasGobernabilidad JAVIERJavierJoseVidurrizagaParedesAún no hay calificaciones

- Cronograma de Novedades AbrilDocumento1 páginaCronograma de Novedades AbrilValentin Duque PerezAún no hay calificaciones

- Unidad 1Documento20 páginasUnidad 1Oscar LlecaAún no hay calificaciones

- Agrupación de Un Conjunto de Empleados Apartir de Sus Caracteristicas Segun El Analisis ClusterDocumento4 páginasAgrupación de Un Conjunto de Empleados Apartir de Sus Caracteristicas Segun El Analisis ClusterDani MonteAún no hay calificaciones

- Análisis de Objeto Técnico: El CPUDocumento11 páginasAnálisis de Objeto Técnico: El CPUIng. Gerardo Sánchez Nájera95% (43)

- NTC3774 (Ingeniería Civil y Arquitectura. Práctica Estándar para La Inspección Petrográfica Del Concreto Endurecido)Documento31 páginasNTC3774 (Ingeniería Civil y Arquitectura. Práctica Estándar para La Inspección Petrográfica Del Concreto Endurecido)Sergio Alejandro Suarez GallegoAún no hay calificaciones

- Avance de ProyectoDocumento15 páginasAvance de Proyectojazmin Ccapa saicoAún no hay calificaciones

- Composicion Poblacional en MexicoDocumento6 páginasComposicion Poblacional en MexicoJaviier Saavedra100% (8)

- Excel Avanzado NotasDocumento9 páginasExcel Avanzado NotasKevin Allan Blanco JarquinAún no hay calificaciones

- Instrumentos de Medicion de Movimientos SismicosDocumento11 páginasInstrumentos de Medicion de Movimientos SismicosgyaytuAún no hay calificaciones

- Plan para La Vigilancia Prevencion y Control de Covid-19 en Minera Yanacocha Sin Lista v.08Documento57 páginasPlan para La Vigilancia Prevencion y Control de Covid-19 en Minera Yanacocha Sin Lista v.08benedicto soto mestanzaAún no hay calificaciones

- ShellT Ellus TDocumento2 páginasShellT Ellus TDaniel MauricioAún no hay calificaciones

- Practica Cofasa - Activo Pasivo Capital ResultadosDocumento323 páginasPractica Cofasa - Activo Pasivo Capital ResultadosEdson Luna BalderasAún no hay calificaciones

- Cuáles Son Los Efectos Positivos y Negativos de La Revolución IndustrialDocumento1 páginaCuáles Son Los Efectos Positivos y Negativos de La Revolución IndustrialDanny Cuyuch AcabalAún no hay calificaciones

- Métodos de Programación de ObraDocumento25 páginasMétodos de Programación de ObraCatalina MENDOZA BERNALAún no hay calificaciones

- PLANIFICACIÓN MICROCURRICULAR 8voDocumento8 páginasPLANIFICACIÓN MICROCURRICULAR 8voMagdalena CastroAún no hay calificaciones

- Fuentes y UsosDocumento5 páginasFuentes y UsosLixon Rios100% (1)

- Libro MVC Con JavaDocumento384 páginasLibro MVC Con JavaGeov@Aún no hay calificaciones

- Agenda ActualDocumento22 páginasAgenda ActualFedericoPereyraAún no hay calificaciones

- Informe Técnico ITVDocumento11 páginasInforme Técnico ITVDarío Fernández FernándezAún no hay calificaciones

- Medicion Del BlockDocumento4 páginasMedicion Del BlockFrida Mercedes Maccapa Sellerico100% (1)