Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Famlias Lógicas

Cargado por

angelDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Famlias Lógicas

Cargado por

angelCopyright:

Formatos disponibles

1

Familias Lógicas

Angel D. Lema

Resumen—Todo diseñador de electrónica digital se ha Casi inmediatamente aparecieron otras familias lógicas

hecho alguna vez la pregunta ¿qué tecnología digital será basadas en transistores bipolares conmutando entre corte y

la más apropiada para este diseño? En una primera saturación a fin de reproducir dentro de un chip los circuitos

aproximación, es fácil elegir entre tecnología TTL o que hasta ese momento se realizaban utilizando

CMOS simplemente basándonos en el consumo que componentes discretos. La primera de estas familias fue

pretendamos que tenga el diseño; pero a partir de ahí es implementada con resistencias y transistores bipolares y se

donde empiezan los problemas: actualmente existen la identifica como lógica RTL (Resistor Transistor

fundamentalmente seis subfamilias TTL y cuatro CMOS, Logic).

cada una de ellas con unas características diferentes que

las hacen propicias para cada tipo de aplicación. La integración de resistencias demanda gran cantidad de área

de silicio, reduciendo la cantidad de compuertas que se

podían incluir dentro de un mismo chip. Para mejorar el

A la vista de esto podemos llegar a la conclusión de que es

aprovechamiento del área algunas resistencias de los

imprescindible para el diseñador conocer a fondo cada

circuitos comenzaron a ser reemplazadas por diodos,

una de estas tecnologías, entendiendo por esto no sólo sus

principalmente en las etapas de entrada, dando lugar a la

características funcionales sino también el porqué de las

aparición de la lógica de diodos y transistores identificada

mismas. como DTL (Diode Transistor Logic). Finalmente, los

transistores multiemisor reemplazaron los diodos y se llegó a

Veremos cómo los fabricantes, al desarrollar una nueva una topología circuital que dio lugar a una familia lógica

tecnología, han perseguido la reducción del parámetro basada fundamentalmente en transistores bipolares y una

"producto potencia disipada retardo de propagación" mínima cantidad de resistencias. Esta familia, denominada

que, como veremos, determina la calidad de la familia lógica TTL (Transistor Transistor Logic), se popularizó

lógica; además, se han ido mejorando otras rápidamente y mantiene, aún en la actualidad, su vigencia.

características.

I. INTRODUCCIÓN

E s un grupo de circuitos integrados digitales monolíticos,

construidos de compuertas lógicas usando diseños

diferentes, usualmente con niveles lógicos compatibles y

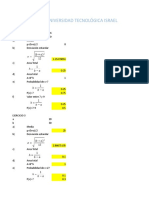

características de fuente de poder dentro de una familia. Fig. 1. Familias lógicas

Muchas familias lógicas son producidas como componentes

individuales, cada uno conteniendo una o algunas funciones Con el correr del tiempo la familia TTL se convirtió en un

básicas relacionadas, las cuales podrían ser utilizadas como conjunto de familias lógicas que si bien entre sí difieren en

bloques para crear sistemas para interconectar circuitos velocidad, consumo de energía y costo, mantienen

integrados más complejos. Como consecuencia de la características de entrada y salida compatibles de manera

estandarización, la interconexión entre dispositivos lógicos que en un sistema digital pueden mezclarse componentes de

de una misma familia es particularmente sencilla y directa: distintas familias TTL. Los principales inconvenientes de los

no requiere de etapas adicionales de acoplamiento. circuitos con transistores bipolares son el alto consumo y,

como consecuencia, la baja escala de integración admisible

Como consecuencia de la estandarización, la interconexión (cantidad de dispositivos posibles de integrar en un mismo

entre dispositivos lógicos de una misma familia es chip) que se relaciona directamente con una baja

particularmente sencilla y directa: no requiere de etapas complejidad del circuito.

adicionales de acoplamiento.

Como alternativa para soslayar estos inconvenientes y

La primera familia lógica en aparecer en el mercado, a facilitar el aumento del nivel de integración surgieron las

principios de la década del 60, fue implementada con lógica familias basadas en transistores de efecto de campo de

de transistores bipolares acoplados por emisor (ECL, compuerta aislada (MOS, metal oxide semiconductor) de

Emitter Coupled Logic). A fin de desarrollar circuitos de enriquecimiento. En esta tecnología, los circuitos lógicos

alta velocidad los transistores conducen en zona activa y de pueden ser implementados íntegramente con transistores

esta manera se minimiza el tiempo de conmutación entre MOS evitando la presencia de resistencias, en consecuencia,

conducción y corte. para implementar.

II.CARACTERÍSTICAS DE LAS FAMLIAS LÓGICAS La familia TTL o bipolar se divide en las siguientes

categorías o subfamilias básicas:

Las características más importantes de un circuito digital

son: su velocidad, su consumo de potencia, su inmunidad al

ruido y su confiabilidad.

La velocidad mide la rapidez de respuesta de las salidas de

un circuito digital a cualquier cambio en sus entradas.

El consumo de potencia mide la cantidad de corriente o de

potencia que consume un circuito digital en operación.

La inmunidad al ruido mide la sensibilidad de un circuito

digital al ruido electromagnético ambiental.

La confiablidad mide el período útil de servicio de un

circuito digital. Fig. 2. Esquema TTL

FAMLIA LÓGICA TTL. La familia TTL tuvo su origen en

los estudios de Sylvania, pero fue Texas Instruments quien la TTL estándar.

insertó en el mercado con la fabricación de la serie 74xx, de

TTL Schottky (S).

mayor velocidad y mejor relación señal-ruido,

convirtiéndose esta serie en el estándar de la familia. Aunque TTL de baja potencia (L).

estos componentes actualmente son utilizados, su mayor TTL Schottky de baja potencia (LS).

empleo ocurrió en las décadas de 1960 y 1970. TTL de alta velocidad (H).

TTL Schottky avanzada (AS).

La familia original 74XX ya obsoleta dio lugar a varias TTL Schottky de baja potencia avanzada (ALS).

subfamilias, buscando mejoras en el funcionamiento y

compatibilidad con otros componentes.

Tensión de alimentación (+ VCC). Los circuitos TTL en

A qué subfamilia pertenece el componente, se indica en el general, pueden operar con tensiones entre 4.75 V. y 5.25 V.

centro de su nombre con una o varias letras después del Pero el valor nominal de la tensión de trabajo es de + 5

número 74/54. Ejemplo 74LS00. volts.

El significado completo del nombre de los componentes Niveles de voltaje.

pertenecientes a la serie 74xx es el siguiente:

De 0 V. a 0.8 V. para el estado bajo.

Prefijo. SN, HD, MM, DM, indican el fabricante, Texas De 2.4 V. A 5 V. para el estado alto.

Instruments, Motorola, ON Semiconductor, Hitachi

Semiconductor, Fairchild Semiconductor, Renesas, etc. FAMLIA LÓGICA ECL. La familia ECL, Lógica Acoplada

en Emisor (emmiter-coupled logic) son unos circuitos

El número 74/54, indica que es de uso comercial para el 74 y integrados digitales los cuales usan transistores bipolares,

de diseño militar para 54. La diferencia radica en la pero a diferencia de los TTL en los ECL se evita la

temperatura de trabajo y en los niveles mínimo y máximo de saturación de los transistores, esto da lugar a un incremento

la tensión de alimentación 5 volts típica. en la velocidad total de conmutación.

Las letras que siguen al número 74/54 indican la subfamilia,

L, H, S, LS, AS, ALS, F. La familia ECL opera bajo el principio de la conmutación de

corriente, por el cual una corriente de polarización fija

El número después de las letras de la subfamilia, indica el menor que la corriente del colector de saturación es

componente en sí (inversores, compuertas, contadores, conmutada del colector de un transistor al otro. Este tipo de

registros, etc.). configuraciones se les conoce también como la lógica de

modo de corriente (CML; current-mode logic).

Si dos o más subfamilias tienen componentes con el mismo

número significa que la función del componente es la misma. El funcionamiento de los circuitos ECL se basa en el mismo

El sufijo (últimas letras) de tenerlo indica el encapsulado del amplificador diferencial. Los transistores no se saturan,

(P,J,N,D). la operación normal es en zona activa, lo que constituye una

de las razones que hace que estos circuitos sean los mas

La familia lógica TTL es la más común de todas las familias veloces de los circuitos integrados digitales.

lógicas. Los circuitos integrados TTL implementan su lógica

interna, exclusivamente basándose en transistores NPN y Tensión de alimentación: 5 V típica, con rango entre los

PNP, diodos y resistencias. 4,75V y los 5,25V para la 74 y 4,5 V a 5,5 V para la 54.

La familia TTL está disponible en dos versiones: la serie 54 Lógica positiva: el “1”lógico es de mayor tensión que el “0”

y la serie 74. La primera se destina a aplicaciones militares y lógico.

la segunda a aplicaciones industriales y de propósito general. Rango de temperatura: de 0 °C a 70 °C para la serie 74 y de

-55º a 125 °C para la 54.

Niveles de tensión de entrada para el “0” lógico (VIL): entre señales, cada entrada CMOS representa comúnmente una

0V y 0,8V. carga a tierra de 5 pF. Debido a su capacitancia de entrada

Niveles de tensión de entrada para el “1” lógico (VIH): entre se limita el número de entradas CMOS que se pueden

2,4V y VCC manejar con una sola salida CMOS.

Velocidad de transmisión entre los estados lógicos: alrededor

de 400 Mhz. Así pues, el factor de carga de CMOS depende del máximo

retardo permisible en la propagación. Comúnmente este

factor de carga es de 50 para bajas frecuencias (<1 MHz).

Por supuesto para altas frecuencias, el factor de carga

disminuye. La salida CMOS tiene que cargar y descargar la

combinación en paralelo de cada capacitancia de entrada, de

manera que el tiempo de conmutación de salida aumente en

proporción al número de cargas conducidas, cada carga

CMOS aumenta el retardo en la conducción de la

propagación del circuito por 3 ns. Así podemos llegar a la

Fig. 3. Niveles de la famlia ECL

conclusión de que el factor de carga de CMOS depende del

La configuración de una ECL Está basada en el máximo retardo permisible en la propagación.

amplificador diferencial, denominado así porque su salida es

proporcional a la diferencia entre dos tensiones de entrada Velocidad de conmutación. Los CMOS, al igual que N-

V1 y V2. Este circuito se utiliza principalmente en sistemas MOS y P-MOS, tiene que conducir capacitancias de carga

analógicos, pero también tiene propiedades digitales, relativamente grandes, su velocidad de conmutación es más

llegando a ser la base de construcción de la lógica de emisor rápida debido a su baja resistencia de salida en cada estado.

acoplado o ECL (en algunos casos nos la podemos encontrar Recordemos que una salida N-MOS tiene que cargar la

como lógica de modo corriente o CML), como lo muestra el capacitancia de carga a través de una resistencia

circuito. relativamente grande (100 k Ω).

Al aumentar el número de entradas, es necesario poner dos En el circuito CMOS, la resistencia de salida en el estado

seguidores de emisor para igualar niveles de tensión de ALTO es el valor RON del P-MOSFET, el cual es

entrada y salida. generalmente de 1 k Ω o menor. Esto permite una carga más

rápida de la capacitancia de carga. Los valores de velocidad

Si V1 es igual que V2 se tendrá que, por simetría del de conmutación dependen del voltaje de alimentación que se

circuito, las corrientes de los transistores son iguales. Sin emplee, por ejemplo en una a compuerta NAND de la serie

embargo, si V1 sobrepasa a V2 en aproximadamente 0,1 4000 el tiempo de propagación es de 50 ns para VDD = 5 V

voltio, el transistor T1 estará en conducción y T2 en corte; e y 25ns para VDD = 10 V. Como podemos ver, mientras

inversamente, si V1 es menor que V2 en 0,1 voltio, entonces VDD sea mayor podemos operar en frecuencias más

T2 conducirá y T1 estará en corte. elevadas.

Por supuesto, mientras más grande sea VDD se producirá

La corriente de emisor se mantiene prácticamente constante, una mayor disipación de potencia. Una compuerta NAND

y se transfiere o conmuta del transistor T1 al T2 cuando la de las series 74HC o 7411CT tiene un tpd promedio

tensión V1 varía desde 0,1 V, por encima de la tensión de alrededor de 8 ns cuando funciona con un VDD = 5V. Esta

referencia V2, hasta 0,1 voltios por debajo de esta tensión. velocidad es comparable con la de la serie 74LS.

Excepto dentro de un margen muy estrecho de variación de

la tensión de entrada V1, a la salida S sólo puede tener uno

de dos posibles valores y, por tanto, actúa como circuito

digital.

FAMLIA LÓGICA CMOS. (Complementary Metal-Oxide

Semiconductor), el término complementario se refiere a la

utilización de dos tipos de transistores en el circuito de

salida, en una configuración similar a la tótem-pole de la

familia TTL.

Se usan conjuntamente MOSFET (MOS Field-Effect

transistor, transistor de efecto campo MOS) de canal n

(NMOS) y de canal p (PMOS ) en el mismo circuito, para Fig. 4. Esquema CMOS

obtener varias ventajas sobre las familias P-MOS y N-MOS.

La tecnología CMOS es ahora la dominante debido a que es Niveles lógicos y margen de ruido

más rápida y consume aún menos potencia que las otras Parámetros característicos

familias MOS. Estas ventajas son opacadas un poco por la VOHmh: Es la tensión de salida mínima que se garantiza en

elevada complejidad del proceso de fabricación del CI y una nivel alto.

menor densidad de integración. De este modo, los CMOS VIHmh: Es la mínima tensión de entrada que se garantiza

todavía no pueden competir con MOS en aplicaciones que será reconocida como nivel alto.

requieren lo último en LSI. VOLmax: Es la tensión de salida máxima que se garantiza

en nivel bajo.

Factor de carga. Al igual que N-MOS y P-MOS, los CMOS VILmax: Es la máxima tensión de entrada que se garantiza

tienen una resistencia de entrada extremadamente grande será reconocida como nivel bajo.

(10*12Ω) que casi no consume corriente de la fuente de

REFERENCIAS

[1] Wakerly, John F. Diseño digital: principios y prácticas. Pearson

educación, 2001.

[2] Viejo, Cecilio Blanco. Fundamentos de electrónica digital. Editorial

Paraninfo, 2005.

[3] Tocci, Ronald J., and Neal S. Widmer. Sistemas digitales: principios y

aplicaciones. Pearson Educación, 2003.

[4] Sanchis, Enrique. Sistemas electrónicos digitales: Fundamentos y diseño

de aplicaciones. Vol. 61. Universitat de València, 2002.

[5] Santamaría, Eduardo. Electrónica digital y microprocesadores. Vol. 4.

Univ Pontifica Comillas, 1993.

4

También podría gustarte

- Acceso Multiple Por Division de Espacio Una Nueva DimensionDocumento6 páginasAcceso Multiple Por Division de Espacio Una Nueva DimensionangelAún no hay calificaciones

- Subtema 2 CsDocumento24 páginasSubtema 2 CsangelAún no hay calificaciones

- Tarea 8Documento8 páginasTarea 8angelAún no hay calificaciones

- Descativar La Busqueda DNSDocumento1 páginaDescativar La Busqueda DNSangelAún no hay calificaciones

- Tesis de DesvanecimientoDocumento187 páginasTesis de Desvanecimientoing_rogercc4528Aún no hay calificaciones

- TAREA10Documento8 páginasTAREA10angelAún no hay calificaciones

- TAREA10Documento8 páginasTAREA10angelAún no hay calificaciones

- Propagación y Antenas Organizador GráficoDocumento2 páginasPropagación y Antenas Organizador GráficoangelAún no hay calificaciones

- TAREA15Documento8 páginasTAREA15angelAún no hay calificaciones

- Tarea 14Documento5 páginasTarea 14angelAún no hay calificaciones

- Tarea 1Documento4 páginasTarea 1angelAún no hay calificaciones

- Tarea 7Documento7 páginasTarea 7angelAún no hay calificaciones

- Tarea 1 Vectores, EscalaresDocumento5 páginasTarea 1 Vectores, EscalaresangelAún no hay calificaciones

- Tarea 3 Diferenciación VectorialDocumento5 páginasTarea 3 Diferenciación VectorialangelAún no hay calificaciones

- Tare1 PeriodicidadDocumento11 páginasTare1 PeriodicidadangelAún no hay calificaciones

- Tare1 Periodicidad PDFDocumento11 páginasTare1 Periodicidad PDFangelAún no hay calificaciones

- Semana 13 ActividadDocumento1 páginaSemana 13 ActividadangelAún no hay calificaciones

- Tare1 Periodicidad PDFDocumento11 páginasTare1 Periodicidad PDFangelAún no hay calificaciones

- Tarea 1 Múltiplos y SubmúltiplosDocumento1 páginaTarea 1 Múltiplos y SubmúltiplosMAGIC STARTAún no hay calificaciones

- Lab 5.1Documento4 páginasLab 5.1Lennin Manchego CastroAún no hay calificaciones

- Karla Lema .FinDocumento2 páginasKarla Lema .FinangelAún no hay calificaciones

- 5.3.1.3 Packet Tracer - Identify MAC and IP AddressesDocumento3 páginas5.3.1.3 Packet Tracer - Identify MAC and IP AddressesangelAún no hay calificaciones

- Ejercicios de Teoría de ColasDocumento3 páginasEjercicios de Teoría de Colasangel0% (2)

- Tarea 10Documento11 páginasTarea 10angelAún no hay calificaciones

- Registro de desplazamiento 4 bitsDocumento1 páginaRegistro de desplazamiento 4 bitsangelAún no hay calificaciones

- Teoria de Algebra de Boole PDFDocumento25 páginasTeoria de Algebra de Boole PDFsilvercachAún no hay calificaciones

- Prueba FinalDocumento11 páginasPrueba FinalangelAún no hay calificaciones

- Amplificación BJT con divisor de voltajeDocumento9 páginasAmplificación BJT con divisor de voltajeangelAún no hay calificaciones

- Observaciones de Carnetización-Enviadas A Quito 30-12-2018Documento1 páginaObservaciones de Carnetización-Enviadas A Quito 30-12-2018angelAún no hay calificaciones

- Tarea de MecanografiaDocumento9 páginasTarea de MecanografiaKaren CastilloAún no hay calificaciones

- EG-1091-Mayta Patzi, Wilfredo WilsonDocumento102 páginasEG-1091-Mayta Patzi, Wilfredo Wilsonluis exalto quispe sanchezAún no hay calificaciones

- Regulaores VRMDocumento14 páginasRegulaores VRMxrazor0Aún no hay calificaciones

- Proyecto 555Documento2 páginasProyecto 555NaLLyd SS.Aún no hay calificaciones

- Proceso de Fabricación de NWELL CMOS (RESUMEN)Documento1 páginaProceso de Fabricación de NWELL CMOS (RESUMEN)Pamela KarenAún no hay calificaciones

- Informe de Compuertas LógicasDocumento18 páginasInforme de Compuertas LógicasguinimaAún no hay calificaciones

- Historia de La ComputadoraDocumento2 páginasHistoria de La ComputadoraKevin GarciaAún no hay calificaciones

- Geopolítica de Los Chips - El DiplóDocumento10 páginasGeopolítica de Los Chips - El Diplódaniel negrelliAún no hay calificaciones

- PMSD-322 - CUADERNO DE INFORMES Reparacion Tablet LaptopDocumento18 páginasPMSD-322 - CUADERNO DE INFORMES Reparacion Tablet Laptopmario TylesAún no hay calificaciones

- Pre-Informe Digitales 1 Practica1Documento7 páginasPre-Informe Digitales 1 Practica1Jhonatan Prieto GuazaquilloAún no hay calificaciones

- Proyecto de La Guarderia ArregladoDocumento17 páginasProyecto de La Guarderia ArregladoMaria Virginia Sierralta100% (2)

- InformeDocumento3 páginasInformePaola BeltránAún no hay calificaciones

- Laboratorio 8 - Modulador de Disparo Del SCR PDFDocumento30 páginasLaboratorio 8 - Modulador de Disparo Del SCR PDFAldo Tolaba Quiroga0% (1)

- FICHA 1 Trabajo en Casa SéptimoDocumento37 páginasFICHA 1 Trabajo en Casa SéptimoNelson Ariel GomezAún no hay calificaciones

- Investigacion de Sistema Operativo 01Documento6 páginasInvestigacion de Sistema Operativo 01samanthaqm702Aún no hay calificaciones

- Documento - EncapsuladosDocumento4 páginasDocumento - EncapsuladosLucas EscuderoAún no hay calificaciones

- Proyecto de NavidadDocumento12 páginasProyecto de NavidadLuis LirAún no hay calificaciones

- 3 GeneracionDocumento12 páginas3 GeneracionGerardo Rincón SaucedoAún no hay calificaciones

- Micro/NanoDocumento35 páginasMicro/NanoJavier Gustavo NoriegaAún no hay calificaciones

- Proteus Configuracion PropiedadelPicDocumento4 páginasProteus Configuracion PropiedadelPicGallego OrtizAún no hay calificaciones

- Caso - Texas InstrumentsDocumento9 páginasCaso - Texas InstrumentsAnn Diaz MenesesAún no hay calificaciones

- Protección de Los Esquemas de Trazados de Circuitos IntegradosDocumento10 páginasProtección de Los Esquemas de Trazados de Circuitos IntegradosMarioValdes0% (1)

- Fabricacion y Programacion de Una Rebobinadora SemiautomaticaDocumento25 páginasFabricacion y Programacion de Una Rebobinadora SemiautomaticaJhustin Reyna Reyna50% (4)

- Probabilidad y EstadisticaDocumento5 páginasProbabilidad y EstadisticaAlvaro Marin0% (1)

- Chrysler Bueno PDFDocumento124 páginasChrysler Bueno PDFLucas Marcell Flores Muñoz89% (9)

- ScribDocumento9 páginasScribluisa FernandaCarrilloAún no hay calificaciones

- Introducción a la Electrónica DigitalDocumento6 páginasIntroducción a la Electrónica DigitalSebastian Pardo Figueroa DianderasAún no hay calificaciones

- Circuitos Digitales ConvencionalesDocumento11 páginasCircuitos Digitales ConvencionaleshgcuAún no hay calificaciones

- Clase CMOS Y TTLDocumento66 páginasClase CMOS Y TTLerteduAún no hay calificaciones

- Generaciones ComputadorasDocumento1 páginaGeneraciones ComputadorasAbraham Flores100% (1)