Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Tema2 PDF

Cargado por

Mauricio MontañoTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Tema2 PDF

Cargado por

Mauricio MontañoCopyright:

Formatos disponibles

Electrnica Digital

Tema 2

Dispositivos Lgicos Programables

(PLD)

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables

Introduccin.

Dispositivos Lgicos Programables Sencillos.

Dispositivos Lgicos Programables Complejos.

FPGAs.

PLDs con Procesadores Empotrados. Soft

cores.

Consideraciones para la eleccin de un PLD.

Tabla comparativa.

Ejemplo de sistema: tarjeta PRINCE.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables. Introduccin

Los PLDs son dispositivos electrnicos digitales

cuya funcionalidad puede ser programada por el

usuario.

El modo en que las funciones lgicas deseadas

se materializan en el dispositivo depende de la

estructura interna del mismo.

Son componentes disponibles comercialmente y

configurables directamente por el usuario.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables. Introduccin

Materializacin de funciones lgicas:

Estructuras AND-OR.

Multiplexores.

Memorias RAM.

Adems incluyen otros elementos:

Flip-flops.

Memorias.

...

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables. Introduccin

Estructuras AND-OR

Materializacin de funciones como suma de

productos (minitrminos).

Permiten configurar un nmero limitado de

minitrminos que se suman en una OR lgica.

Se suelen conocer con el acrnimo PAL

(Programmable Array Logic).

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables. Introduccin

Estructuras AND-OR

Arquitectura:

...

Conexin Programable

...

... Salida

Entradas ...

...

...

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables. Introduccin

Estructuras AND-OR

Otras simbologas:

Entradas

Salida Array n Salida

AND

programable

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables. Introduccin

Multiplexores

Otra forma de materializar funciones lgicas.

No suele emplearse en PLD sencillos.

Arquitectura:

Salida

Entradas

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables. Introduccin

Memorias

Almacenamiento en una memoria RAM de la tabla

de verdad de una funcin combinacional.

No suele emplearse en PLD sencillos.

Se les denomina look-up tables (LUT).

n

Direcciones

Entradas

Memoria

Salidas

m

Datos

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables. Introduccin

Memorias

Ejemplo: Memoria de 4 1 bit.

Memoria

00 0

A

01 1 F=AB

Entradas

B 10 1

Salida

11 0

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables. Introduccin

Caractersticas de los PLDs

Velocidad: Mayor que series estndar; menor que ASICs.

Tiempos de LUT + FF inferiores a 1ns.

Densidad de Integracin: Menor que ASICs.

Hasta 10 Mpuertas + Memoria + HW especfico

(multiplicadores, procesadores, etc.).

Coste de Desarrollo: Mucho menor que ASICs.

Prototipado y Verificacin: Ms sencillos que en ASICs.

Configuracin (RAM o Flash) in-system.

Modificacin de diseos: Sencilla.

Coste:

Depende del volumen.

Parmetro /puerta cada vez menor.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables. Introduccin

Fuerte competencia comercial multitud de siglas:

PLD: Programmable Logic Device.

PLA: Programmable Logic Array.

PAL: Programmable Array Logic.

GAL: Generic Array Logic.

CPLD: Complex PLD.

EPLD: Erasable PLD.

HCPLD: High Complexity PLD.

LCA: Logic Cell Array.

FPGA: Field Programmable Gate Array. ...etc

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables. Introduccin

Clasificacin:

Mayor densidad de integracin

PLD sencillos:

Arquitecturas PAL.

PLD complejos:

Agrupacin de los anteriores en un nico chip.

FPGAs:

Look-up tables o multiplexores.

PLD con procesadores empotrados:

FPGAs ms hardware especfico (multiplicadores,

microprocesadores de propsito general, DSP,

interfaces,...).

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables. Introduccin

Configuracin de los dispositivos:

Configuracin no voltil:

EPROM, EEPROM (Floating Gate Programming Technology).

PROM (Antifuse Programming Technology).

Configuracin voltil:

Memoria RAM.

Modos de Configuracin:

Separando el circuito de la tarjeta (dispositivos antiguos o muy

sencillos).

Programacin en el sistema (In System Programmability, ISP).

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables sencillos

PALCE22V10: Diagrama de bloques.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables sencillos

PALCE22V10: Detalle de la Macrocelda de salida.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables sencillos

PALCE22V10: Posibles configuraciones de salida.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables Complejos

Elementos constitutivos

Bloques lgicos.

Permiten la materializacin de las funciones lgicas.

Tpicamente son estructuras PAL y flip-flops.

Bloques de entrada/salida.

Asociados a los pines del dispositivo.

Permiten diversas configuraciones: entrada, salida,

bidireccional, registrada, no registrada, etc.

Recursos de interconexin.

Permiten la conexin entre bloques de los descritos

anteriormente.

Introducen retardo.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables Complejos

Familia MAX3000A: Diagrama de bloques.

Bloque Lgico

Bloque E/S

Interconexin

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables Complejos

Familia MAX3000A: Bloque Lgico (Macrocell).

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables Complejos

Familia MAX3000A: Recursos de interconexin (PIA).

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables Complejos

Familia MAX3000A: Bloque de entrada/salida

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Dispositivos Lgicos Programables Complejos

Familia MAX3000A: Caractersticas de algunos

elementos de la familia:

EPM3032A ... EPM3128A ... EPM3512A

Puertas 600 2.500 10.000

Macrocells 32 128 512

LABs 2 8 32

Pines I/O 36 98 208

FCNT 2273 MHz 1923 MHz 1163 MHz

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Elementos constitutivos.

Bloques lgicos.

Permiten la materializacin de las funciones lgicas.

Habitualmente son LUT (o multiplexores) y flip-flops.

Bloques de entrada/salida.

Asociados a los pines del dispositivo.

Diversas configuraciones.

Control de slew-rate, salidas open-drain, PCI, multitensin...

Memoria.

Bloques de memoria RAM utilizable como tal (simple o doble

puerto), o como ROMs o FIFOs, o para materializar funciones

lgicas.

Recursos de interconexin.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia FLEX10K: Diagrama de bloques.

Bloque Lgico

Memorias

Bloque E/S

Interconexin

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia FLEX10K: Bloque Lgico (Logic Array Block).

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia FLEX10K: Bloque Lgico (Logic Element, LE).

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia FLEX10K:

Bloque de E/S

(IOE).

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia FLEX10K: Memoria (Embedded Array Block, EAB).

Bloques de RAM que admiten diversas configuraciones y

conexiones

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia FLEX10K: Recursos de Interconexin (FastTrack)

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia FLEX10K: Modos de Configuracin.

Activo Pasivo

(bajo control del FPGA) (bajo control exterior)

EEPROM serie Cable de configuracin

Serie externa Microprocesador externo

EEPROM serie externa

EEPROM paralelo EEPROM paralelo

externa externa

Paralelo

Microprocesador externo

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia FLEX10K: Configuracin JTAG.

TMS, TCK

TDI TDI TDO TDI TDO

Conector JTAG FLASH FPGA

TDO

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia FLEX10K: Configuracin JTAG.

Vcc

Configuracin

FPGA #1 FPGA #2 ... FPGA #n

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia FLEX10K: Tensiones de Alimentacin.

Subfamilias FLEX10K.

FLEX 10KE (2.5 V).

FLEX 10KA (3.3 V).

FLEX 10K (5.0 V).

Pines de Vcc y GND diferentes para Ncleo (VCCINT) y

Entrada/Salida (VCCIO).

Tensiones de alimentacin diferentes para Ncleo y

Entrada/Salida.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia FLEX10K: Tensiones de Alimentacin.

Tolerancia a otros niveles de tensin.

VCCINT VCCIO Entradas Salidas

5.0 5.0 3.3 5.0 5.0

FLEX 10K

5.0 3.3 3.3 5.0 3.3 5.0

3.3 3.3 2.5, 3.3, 5.0 3.3 5.0

FLEX 10KA

3.3 2.5 2.5, 3.3, 5.0 2.5

2.5 2.5 2.5, 3.3, 5.0 2.5

FLEX 10KE

2.5 3.3 2.5, 3.3, 5.0 2.5, 3.3, 5.0

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia FLEX10K: Caractersticas de algunos

elementos de la familia:

EPF10K10 ... EPF10K250

Puertas 10.000 250.000

LEs 576 12.160

LABs 72 1.520

EABs 3 (6.144 bits) 20 (40.960 bits)

Pines I/O 150 470

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Tendencias:

Mayor densidad de integracin (lgica y pines).

Interfaces: LVDS, LVTTL, LVCMOS, PCI, etc.

Disminucin de la tensin de alimentacin.

Multiplicadores Hardware.

PLLs.

Ms flexibilidad en el manejo y la distribucin de relojes.

Modos de power down.

Lneas de retardo programables

Ms memoria.

Mayor velocidad.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Cyclone II: recursos

Cyclone-II EP2C5 ... EP2C70

LEs 4.608 68.416

M4K RAM blocks

26 250

(4Kbits+512 bits de paridad)

RAM bits 119.808 1.152.000

Multiplicadores 13 150

PLLs 2 4

Pines I/O 158 622

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Cyclone II: diagrama de bloques

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Cyclone II: logic element (LE) en modo normal

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Cyclone II: logic element (LE) en modo aritmtico

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Cyclone II: distribucin de reloj

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Stratix II: recursos

Stratix-II EP2S15 ... EP2S180

ALMs 6.240 71.760

LEs (equiv) 15.600 179.400

M512 RAM blocks

104 930

512 bits

M4K RAM blocks

78 768

4K bits

M-RAM blocks

0 9

512 K bits

RAM bits (total) 419.328 9.383.040

Bloques DSP/ Multiplicadores 12/48 96/384

PLLs 6 12

Pines I/O 366 1170

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Stratix II: diagrama de bloques

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Stratix II: adaptative logic modules (ALMs)

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Stratix II: ALM en modo normal para funciones

de 6 entradas

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Stratix II: ALM en modo aritmtico

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Stratix II: distribucin de reloj

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Virtex 4: 3 subfamilias

LX, optimizada para aplicaciones lgicas

SX, optimizada para aplicaciones de procesado digital de la

seal .

FX, optimizada para sistemas embebidos.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

FPGAs

Familia Virtex 4: recursos

Virtex 4 XC4VLX15 ... XC4VLX200

CLBs 1.536 22.272

RAM blocks

48 336

18 Kbits

RAM bits (total) 884.736 6.193.152

Bloques DSP 32 96

DCMs 4 12

Pines I/O 320 960

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

PLDs con procesadores empotrados

Elementos constitutivos.

FPGA:

Bloques lgicos.

Bloques de entrada/salida.

Memoria.

Recursos de interconexin.

Multiplicadores y Acumuladores para Procesado Digital

Microprocesador y Perifricos.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

PLDs con procesadores empotrados

Familia Virtex 4 FX

1 2 Power PC 405 cores

Arquitectura Harvard de 32 bits.

Caches de 16 KB integradas para instrucciones y datos.

Interfaz eficiente con los bloques de RAM del FPGA.

2 4 EMAC cores

10/100/1000 Mb/s

RocketIO Transceiver

8-24 canales

622Mb/s-6.5 Gb/s.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

PLDs con procesadores empotrados

Soft cores: MicroBlaze

IP de Xilinx

Cores de los perifricos

ms comunes

Herramientas de desarrollo

GNU

Varios RTOS

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

PLDs con procesadores empotrados

Soft cores: NIOS II

IP de Altera

Cores de los perifricos

ms comunes

Entorno de desarrollo

Varios RTOS

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Consideraciones para la eleccin de un PLD

Complejidad del diseo:

Area.

Nmero de puertas y flip-flops.

RAM integrada.

Otros recursos (triestado internos, multiplicadores, etc.).

Velocidad.

Frecuencia de reloj.

Retardo de bloque lgico y de conexionado.

Tipo de funciones (n de variables y n de minitrminos).

Nmero de entradas y salidas.

Entradas o salidas especiales (open-drain, PCI, LVDS ...).

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Consideraciones para la eleccin de un PLD

Caractersticas de sistema:

Tipo de encapsulado.

Accesibilidad a los pines (test).

Precio.

Configuracin.

Fuera del sistema o in system (requiere conector).

No voltil o voltil (precisa, adems, elemento de

configuracin).

Tensiones de alimentacin.

Reguladores para obtenerlas.

Compatibilidad con otros circuitos del sistema.

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Consideraciones para la eleccin de un PLD

Otros aspectos:

Herramientas de desarrollo.

Disponibilidad (precio).

Prestaciones y calidad.

Disponibilidad de IPs.

PRECIO. !

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

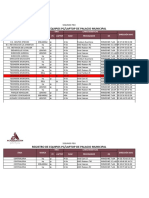

Precios Dispositivos Lgicos Programables

Dispositivo Familia LEs RAM DSP blocks / Pines de Precio

(bits) Multipliers E/S de (USD)

usuario

EPF10K30 Flex 10K 1.728 12.288 - 246 -

EPM3032 Max 3000A 42 (eq) - - 34 1.2-2.4

EPM3512 Max 3000A 666 (eq) - - 208 42.5-70

EP1C3 Cyclone 2.910 59.904 - 104 10.7-16.0

EP1C4 Cyclone 4.000 78.336 - 301 19.2-28.8

EP1C20 Cyclone 20.060 294.912 - 301 65.7-98.7

EP2C5 Cyclone II 4.608 119.808 - / 13 150 12.8-17.9

EP2C70 Cyclone II 68.416 1.152.000 - / 150 622 235-307

EP1S10 Stratix 10.570 920.448 6 / 48 426 190-350

EP1S80 Stratix 79.040 7.427.520 22 / 176 1.238 4.980-

7.195

EP2S15 Stratix II 15.600 (eq) 419.328 12 / 48 366 190-265

EP2S180 Stratix II 179.400 (eq) 9.383.040 96 / 384 1.170 6.135-

9.350

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Ejemplos

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Ejemplos

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

Ejemplos

Dpto. de Sistemas Electrnicos y de Control. UPM Curso 2010-2011

También podría gustarte

- Ejercicios Resultos de Sub-Espacios VectorialesDocumento26 páginasEjercicios Resultos de Sub-Espacios VectorialesSantiago Daza100% (5)

- Tabla de IntegralesDocumento12 páginasTabla de IntegralesEdgar100% (22)

- Arrollamientos PDFDocumento20 páginasArrollamientos PDFEdwin Santiago Villegas AuquesAún no hay calificaciones

- ProlatDocumento73 páginasProlatWEROMEAún no hay calificaciones

- ProlatDocumento73 páginasProlatWEROMEAún no hay calificaciones

- Bobinas PDFDocumento28 páginasBobinas PDFAdan Meiner Benites RodríguezAún no hay calificaciones

- Calculadora Gráfica HP Prime PDFDocumento684 páginasCalculadora Gráfica HP Prime PDFKei Kurono KuronoAún no hay calificaciones

- Osciladores Capitulo 6Documento18 páginasOsciladores Capitulo 6mdtjrlcAún no hay calificaciones

- Primera Clase PDFDocumento34 páginasPrimera Clase PDFMaycol Antonio RojasAún no hay calificaciones

- Esp Vect Ejer Soluc PDFDocumento25 páginasEsp Vect Ejer Soluc PDFAnonymous cYy5YgJAún no hay calificaciones

- Nyq Jul 2001Documento8 páginasNyq Jul 2001Lucas Matías JuarezAún no hay calificaciones

- Registros de DesplazamientoDocumento30 páginasRegistros de Desplazamientoabeat_1100% (2)

- Ejercicios Nyquist2 PDFDocumento2 páginasEjercicios Nyquist2 PDFMauricio MontañoAún no hay calificaciones

- Tipos de Antenas y Funcionamiento - Introduccion A Las TelecomunicacionesDocumento9 páginasTipos de Antenas y Funcionamiento - Introduccion A Las TelecomunicacionesUziel Hernandez CazarinAún no hay calificaciones

- EscapeDocumento14 páginasEscapeAna Carrasco MartínezAún no hay calificaciones

- 1taller de SIMULINK y Procesamiento DeSe AlesDocumento26 páginas1taller de SIMULINK y Procesamiento DeSe AlesSantos EscobedoAún no hay calificaciones

- 2.2 Dominio TiempoyfrecDocumento23 páginas2.2 Dominio TiempoyfrecJuan RodriguezAún no hay calificaciones

- Transformador Real Norberto A LemozyDocumento10 páginasTransformador Real Norberto A LemozyenriqueunoAún no hay calificaciones

- 06-Error en Estado Estable 2 - 06 - Error en Estado Estable o Estacionario PDFDocumento11 páginas06-Error en Estado Estable 2 - 06 - Error en Estado Estable o Estacionario PDFMauricio MontañoAún no hay calificaciones

- Problemas 3 Motores AsíncronosDocumento3 páginasProblemas 3 Motores AsíncronosMauricio MontañoAún no hay calificaciones

- Registros de DesplazamientoDocumento30 páginasRegistros de Desplazamientoabeat_1100% (2)

- Analisis TransformadorDocumento21 páginasAnalisis TransformadorBrian Martin Rodriguez AlvarezAún no hay calificaciones

- Maquinas de Indusccion Asincronas Ocw - Captitulo - IIDocumento38 páginasMaquinas de Indusccion Asincronas Ocw - Captitulo - IIJm MoAún no hay calificaciones

- Lab. No.6 Ensayo Motores AsíncronosDocumento5 páginasLab. No.6 Ensayo Motores Asíncronoscalderas joseAún no hay calificaciones

- Comparacinentrelasfamiliaslgicas 141108134716 Conversion Gate01Documento1 páginaComparacinentrelasfamiliaslgicas 141108134716 Conversion Gate01Mauricio MontañoAún no hay calificaciones

- Prac 10Documento1 páginaPrac 10Mauricio MontañoAún no hay calificaciones

- Presentacion Lineas Transmision Terminadas PDFDocumento57 páginasPresentacion Lineas Transmision Terminadas PDFjorge perezAún no hay calificaciones

- Tesis539 PDFDocumento66 páginasTesis539 PDFjaliesispAún no hay calificaciones

- Ejercicios Lineas de Transmision TerminadasDocumento3 páginasEjercicios Lineas de Transmision TerminadasAlba AmeliaAún no hay calificaciones

- Familias LogicasDocumento5 páginasFamilias LogicasPablo Andrés100% (1)

- 01 Familias Compuertas LogicasDocumento5 páginas01 Familias Compuertas LogicasSergio Garcia HernandezAún no hay calificaciones

- Cotizacion DdtechDocumento4 páginasCotizacion Ddtechmarcoantonio777Aún no hay calificaciones

- Historia Del CPUDocumento25 páginasHistoria Del CPUJose BarahonaAún no hay calificaciones

- Unidad 2Documento80 páginasUnidad 2Hatapro Abaran SaidAún no hay calificaciones

- Trabajo Grupal No1 EnsambleDocumento82 páginasTrabajo Grupal No1 EnsambleLorena P. GutiérrezAún no hay calificaciones

- Practica 18Documento5 páginasPractica 18eduardo martinesAún no hay calificaciones

- MicroprocesadorDocumento2 páginasMicroprocesadorRenzo DelgadoAún no hay calificaciones

- Memoria InternaDocumento6 páginasMemoria Internapatty ayalaAún no hay calificaciones

- Configuracion PCDocumento2 páginasConfiguracion PCWilliam L. Taype PerezAún no hay calificaciones

- Compute & Storage Top - Value - PVPDocumento29 páginasCompute & Storage Top - Value - PVPjcbp9Aún no hay calificaciones

- Que Es Un MicroprocesadorDocumento4 páginasQue Es Un MicroprocesadorJose Eduardo MayaAún no hay calificaciones

- Microporcesador AvrDocumento13 páginasMicroporcesador AvrCRISTOFHER SHANDEE ANASTACIO CHÁVEZAún no hay calificaciones

- Actividad 2Documento2 páginasActividad 2XIFITO 19Aún no hay calificaciones

- Trabajo de Memorias RAM - ROMDocumento28 páginasTrabajo de Memorias RAM - ROMdeyvisAún no hay calificaciones

- Tipos y Modelos de ProcesadoresDocumento22 páginasTipos y Modelos de ProcesadoresbaironAún no hay calificaciones

- Censo de Pc-LaptosDocumento7 páginasCenso de Pc-LaptosDoloresFuertesDeBarrigaAún no hay calificaciones

- SRAMDocumento10 páginasSRAMzxczxAún no hay calificaciones

- Familias LógicasDocumento6 páginasFamilias LógicasJonathan Sandoval FernándezAún no hay calificaciones

- CPLD FpgaDocumento24 páginasCPLD FpgaKerry Mayer Nolasco HuamánAún no hay calificaciones

- Cronologia de Los Procesadores IntelDocumento15 páginasCronologia de Los Procesadores IntelmarcosgarnicaAún no hay calificaciones

- Cuarta GeneracionDocumento24 páginasCuarta GeneracionRotherick Calderon MolinaAún no hay calificaciones

- G1 - Brochure Skpbasico InterDocumento6 páginasG1 - Brochure Skpbasico InterMilton Huallpa MamaniAún no hay calificaciones

- Problemas Propuestos: A. B. C. DDocumento8 páginasProblemas Propuestos: A. B. C. DLeila CuelloAún no hay calificaciones

- Actividad 3.1 Analisis Del Set de Instrucciones Del PIC16F84 VEGADocumento15 páginasActividad 3.1 Analisis Del Set de Instrucciones Del PIC16F84 VEGAYazmin GuerreroAún no hay calificaciones

- Tema 3 Jerarqu A de MemoriaDocumento59 páginasTema 3 Jerarqu A de MemoriaYirmel SanchezAún no hay calificaciones

- Lista de Precios LaptopsDocumento2 páginasLista de Precios LaptopssergioRssssAún no hay calificaciones

- MicrochipDocumento2 páginasMicrochipDANIEL ALEJANDRO GARCIA PENAAún no hay calificaciones

- Familia Lógica TTLDocumento3 páginasFamilia Lógica TTLGeovanni ConumbaAún no hay calificaciones

- Evolución de Los ProcesadoresDocumento8 páginasEvolución de Los Procesadoresdavid lopezAún no hay calificaciones

- Microprocesador 8085Documento7 páginasMicroprocesador 8085Percy VillegasAún no hay calificaciones