Documentos de Académico

Documentos de Profesional

Documentos de Cultura

VHDL IntroEntityArchitecture

Cargado por

Alberto Jose Redondo DiazGranadosTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

VHDL IntroEntityArchitecture

Cargado por

Alberto Jose Redondo DiazGranadosCopyright:

Formatos disponibles

Using VHDL for Synthesis of

Digital System

MSc Heiner Castro

Por qu usar Hardware

Description Language -HDL-?

La captura en esquemtico de sistemas

digitales se hace tediosa para diseos

complejos y extensos.

Con un HDL se reduce tiempo y costo.

Permite una exploracin rpida de

diversas alternativas.

Reuso del diseo.

VHDL: Very High Speed Integrated Circuit

Hardware Description Language

Es un lenguaje de descripcin y modelado de

sistemas digitales.

Es una herramienta estndar e independiente.

Standard 1076 y 1164 de IEEE.

La descripcin se realiza de una forma

independiente de la tecnologa a emplear.

Se basa en un alto nivel en la sintaxis (no en la

abstraccin).

Soportado por numerosas herramientas CAD.

VHDL: Historia y Evolucin

1980: El departamento de defensa de Estados

Unidos inicia el proyecto.

1985: Versin 7.2 en dominio pblico.

1987: Estndar IEEE 1076 (VHDL 87).

1993: Nueva versin del estndar, VHDL 93.

2000 y 2002 Actualizacin del estndar IEEE 1076.

Cambios menores a la versin 93.

2008. Mayor compatibilidad hacia otros lenguajes

(C++) y con mayor posibilidad de diseo de alto

nivel.

Hardware Vs. Software

Software

La mayora de los lenguajes de

programacin convencionales

estn basados en un modelo de

operacin secuencial.

Los lenguajes de programacin

convencionales no pueden

describir o modelar la operacin

del hardware digital debido a que

no incluyen la nocin del tiempo

en sus sentencias.

Hardware

El hardware digital posee una

naturaleza paralela de

funcionamiento.

Las entradas, las salidas y los

circuitos mismos dependen del

tiempo.

HDLs

Todos los lenguages de

descripcin de hardware estan

definidos para modelar

operaciones paralelas o

concurrentes.

Todos los HDLs incluyen

sentencias para emular el tiempo

en las descripciones.

Elementos Sintcticos de

VHDL

Entidades

Arquitecturas

Seales

Puertos

Entity

Define la visin externa del

dispositivo, interfaz con el

entorno.

Permite realizar diseos

jerrquicos: puede ser

reutilizada por otros

diseos manteniendo

oculta la implementacin

concreta del sistema.

entity ejemplo1 is

port (C: in std_logic;

A,B: in std_logic_vector (3 downto 0);

E: out std_logic;

F: out std_logic_vector (3 downto 0));

end ejemplo1;

Ports

in

Los puertos de entrada

slo se pueden leer.

No es permitido

asignarles ninguna

conexin.

out

Las puertos de salida

pueden cambiar y es

posible asignarles

valores.

No pueden leerse. No

es vlido usarlas como

argumentos.

port: define las entradas y salidas del mdulo descrito.

inout: describe a un puerto bidireccional, el cual permite

operaciones de escritura y lectura.

Type Std_logic

Type Std_logic:

'1' : Bit 1

'0' : Bit 0

'X' : Unknown

'U' : Uninitialized

'Z' : High impedance

'L' : Driven low weakly

'H' : Driven high weakly

'W' : Weak unknown

'-' : Do not care

Type bit

'1' : bit 1

'0' : bit 0

Architecture

Sirve para definir la funcionalidad

de la entidad que representa.

Siempre est referida a una

entidad concreta.

Una misma entidad puede tener

diferentes arquitecturas.

architecture behavioral of ejemplo1 is

-- parte declarativa

begin

-- sentencias concurrentes

F <= A - not (B) + C;

E <= not ( A(3) or A(2) or A(1) or A(0) );

end behavioral;

Architecture: signals

architecture behavioral2 of ejemplo1 is

-- parte declarativa

signal X,Y : std_logic_vector (3 downto 0);

begin

F <= Y + C;

X <= not B;

E <= A(3) nor A(2) nor A(1) nor A(0);

Y <= A - X;

end behavioral2;

VHDL Operators

Highest precedence first, left to right within same precedence group,

use parenthesis to control order.

Unary operators take an operand on the right.

"result same" means the result is the same as the right operand.

Binary operators take an operand on the left and right.

Arithmetic Operators

** exponentiation, numeric ** integer, result numeric X <= Y**3;

abs absolute value, abs numeric, result numeric X <= abs (Y);

* multiplication, numeric * numeric, result numeric X <= Y*Z;

/ division, numeric / numeric, result numeric X <= Y/Z;

mod modulo, integer mod integer, result integer X <= Z mod Y;

rem remainder, integer rem integer, result integer X <= Y rem Z;

+ unary plus, + numeric, result numeric X <= +Y;

- unary minus, - numeric, result numeric X <= -Y;

+ addition, numeric + numeric, result numeric X <= Y + Z

- subtraction, numeric - numeric, result numeric X <= Y - Z

source: http://www.cs.umbc.edu/portal/help/VHDL/operator.html

VHDL Operators

Shift Operators

sll shift left logical, logical array sll integer, result same, X <= Y sll 1;

srl shift right logical, logical array srl integer, result same X <= Y srl 2;

sla shift left arithmetic, logical array sla integer, result same X <= Y sla 3;

sra shift right arithmetic, logical array sra integer, result same X <= Y sra 4;

rol rotate left, logical array rol integer, result same X <= Y rol 5;

ror rotate right, logical array ror integer, result same X <= Y ror 6;

& (1) concatenation, array or element & array or element, result array

X <= Y & Z;

Boolean Operators

= test for equality, result is boolean X = Y; F <= X = Y;

/= test for inequality, result is boolean X /= Y; F <= X /= Y;

< test for less than, result is boolean X < Y; F <= X < Y;

<= test for less than or equal, result is boolean X <= Y; F <= X <= Y;

> test for greater than, result is boolean X > Y; F <= X > Y;

>= test for greater than or equal, result is boolean X >= Y; F <= X >= Y;

(1) Precedence priority 12th

VHDL Operators

Logic Operators

not (2) complement, not logic or boolean, result same X <= not (Y);

and logical and, logical array or boolean, result is same X <= Y and Z;

or logical or, logical array or boolean, result is same X <= Y or Z;

nand logical complement of and, logical array or boolean, result is same

X <= Y nand Z;

nor logical complement of or, logical array or boolean, result is same

X <= Y nor Z;

xor logical exclusive or, logical array or boolean, result is same X <= Y xor Z;

xnor logical complement of exclusive or, logical array or boolean, result is same

X <= Y xnor Z;

(2) Precedence priority 3rd

source: http://www.cs.umbc.edu/portal/help/VHDL/operator.html

VHDL Operators

library IEEE;

use IEEE.std_logic_1164.all, IEEE.numeric_std.all;

entity nBitAdder is

generic (n: NATURAL :=8);

Port (A,B: in std_logic_vector (n-1 downto 0);

Sum: out std_logic_vector (n downto 0));

end entity nBitAdder;

Architecture behavioral of nBitAdder is

Begin

sum <= (0&A) + (0&B); --add including Carry-out

end behavioral;

Architecture: exercise

Escriba la descripcin completa (entidad y arquitectura) de un circuito

que le cambie el signo a un nmero binario con signo de 8 bits en

formato complemento a 2. En este ejercicio no puede usar sentencias

if then o when else, solamente compuertas, sumadores y restadores.

Escriba el cdigo VHDL del

circuito que se muestra en la

figura. Todos los buses son de 4

bits. No puede usar sentencias if

then o when else, solamente

compuertas, sumadores y

restadores. Cuidado que las

salidas no pueden leerse.

VHDL combinational blocks: adders

Escriba la descripcin de hardware

completa en VHDL del sumador de la

figura si A, B y Sum son buses de n

bits y los dems puertos son de 1 bit.

Desarrolle el cdigo VHDL para un sumador genrico de n bits con datos

de entrada con signo en formato complemento a 2.

Desarrolle el VHDL para un restador genrico de n bits con datos de

entrada sin signo. El resultado de la diferencia debe tener un bit de ms

donde este el prstamo. El circuito debe tener en cuenta un prstamo de

entrada.

Desarrolle el VHDL para un restador genrico de n bits con datos de

entrada con signo en formato complemento a 2.

VHDL combinational blocks examples

if a < b then

Amenor <= '1';

else Amenor <= '0';

if a = b then

Aigual <= '1';

else Aigual <= '0';

--a, b must be vectors for all comparations to take place

--Comparators

if a > b then

Amayor <= '1';

else Amayor <= '0';

--Multiplier

M <= A*B; --m, a, b must vectors, size of M = size of A + size of B.

--Adder/substractor

S <= A + B; --s, a, b must be vectors

R <= A - B; --r, a, b must be vectors, R is in Two's complement

For the next class

También podría gustarte

- Simulacro Atencion Cliente CORREOSDocumento66 páginasSimulacro Atencion Cliente CORREOSC. A.Barriuso100% (3)

- Clase2 AlgoritmosDocumento32 páginasClase2 AlgoritmosCarlos DíazAún no hay calificaciones

- Cuestiones Éticas en Psicoterapia en LíneaDocumento72 páginasCuestiones Éticas en Psicoterapia en LíneaEva PardoAún no hay calificaciones

- Auditoría financiera en ExcelDocumento32 páginasAuditoría financiera en ExcelDanilo Mauricio Torres100% (1)

- Protección contra caídasDocumento5 páginasProtección contra caídasJulio Rene Ccopa QuispeAún no hay calificaciones

- Práctica 6 - Circuito Decodificador de Código Hexadecimal A Sistema de 7 Segmentos Implementado en PLDDocumento12 páginasPráctica 6 - Circuito Decodificador de Código Hexadecimal A Sistema de 7 Segmentos Implementado en PLDLomeleanAún no hay calificaciones

- SEMANA 2 (Compuertas Lógicas y Álgebra Booleana) (COMPLETO)Documento57 páginasSEMANA 2 (Compuertas Lógicas y Álgebra Booleana) (COMPLETO)gl devAún no hay calificaciones

- Programación con lenguajes de guión en páginas web. IFCD0110De EverandProgramación con lenguajes de guión en páginas web. IFCD0110Aún no hay calificaciones

- Banda Lateral Unica Con Portadora SuprimidaDocumento32 páginasBanda Lateral Unica Con Portadora SuprimidaAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Determinación de HumedadDocumento2 páginasDeterminación de HumedadMamo56% (9)

- Cálculo de La EvapotranspiraciónDocumento6 páginasCálculo de La Evapotranspiraciónhalbornoz86Aún no hay calificaciones

- Sumador Completo de Dos Bits en VHDLDocumento4 páginasSumador Completo de Dos Bits en VHDLPepeE.BenítezAún no hay calificaciones

- Sumador 2 Bits: Código en VHDL Utilizando Un Algoritmo FuncionalDocumento5 páginasSumador 2 Bits: Código en VHDL Utilizando Un Algoritmo FuncionalraulAún no hay calificaciones

- VHDLDocumento23 páginasVHDLHolamundoAún no hay calificaciones

- Clase 2Documento58 páginasClase 2Francisco LopezAún no hay calificaciones

- Sumador Completo de Dos Bits en VHDLDocumento4 páginasSumador Completo de Dos Bits en VHDLVictor Alejandro100% (1)

- Tipos de Datos en JavaDocumento12 páginasTipos de Datos en JavaJhonmanAún no hay calificaciones

- Práctica 2 - Compuertas Lógicas - Medina Oscar 4-A MAADocumento9 páginasPráctica 2 - Compuertas Lógicas - Medina Oscar 4-A MAAOSCAR ADRIAN MEDINA DURANAún no hay calificaciones

- Practica 6Documento12 páginasPractica 6hector blancoAún no hay calificaciones

- Diseño Logico Combinacional Con VHDLDocumento77 páginasDiseño Logico Combinacional Con VHDLENIC-AITCGAún no hay calificaciones

- Práctica 5 - Sumador Completo - Medina Oscar 4ADocumento8 páginasPráctica 5 - Sumador Completo - Medina Oscar 4AOSCAR ADRIAN MEDINA DURANAún no hay calificaciones

- 2 - Diseno Logico Combinacional Mediante VHDLDocumento21 páginas2 - Diseno Logico Combinacional Mediante VHDLGenus ArangurenAún no hay calificaciones

- Tipos de Operadores C++Documento27 páginasTipos de Operadores C++Erick GarcíaAún no hay calificaciones

- Pseint InstruccionesDocumento78 páginasPseint InstruccionesKarolina Denia Jouide Hide0% (1)

- Pseint InstruccionesDocumento78 páginasPseint InstruccionesJorge Enrique Ramos CamargoAún no hay calificaciones

- Practicas VHDL FINALDocumento13 páginasPracticas VHDL FINALEnrique GomezAún no hay calificaciones

- JF 2 13 Practice EspDocumento3 páginasJF 2 13 Practice EspdukegaloAún no hay calificaciones

- 2 Dispositivos Integrados - Unidad FPGA VHDLDocumento111 páginas2 Dispositivos Integrados - Unidad FPGA VHDLAgustina Gutierrez PariAún no hay calificaciones

- IC3 Sol Jun2022 Sem2Documento9 páginasIC3 Sol Jun2022 Sem2eduAún no hay calificaciones

- Guia Pseint 2016-6-14Documento9 páginasGuia Pseint 2016-6-14Fabian Vargas JimenezAún no hay calificaciones

- Guia Pseint 2016Documento15 páginasGuia Pseint 2016Juliiân MayorgaAún no hay calificaciones

- Python Manual para PrincipiantesDocumento7 páginasPython Manual para PrincipiantesJose BiscottiAún no hay calificaciones

- VHDL Su Organizacion y ArquitecturaDocumento20 páginasVHDL Su Organizacion y ArquitecturaTonaspiuckAún no hay calificaciones

- LIBRERIAS Más Importantes en C+Documento9 páginasLIBRERIAS Más Importantes en C+Franyelis DiazAún no hay calificaciones

- Curso VHDLDocumento27 páginasCurso VHDLedsonAún no hay calificaciones

- Programación en C: Microcontroladores y sistemas embebidosDocumento34 páginasProgramación en C: Microcontroladores y sistemas embebidosJosue Israel MendozaAún no hay calificaciones

- Reyesdeberquarus 2Documento16 páginasReyesdeberquarus 2Rosa CastroAún no hay calificaciones

- OperadoresExpresionesLab3Documento7 páginasOperadoresExpresionesLab3Franz Quispe FloresAún no hay calificaciones

- Introduccion Al Lenguaje VHDLDocumento21 páginasIntroduccion Al Lenguaje VHDLLucho PortuanoAún no hay calificaciones

- ALU Expandida en VHDLDocumento14 páginasALU Expandida en VHDLArmando GaviriaAún no hay calificaciones

- Sase2013 Intro VHDLDocumento40 páginasSase2013 Intro VHDLPreprensa BoxAún no hay calificaciones

- VHDL Intro PDFDocumento12 páginasVHDL Intro PDFjessicaAún no hay calificaciones

- Memoria de ejercicios Lógica DigitalDocumento24 páginasMemoria de ejercicios Lógica DigitalDavid Vilar PerisAún no hay calificaciones

- VHDL contador 4bits GAL22V10DDocumento9 páginasVHDL contador 4bits GAL22V10DFafancxAún no hay calificaciones

- VHDL declaraciones condicionales when-else y with-select-whenDocumento4 páginasVHDL declaraciones condicionales when-else y with-select-whenErikson Barreda LopezAún no hay calificaciones

- Conferencia 1. Expresiones lógicas y algoritmosDocumento10 páginasConferencia 1. Expresiones lógicas y algoritmosEzequielAún no hay calificaciones

- Problemas DigDocumento21 páginasProblemas DigAleja VargasAún no hay calificaciones

- Tarea VHDLDocumento13 páginasTarea VHDLJulio Cesar Romero100% (1)

- Características Generales de JavaDocumento11 páginasCaracterísticas Generales de JavaFrancisco MartínezAún no hay calificaciones

- 4-VHDL - Tipos de DatosDocumento19 páginas4-VHDL - Tipos de DatosDaniel ParedesAún no hay calificaciones

- Practica 13Documento3 páginasPractica 13gerardoAún no hay calificaciones

- Tarea 1 Corte 2Documento7 páginasTarea 1 Corte 2Jonathan Gilberto Alvarez RoaAún no hay calificaciones

- Introducción VHDL sintesis FPGADocumento36 páginasIntroducción VHDL sintesis FPGAJhosep AntonyAún no hay calificaciones

- Taller JavaDocumento12 páginasTaller Javadariolara100% (7)

- Sesion 3 Principios de Diseño Lógico Combinatorial (Parte 1)Documento55 páginasSesion 3 Principios de Diseño Lógico Combinatorial (Parte 1)coroline24Aún no hay calificaciones

- Sentencias en CDocumento40 páginasSentencias en CDARK REASON D'ETREAún no hay calificaciones

- Lab 4 DigitalDocumento7 páginasLab 4 DigitalCristhian Ustariz SalgueroAún no hay calificaciones

- Actividad 2 SolucionDocumento16 páginasActividad 2 SolucionAndres ZaensAún no hay calificaciones

- Logica Digital EjerciciosDocumento24 páginasLogica Digital EjerciciosfernandosssssAún no hay calificaciones

- Compuertas Logicas VHDLDocumento7 páginasCompuertas Logicas VHDLArthur RamXel100% (1)

- Operadores LógicosDocumento6 páginasOperadores LógicosCarlos David Villazon MojicaAún no hay calificaciones

- Código Scilab - Programación Básica y Métodos NuméricosDocumento32 páginasCódigo Scilab - Programación Básica y Métodos NuméricosIvan100% (1)

- Programación en VHDLDocumento17 páginasProgramación en VHDLsinchyAún no hay calificaciones

- P1 InstruVirtualDocumento10 páginasP1 InstruVirtualDiego Giovany Carrillo CardenasAún no hay calificaciones

- Informe 1 de Diseño DigitalDocumento10 páginasInforme 1 de Diseño DigitalpperfectionnAún no hay calificaciones

- Dialnet SanIgnacioDeLoyolaYLaTeologia 6367800Documento43 páginasDialnet SanIgnacioDeLoyolaYLaTeologia 6367800Alberto Jose Redondo DiazGranadosAún no hay calificaciones

- Una Ermita Quijotesca en El Campo de Montiel Albaceteño: San Pedro de SahelicesDocumento20 páginasUna Ermita Quijotesca en El Campo de Montiel Albaceteño: San Pedro de SahelicesAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Dialnet SanPedroMartirDeVeronaYElAguaDelCielo 2597363Documento4 páginasDialnet SanPedroMartirDeVeronaYElAguaDelCielo 2597363Alberto Jose Redondo DiazGranadosAún no hay calificaciones

- La Caridad CatesismoDocumento7 páginasLa Caridad CatesismoAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Granada en la beatificación de San IgnacioDocumento12 páginasGranada en la beatificación de San IgnacioAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Fo No Cardiogram ADocumento18 páginasFo No Cardiogram AAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Carcasa Híbrida Galaxy Tab A 8Documento1 páginaCarcasa Híbrida Galaxy Tab A 8Alberto Jose Redondo DiazGranadosAún no hay calificaciones

- Proceso de CanonizacionDocumento36 páginasProceso de CanonizacionAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Artículo Introducción Al Espíritu de La LiturgiaDocumento2 páginasArtículo Introducción Al Espíritu de La LiturgiaAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Articulo EcuacionesDocumento6 páginasArticulo EcuacionesAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- 4 1 OsciladoresDocumento31 páginas4 1 OsciladoresAlex Valverde CruzAún no hay calificaciones

- MemoriaDocumento10 páginasMemoriaAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Cirio PascualDocumento1 páginaCirio PascualAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Antena Road® 10 Metros LMR-400 PDFDocumento1 páginaAntena Road® 10 Metros LMR-400 PDFAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- CursodeinstrumentacionDocumento96 páginasCursodeinstrumentacionmarsiverianoAún no hay calificaciones

- Evolucion de La NeuropsicologiaDocumento71 páginasEvolucion de La NeuropsicologiaAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Faq FiltrosDocumento4 páginasFaq FiltrosAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Cap 07 FM Trans Mi SoresDocumento15 páginasCap 07 FM Trans Mi SoresAndres21216Aún no hay calificaciones

- Filtro Pasa Banda-AngostaDocumento12 páginasFiltro Pasa Banda-AngostaAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Lugar Geometrico de Las RaicesDocumento18 páginasLugar Geometrico de Las RaicesAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Sillas de Ruedas Controladas Por Señales ElectroculograficasDocumento2 páginasSillas de Ruedas Controladas Por Señales ElectroculograficasAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Cap08FMReceptores PDFDocumento11 páginasCap08FMReceptores PDFAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Habilidades en La IngenieriaDocumento4 páginasHabilidades en La IngenieriaHillary Carrillo ReyesAún no hay calificaciones

- Laboratorio No1 (Ele)Documento7 páginasLaboratorio No1 (Ele)Alberto Jose Redondo DiazGranadosAún no hay calificaciones

- Rayos X y Tomografia Conputalizada AplicacionesDocumento6 páginasRayos X y Tomografia Conputalizada AplicacionesAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Bases MusicalesDocumento9 páginasBases MusicalesAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Karaoke Stereo Con EcualizadorDocumento22 páginasKaraoke Stereo Con EcualizadorAlberto Jose Redondo DiazGranadosAún no hay calificaciones

- Enfoque de La Investigación - SampieriDocumento4 páginasEnfoque de La Investigación - SampieriJhasmin Jhosselin Tutaya BendezuAún no hay calificaciones

- Especificaciones Tecnicas Del Cemento Conductivo EARTH POINTDocumento15 páginasEspecificaciones Tecnicas Del Cemento Conductivo EARTH POINTAlex Ortiz DiazAún no hay calificaciones

- Matriz Herramientas Formato Sar 07-10-2019Documento2 páginasMatriz Herramientas Formato Sar 07-10-2019Lizeth Yadira Silva RondonAún no hay calificaciones

- Matriz Tabulacion Pruebas de Diagnostico SegundoDocumento17 páginasMatriz Tabulacion Pruebas de Diagnostico SegundoKarina PonceAún no hay calificaciones

- Ficha-Concertacion-Sílabo - Quimica IDocumento2 páginasFicha-Concertacion-Sílabo - Quimica IhernanAún no hay calificaciones

- Rehabilitación Después de Una Operación de Fractura de CalcáneoDocumento7 páginasRehabilitación Después de Una Operación de Fractura de CalcáneodfnoriegaAún no hay calificaciones

- Carta de No Poseer ViviendaDocumento3 páginasCarta de No Poseer ViviendaAndres SucreAún no hay calificaciones

- 03-SSR - Agencias de ViajesDocumento12 páginas03-SSR - Agencias de Viajesalfaorion11Aún no hay calificaciones

- Tema 4 Proteccion Civil - ASSODocumento34 páginasTema 4 Proteccion Civil - ASSOReyna OrtizAún no hay calificaciones

- Bombeo y Conex. DomicilDocumento3 páginasBombeo y Conex. DomicilELVISAún no hay calificaciones

- 8 884 2100 - 0006608155 - 01 Mar 2019 PDFDocumento1 página8 884 2100 - 0006608155 - 01 Mar 2019 PDFNestor Herrera HenriquezAún no hay calificaciones

- Equipos Especiales de Protección PersonalDocumento3 páginasEquipos Especiales de Protección PersonalJaider PalmaAún no hay calificaciones

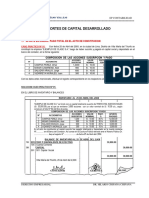

- 2 CarsaDocumento2 páginas2 CarsaSamuel BustillosAún no hay calificaciones

- Proyecto Alarma.Documento22 páginasProyecto Alarma.Evert Pirela100% (1)

- Seminario Modelos PedagogicosDocumento20 páginasSeminario Modelos PedagogicosGuillermo Merlano OrtegaAún no hay calificaciones

- Doctrina de La Protección Integral de La Niñez y de La Adolescencia.Documento7 páginasDoctrina de La Protección Integral de La Niñez y de La Adolescencia.Karen Gamero TobarAún no hay calificaciones

- 2013-3158 RELACION-PLANTA-AGUA Y SUELO Wilfredo Enrique Lira Palza PDFDocumento11 páginas2013-3158 RELACION-PLANTA-AGUA Y SUELO Wilfredo Enrique Lira Palza PDFXavier Lira PalzaAún no hay calificaciones

- Bomba Hidraulica-Lab Grupo A 2021Documento19 páginasBomba Hidraulica-Lab Grupo A 2021Omar Campos100% (1)

- Lab. Analítica (Práctica 3)Documento3 páginasLab. Analítica (Práctica 3)Santiago Vallejo100% (1)

- Act 02-03. Mapa Conceptual Yo Mental Sobre Términos y Definiciones ISO 140012015.Documento4 páginasAct 02-03. Mapa Conceptual Yo Mental Sobre Términos y Definiciones ISO 140012015.Gabriel García OrtizAún no hay calificaciones

- CASO Solucion 01 y 03Documento4 páginasCASO Solucion 01 y 03dayana magdiel de la cruz esteloAún no hay calificaciones

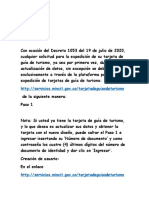

- Tramites Tarjeta Guianza TuristicaDocumento6 páginasTramites Tarjeta Guianza Turisticaalberto valenciaAún no hay calificaciones

- Qué Es La GeografíaDocumento7 páginasQué Es La GeografíaDaniel Bustamante MujicaAún no hay calificaciones

- Nro7069 - 2022 06 23Documento40 páginasNro7069 - 2022 06 23Diario Primera LíneaAún no hay calificaciones