Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Modelado PWM

Cargado por

Stiver MartinezTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Modelado PWM

Cargado por

Stiver MartinezCopyright:

Formatos disponibles

Captulo 2

Mtodo de Modelado Aplicando la Funcin

Pulso Unitario de Heaviside

Objetivos del Captulo

En este captulo se introducen los fundamentos matemticos y funcionales de la tcnica

de modelado no lineal desarrollada en esta tesis. Se comienza por la descripcin de las

caractersticas deseadas del modelo, que dan paso a los fundamentos desde los que se parte.

Seguidamente se describe el anlisis matemtico del proceso de modulacin PWM, por

medio de la transformada de Laplace y la funcin Pulso Unitario de Heaviside, para obtener

el modelo de simulacin del modulador PWM. A continuacin se plantea el modelado de

los ltros de salida de las etapas de los convertidores conmutados y de las etapas de control

PWM clsicas. Por ltimo se aplica la tcnica de modelado al paralelizado de convertidores

conmutados.

Como resultado se obtiene un modelo analtico de la modulacin PWM y un modelo

de simulacin no lineal aplicable a la simulacin de convertidores conmutados de potencia,

desarrollado en una biblioteca de mdulos de SIMULINK.

2.1. Introduccin a la Metodologa de Modelado

A la luz de la evolucin histrica de las tcnicas de modelado (ver el apartado 1.6 en la

pgina 48), asociadas a las necesidades de anlisis, desarrollo y comprensin del funcionamiento

de las distintas topologas de los convertidores conmutados de potencia, de sus circuitos de

control y de las asociaciones de convertidores para formar sistemas ms complejos, se plantea

la elaboracin de una tcnica de modelado que, a grandes rasgos, intenta aunar las virtudes

ms relevantes de los mtodos de modelado existentes y aprovechar las actuales capacidades

de cmputo de las plataformas de ordenadores y de los distintas herramientas informticas

disponibles.

59

Captulo 2. Mtodo de Modelado Aplicando ...

Las principales caractersticas de la metodologa de modelado propuesta son:

Descripcin matemtica y funcional del modulador PWM

La descripcin matemtica est basada en la funcin Pulso Unitario de Heaviside

Se obtiene un modelo de simulacin fcil de aplicar a los convertidores conmutados

El modelo del modulador PWM permite obtener distintos tipos de modulacin (natural,

uniforme, multinivel)

Descripcin matemtica y funcional del circuito de la etapa de salida del convertidor

Vlida tanto para modo continuo como discontinuo

Se obtienen las variables elctricas de la etapa de potencia

El modelo de simulacin permite la variacin, lineal y no lineal, de los parmetros de

los elementos que modelan la carga

Descripcin matemtica y funcional del circuito de la etapa de compensacin del convertidor

Modela las no linealidades de los circuitos de control disponibles comercialmente

Permite obtener las variables elctricas

Es posible implantar otros tipos de control (fuzzy, discreto, etc...)

El modelo es fcil de usar una vez implantado en el programa de simulacin (MATLAB Y

SIMULINK)

La plataforma de simulacin permite el crecimiento del modelo de forma modular

Es posible escoger el mtodo matemtico de resolucin de las ecuaciones diferenciales

La simulacin se puede llevar a cabo mediante interpretacin de los comandos por

parte del simulador, o bien por compilacin del modelo y obtencin de un programa

ejecutable

2.2. Fundamentos de la Metodologa de Modelado

Del funcionamiento de las cuatro topologas bsicas reductora (ver A.2.1 en la pgina 146),

elevadora (ver A.2.2 en la pgina 148), reductora-elevadora (ver A.2.3 en la pgina 150) y

Cuk

(ver A.2.4 en la pgina 152) se desprenden una serie de ideas que permiten la elaboracin de un

modelo no lineal.

La primera idea se obtiene de la observacin del conjunto de interruptores en el circuito

(generalmente un transistor actuando como interruptor controlado (S) y un diodo (D), que entra

en conduccin cuando el interruptor est abierto ), ya que estos componentes semiconductores

slo permiten el ujo de energa en un nico sentido en el convertidor. Esta idea se representa

grcamente en la Fig. 2.1

La segunda idea tiene su origen en la disposicin de los elementos pasivos que conforman

la etapa de salida de los convertidor: inductancia (L), condensador (C) y carga (generalmente

asimilada a R). Estos elementos pasivos, asociados a la presencia de un diodo (D), hacen que el

60

2.2 Fundamentos de la Metodologa de Modelado

(a) reductor (buck) (b) elevador (boost)

(c) reductor-elevador (buck-

boost)

(d) Cuk

Figura 2.1: Convertidores bsicos. Disposicin de los interruptores controlado (S)

y no controlado (D)

ltro de salida slo pueda trabajar dejando que la energa elctrica uya en un determinado sentido.

Dada su similitud, es posible obtener, de manera anloga para todos, un modelo que describa el

comportamiento de esta parte del circuito. Las capacidades de este circuito han sido estudiadas

intensivamente, pero es difcil encontrar anlisis detallados o completos [144146]. Esta idea se

representa grcamente en la Fig. 2.2

Uniendo las dos ideas anteriores es posible realizar una descripcin de la etapa de potencia

de un convertidor conmutado en dos bloques claramente interrelacionados: el primero es un

modulador PWM que genera una seal cuadrada genrica, similar al encendido y apagado del

interruptor controlado, el segundo bloque modela el comportamiento no lineal del ltro LCR de

salida del convertidor, que engloba el diodo.

Para obtener un sistema completo es necesario implantar la etapa de control. En el estado actual

de desarrollo de convertidores conmutados de potencia es un requisito fundamental que el modelo

de este bloque pueda acomodar los controles clsicos (PI, PID) y las elaboraciones ms complejas

de origen digital (control digital, fuzzy, deslizante, etc...).

Finalmente, el modelo debe permitir el modelado de elementos parsitos, tanto en los

elementos semiconductores como en los componentes pasivos, y la capacidad de hacer que el

modulador PWM presente caractersticas prximas a los circuitos reales de control. Sin perder de

vista el paralelizado de mdulos se hace necesario tener en cuenta que tanto el modulador como la

parte de control deben ser capaces de simular las singularidades que estos mtodos presentan.

61

Captulo 2. Mtodo de Modelado Aplicando ...

(a) reductor (buck) (b) elevador (boost)

(c) reductor-elevador (buck-

boost)

(d) Cuk

Figura 2.2: Convertidores bsicos - Componentes de la etapa de salida

2.3. El modulador PWM

El correcto funcionamiento del modelo del modulador en ancho de pulsos (pulse-width

modulator) es importante para alcanzar modelos matemticos y de comportamiento de los sistemas

que lo incorporen. Igualmente estos modelos deben permitir obtener informacin precisa sobre

el contenido de armnicos de la seal modulada y ser fcilmente aplicables en modelos de

circuitos elctricos y electrnicos para saber cmo se comportarn stos en presencia de las seales

moduladas.

Histricamente muchas tcnicas de modulacin

1

, especialmente aquellas complejas y las

que se sirven de tcnicas digitales, no pudieron ser implantadas debido a las limitaciones

de los semiconductores y de los circuitos de control. La modulacin natural y la uniforme

( tambin llamada por algunos autores muestreada - sampled) [147149] fueron las primeras

en ser aplicadas. Posteriormente, para controlar motores de tensin alterna con la ayuda de

circuitos digitales se aplicaron seales moduladas ms complejas [150153]. Ms ejemplos

donde se observa la importancia de la modulacin PWM los encontramos en [155], donde un

sistema con un microprocesador dedicado controla un inversor en fuente de tensin (VSI) con

transistores MOSFETs, empleando un esquema de modulacin especial que reduce el nmero de

conmutaciones, en [156] proponen un modulador PWM elaborado en un programa de ordenador

que permite las modulaciones clsicas y un modo especial de inyeccin de armnicos y en

[157, 158] con la ayuda de DSPs se aplica la modulacin PWM a la modulacin en el espacio

1

Por sencillez, siempre que se hable en este captulo de la modulacin en ancho de pulsos (PWM) la

denominaremos modulacin.

62

2.3 El modulador PWM

de vectores (space vector modulation, SVM).

Con el aumento de la complejidad de la modulacin tambin se increment la complejidad de

los modelos matemticos y de simulacin, en especial en aquellos casos en que se incluye el lazo

de control. Enfocados concretamente en modelar el proceso de modulacin, surgieron modelos

elaborados empleando la serie de Fourier [148, 149], funciones de Bessel [154, 155] y modelos en

el dominio del tiempo de las seales involucradas en la modulacin [156]. Al aplicar el control

PWM tambin a convertidores conmutados, esfuerzos para describir su naturaleza inherentemente

no lineal se encuentran en [160] aplicando la transformada de Laplace, en [65] aplicando la serie

de Taylor y en [85] aplicando la serie de Volterra.

2.3.1. Anlisis Matemtico

La mayora de los modelos matemticos de la modulacin PWM aplicada a convertidores

conmutados de potencia intenta evitar el empleo de las inherentes no linealidades que presenta,

pues es un bloque que funciona nicamente en conmutacin.

Para ello se emplean modelos promediados, que reducen la funcin de transferencia del

modulador a un factor de atenuacin directamente relacionado con la relacin de tiempo de

encendido frente al perodo de conmutacin. Tambin se aproxima su comportamiento por

desarrollos de series, que presentan mayor precisin cuantos ms trminos posea la serie, lo que

hace costoso en trminos de cmputo un modelo preciso.

A mayores de estos factores, si el modelo es promediado, desaparecen todos los efectos

relacionados con los desfases. Esto aade una dicultad en el caso de modelar convertidores en

paralelo que funcionan sincronizados (interleaving).

Para solventar estos problemas, se ha desarrollado un modelo del modulador empleando

relaciones matemticas. Este modelo matemtico no aporta per se informacin ms precisa que

los desarrollos en serie, pero permite crear un modelo de simulacin preciso y con unos requsitos

de cmputo exiguos.

En este apartado se elabora un anlisis matemtico para demostrar como obtener las seales

PWM, empleando algunas propiedades interesantes aportadas por la transformada de Laplace y la

funcin Pulso Unitaria de Heaviside [161].

El punto de partida para la creacin de un modelo del modulador es establecer cuales son las

seales de entrada necesarias, que aporta cada una de las mismas a la modulacin y que seales de

salida obtenemos del modulador.

Para la obtencin de una seal modulada en ancho de pulso genrica (u

PWM

(t)) son necesarias

dos seales: la portadora

_

u

portadora

(t)

_

y la referencia

_

u

re f erencia

(t)

_

. Como condicin para que

el proceso de modulacin sea vlido, lo que equivale a decir que la seal modulada contenga la

misma informacin que la seal de referencia, es condicin indispensable que la frecuencia de la

seal portadora sea mayor que la seal de referencia. En la mayora de los procesos de conversin

de energa mediante interruptores controlados la portadora tiene forma triangular, bien simtrica,

bien asimtrica (diente de sierra). La seal modulada puede ser de dos formas, a las cuales se les

denomina modulada normal

_

u

n

modulada

(t)

_

y su complementaria

_

u

c

modulada

(t)

_

.

De la representacin de las seales en la Fig. 2.3 se denen otras variables:

La seal modulada, de forma general, est denida como un tren de pulsos que tiene valor

mnimo cero y mximo igual a uno. Los valores mximo y mnimo nal de la seal se puede

63

Captulo 2. Mtodo de Modelado Aplicando ...

Figura 2.3: Seales de la modulacin PWM

cambiar con el aadido de dos variables: el valor mnimo que toma la seal, que se denota

por U

e-mnimo

y que toma generalmente el valor cero; y el valor mximo, que se denota por

u

e-mximo

(t).

El ancho de pulso de la seal modulada, al que se denomina t

delta

.

El atraso del pulso respecto al comienzo de la seal triangular (portadora), que se denomina

t

phi

.

La frecuencia constante de la seal portadora, que se denomina f

p

y su perodo, T

p

.

Por sencillez y sin renunciar a ninguna generalidad, se dene:

t

delta

= t

2

t

1

(2.1)

t

phi

= t

1

(2.2)

La funcin u

n

modulada

(t) en la Fig. 2.3 puede denirse en subintervalos de duracin T

p

como:

u

n

modulada

(t) =

_

_

_

u

e-mximo

(t) U

e-mnimo

0 < t <t

1

U

e-mnimo

t

1

< t < t

2

u

e-mximo

(t) U

e-mnimo

t

2

< t < T

p

(2.3)

y la funcin u

c

modulada

(t) en la Fig. 2.3 puede denirse en subintervalos de duracin T

p

como:

u

c

modulada

(t) =

_

_

_

U

e-mnimo

0 < t <t

1

u

e-mximo

(t) U

e-mnimo

t

1

< t < t

2

U

e-mnimo

t

2

< t < T

p

(2.4)

64

2.3 El modulador PWM

Si u

e-mximo

(t) = 1 yU

e-mnimo

= 0, entonces se denen las funciones moduladas unitarias

f

n

(t) = u

nunitaria

modulada

(t) =

_

_

_

1 0 < t <t

1

0 t

1

< t < t

2

1 t

2

< t < T

p

(2.5)

y

f

c

(t) = u

cunitaria

modulada

(t) =

_

_

_

0 0 <t <t

1

1 t

1

< t <t

2

0 t

2

< t < T

p

(2.6)

Por lo tanto, se pueden volver a denir las Ec. 2.3 y 2.4 como:

u

n

modulada

(t) =U

e-mnimo

+(u

e-mximo

(t) U

e-mnimo

) f

n

(t) (2.7)

u

c

modulada

(t) =U

e-mnimo

+(u

e-mximo

(t) U

e-mnimo

) f

c

(t) (2.8)

donde se aprecia que el valor de la funcin modulada depende realmente de la funcin modulada

unitaria.

Para obtener una mejor comprensin de las funciones de modulacin se le aplica la

transformada de Laplace denida por:

L{ f (t)} = F(s) =

Z

0

f (t) e

st

dt (2.9)

a las Ec. 2.5 y 2.6, teniendo en cuenta que la transformacin de una funcin periodica se lleva a

cabo con:

F(t) =

R

T

0

f (t) e

st

dt

1e

st

(2.10)

Aplicando la propiedad de la Ec. 2.10 a la seal en la Ec. 2.6

F

c

(s) =

R

T

p

0

f

c

(t) e

st

dt

1e

st

=

R

t

1

0

0 e

st

dt +

R

t

2

t

1

1 e

st

dt +

R

T

p

t

2

0 e

st

dt

1e

st

(2.11)

se obtiene la seal resultante

F

c

(s) =

e

st

1

e

st

2

s(1e

st

)

(2.12)

que se descompone en dos partes

F

c

(s) =

e

st

1

s(1e

st

)

e

st

2

s(1e

st

)

(2.13)

aplicando la transformada inversa de Laplace para volver al dominio del tiempo, se obtiene la

funcin Pulso Unitario de Heavisde, que se describe por:

U(t t

r

) =

_

0 t <t

r

1 t >t

r

(2.14)

65

Captulo 2. Mtodo de Modelado Aplicando ...

donde t

r

es el instante en que el pulso cambia a valor uno. Luego, la seal modulada en ancho de

pulso f

c

(t) se expresa como:

f

c

(t) =U(t t

1

) U(t t

2

) (2.15)

Llevando a cabo operaciones matemticas anlogas, la seal modulada en ancho de pulso f

n

(t)

se expresa como:

f

n

(t) = 1U(t t

1

) +U(t t

2

) (2.16)

y las seales que denen la seal modulada se representan en la Fig. 2.4.

Figura 2.4: Seales PWM unitarias y funciones Pulso Unitario de Heaviside

Para obtener un modelo matemtico ms genrico, las Ec. 2.15 y 2.16 pueden ser formuladas

usando lgebra de mdulos:

f

n

(t) = 1|U(t t

1

) U(t t

2

)| = 1|U(t t

2

) U(t t

1

)| (2.17)

f

c

(t) = |U(t t

1

) U(t t

2

)| = |U(t t

2

) U(t t

1

)| (2.18)

y debido a la naturaleza Booleana de las seales, tambin pueden ser formuladas con ayuda de la

funcin o-exclusiva:

f

n

(t) =U(t t

1

) U(t t

2

) (2.19)

f

c

(t) =U(t t

1

) U(t t

2

) (2.20)

La simulacin de un sistema dinmico con lazo de control requiere que se obtenga de un

tren de pulsos modulados. Esta secuencia de pulsos se puede expresar como la suma ordenada

de pulsos obtenidos en distintos instantes de tiempo, lo que se puede observar claramente en la

Fig. 2.5, donde u

tk

= U(t t

k

). Una de las condiciones para que la modulacin sea vlida es que

la frecuencia de la portadora debe ser mayor que la frecuencia de la seal de referencia. Basndose

en esta condicin se asumen las siguientes suposiciones a efectos prcticos:

66

2.3 El modulador PWM

para el ancho de pulso (t

delta

)

t

2

t

1

= t

4

t

3

t

4

t

3

= t

6

t

5

t

6

t

5

= t

8

t

7

para el atraso del pulso

_

t

phi

_

t

1

= T

c

t

3

T

c

t

3

= 2T

c

t

5

2T

c

t

5

= 3T

c

t

7

Figura 2.5: Secuencias de Pulsos Unitarios de Heaviside

Dos seales pulsantes, compuestas de una suma en serie de funciones Pulso Unitario de

Heaviside, se denen como:

u

impar

(t) = u

t1

u

t3

+u

t5

u

t7

+u

t(2n+1)

u

t(2n+3)

...

u

par

(t) = u

t2

u

t4

+u

t6

u

t8

+u

t(2n+2)

u

t(2n+4)

...

_

n = 4, 6, 8, 10... (2.21)

o bien por

u

impar

(t) =

n=1

(1)

n+1

U(t t

2n1

) (2.22)

u

par

(t) =

n=1

(1)

n+1

U(t t

2n

) (2.23)

y la funcin modulada f

c

(t) queda denida por

f

c

(t) = u

par

(t) u

impar

(t) (2.24)

con un perodo igual a la mitad del perodo de las seales pulsantes u

par

y u

impar

.

67

Captulo 2. Mtodo de Modelado Aplicando ...

2.3.2. Implementacin Software del Modelo

A partir de las deducciones matemticas se crea un modelo no lineal de comportamiento por

medio de MATLAB y SIMULINK [162]. Se ha escogido trabajar con estas dos herramientas por las

siguientes razones:

permiten de manera sencilla manipulaciones matemticas de variables, matrices y funciones

tienen bibliotecas de funciones de los propios programas y de toda la comunidad de usuarios

el mdulo SIMULINK posee bibliotecas de bloques a partir de las cuales es posible modelar

sistemas mediante un editor grco

se pueden crear bibliotecas de bloques a partir de la descripcin con bloques ya existentes

disponen de varios algoritmos de solucin de ecuaciones diferenciales, tanto para sistemas

continuos como para sistemas discretizados

gestionan de forma sencilla la creacin de grcos de las funciones en dos y tres dimensiones

existe la posibilidad de compilar los modelos en cdigo ejecutable, a travs de un compilador

C, para acelerar su simulacin

El primer objetivo es modelar un bloque de SIMULINK, que se denomina Generador Totalmente

Controlado con salida complementaria (GTCc), que acepte las entradas de la Tabla 2.1 y permita

obtener en sus salidas las funciones descritas por las Ec. 2.7 y 2.8.

Nombre Funcin o variable matemtica Valor

Ue u

e-mximo

(t)

valor mximo que toma la seal

modulada

Uminimo U

e-mnimo

valor mnimo (constante) que toma

la seal modulada

T T

p

perodo (constante) de la seal

portadora

Delta t

delta

ancho de pulso de la seal

modulada

Phi t

phi

atraso del pulso respecto al

comienzo de la seal triangular

(portadora)

PS

seal digital para modelar la

proteccin contra sobrecorriente,

presente en circuitos de control

PWM comerciales

Tabla 2.1: Entradas del GTCc

Para modelar un sistema como el descrito por la Ec. 2.24 se comienza por un bloque generador

de una seal cuadrada de frecuencia constante y amplitud igual a uno, a la que denominaremos

f

0

, que modela las seales pulsantes u

par

y u

impar

sin ningn atraso temporal. A esta seal se la

hace pasar a travs de dos bloques Variable Transport Delay (VTD). Los bloques VTD tienen dos

68

2.3 El modulador PWM

entradas: la primera entrada recibe la seal que va a ser atrasada y la segunda entrada necesita el

valor, en segundos, del atraso que se le aplicar a la seal de la primera entrada.

Para crear la seal modulada, el primer VTD tiene por entrada la seal f

0

y por atraso el valor

t

1

. De la Ec. 2.2 se sabe que t

1

= t

phi

. La seal que se obtiene de este primer bloque corresponde

con la u

impar

de la Fig. 2.5. El segundo VTD tiene por entrada la seal f

0

y por atraso el valor de

t

2

. De la Ec. 2.1 se sabe que t

2

= t

delta

+t

1

= t

delta

+t

phi

. La seal que se obtiene de este segundo

bloque corresponde con la u

par

de la Fig. 2.5. Estas dos seales son las entradas de una funcin

O-exclusiva, para obtener en la salida la funcin f

c

(t).

El modelo resultante de SIMULINK para simular el primer paso del proceso de modulacin se

muestra en la Fig. 2.6.

La Constante 2 determina el atraso de la seal de salida.

La Constante 3 determina el ancho de pulso.

El Atraso Variable 1 es el que genera el atraso de la seal de salida.

El Atraso Variable 2 es el que genera el ancho de pulso de la seal de salida.

Variable Time

Delay 2

Variable Time

Delay 1

z

1

Unit Delay

Suma 2

Suma

Scope

XOR

Operador

Lgico

tdelta

Constante 3

Ancho de Pulso

tphi

Constante 2

Atraso

1

Constante 1

Figura 2.6: Modelo de SIMULINK del Generador Totalmente Controlable (sin

encapsular)

Este modelo se encapsula en un bloque al que se denomina Generador Totalmente Controlado

(GTC), y es el primer componente de una biblioteca de bloques para simular convertidores

conmutados de potencia. Aunque est incompleto frente a todas las posibilidades que se implantan

en apartados posteriores, este modulador posee todos los fundamentos matemticos y funcionales

del modelo.

Cabe sealar que el comportamiento de GTC no ser correcto cuando la seal de referencia

tenga cambios bruscos en las inmediaciones del instante en que la referencia supere el valor de

la moduladora, lo que se traduce en un serie de oscilaciones caticas de la seal modulada. Este

fenmeno, detectado a principios de los aos 70, hizo que los circuitos de control tuviesen la salida

del comparador (modulador) aplicada a la entrada S (set) de un biestable R-S, de tal forma que

nicamente el primer cambio activara la salida y slo se desactivara cuando se hubiese cumplido el

ciclo T

p

de conmutacin. Un claro ejemplo de esta solucin se encuentra en los circuitos integrados

SG1524 y derivados.

69

Captulo 2. Mtodo de Modelado Aplicando ...

Para que la salida del modulador corresponda con las Ec. 2.7 y 2.8 es necesario aadir los

bloques que completen la funcionalidad, los cuales se muestran en la Fig. 2.7, y que se analiza

desde el esquema de SIMULINK.

Comenzando por la izquierda del modelo, se encuentran las entradas Delta y Phi, que ahora

pasan por dos bloques de saturacin. Estos bloques tiene por misin evitar que ambas seales

excedan de los valores correctos de funcionamiento, ya que ambas deben cumplir:

0 < t

delta

< T

p

(2.25)

0 <t

phi

< T

p

(2.26)

Estas seales entran como variable de control de dos VTDs (aqui denominados Atraso Variable

1 y 2), los cuales se encargan de atrasar la seal f

0

para obtener las seales u

impar

y u

par

. Estas

dos seales vuelven a pasar a travs de otros dos VTDs (denominados Atraso Variable 3 y 4),

cuya seal de control es un 0,5 % del perodo T

p

. Las seales provenientes de los atrasos impares

generan una seal pulso de Dirac que activa la salida Q (desactiva la salida !Q) del biestable RS y

las seales provenientes de los atrasos impares generan el pulso que desactiva la salida Q (activa

la salida !Q).

El biestable RS necesita una seal que le aporte ancos ascendentes, para permitir la evolucin

del mismo segun el estado de sus entradas. Esta seal proviene de otro generador de ondas

cuadradas, pero de frecuencia mil veces mayor que la de la portadora.

En las salidas del biestable se obtienen las funciones f

c

(t) y f

n

(t). Para nalmente obtener las

moduladas las salidas del biestable pasan por un conjunto de bloques que implantan las ecuaciones

Ec. 2.7 y 2.8.

Por ltimo, la entrada PS (proteccin de sobrecorriente) permite, de forma asncrona, desactivar

ambas salidas del modulador. Su objetivo es presentar la funcionalidad de proteccin por

sobrecorriente, o tambin la de permitir el apagado del modulador desde un sistema de control

externo. Cuando toma el valor uno, provoca la puesta a cero de la salida Q del biestable y la puesta

a cero de las salidas del modulador.

2.3.3. Ensayos del Modelo del Modulador PWM

Para comprobar que tanto el desarrollo matemtico como la implantacin funcional en el

modelo de SIMULINK son correctas se llevan a cabo una serie de pruebas cuyos resultados se

muestran en el apartado 3.1 en la pgina 94 y posteriores.

70

2

.

3

E

l

m

o

d

u

l

a

d

o

r

P

W

M

Este es el modelo del Generador Totalmente Encapsulado con salida Complementaria

listo para enmascarar en la libreria lib400.mdl

Las variables necesarias para la mascara son:

T = periodo de oscilacion del sistema

T05 = el cinco por mil del periodo de oscilacion del sistema

TM = 0.001 * T, muestreo del flip flop

SAT = SAT1 = el 99,95% del periodo de oscilacion del sistema

2

Uc

1

Ug

Uminimo

Uminimo

Suma 7

Suma 6

Suma 5

Suma 4

Suma 3

Suma 2

Suma 1

Suma

Saturation1

Saturation

S

R

Q

!Q

SR

FlipFlop

Producto

1

Producto

XOR

Operador

Lgico1

XOR

Operador

Lgico

z

1

Atraso unidad 1

z

1

Atraso unidad

Atraso Variable 4

Atraso Variable 3

Atraso Variable 2

Atraso Variable 1

T05

0,5% del Periodo

1

Constante 3

1

Constante 2

1

Constante 1

4

PS

3

Phi

2

Delta

1

Ue

F

i

g

u

r

a

2

.

7

:

M

o

d

e

l

o

c

o

m

p

l

e

t

o

d

e

S

I

M

U

L

I

N

K

d

e

l

G

e

n

e

r

a

d

o

r

T

o

t

a

l

m

e

n

t

e

C

o

n

t

r

o

l

a

d

o

c

o

n

s

a

l

i

d

a

c

o

m

p

l

e

m

e

n

t

a

r

i

a

(

G

T

C

c

)

7

1

Captulo 2. Mtodo de Modelado Aplicando ...

2.4. El Filtro de Salida del Convertidor Reductor

De la observacin de la etapa de salida de los convertidores de la Fig. 2.2 se aprecia que

todos son circuitos LCR +D, lo que constituye un ltro paso bajo destinado a suavizar los

pulsos de tensin provenientes de la fuente de entrada y el interruptor controlado. Es, por lo tanto,

parte fundamental de la dinmica que presenta el convertidor. Para llevar a cabo el modelado se

comenzar con el ltro de salida de una topologa reductora, que se representa en la Fig. 2.8 con

los elementos parsitos ms importantes de sus componentes.

Figura 2.8: Filtro de salida de un convertidor reductor con componentes parsitos

Si bien el ltro de salida, atenindonos al concepto clsico de ltro pasivo, est integrado por

la inductancia, el condensador y la carga, se incluye en el mismo la presencia del diodo D. La

presencia de este diodo permite modelar la respuesta del ltro del convertidor reductor cuando

trabaja en modo discontinuo, pues el GTCc no modela el comportamiento elctrico del conjunto

fuente de tensin de entrada, transistor y diodo. El GTCc slamente aporta la forma de la onda de

tensin aplicada a la entrada del ltro.

Es habitual recurrir a modelos de la etapa de potencia y del ltro de salida cuya composicin

acomoda componentes no lineales (diodo, transistor) y lineales (inductancia, condensador) o no

en funcin de la descripcin funcional del convertidor. Esto conlleva que, al crear el modelo

matemtico de anlisis y el de simulacin, el comportamiento de los componentes no lineales

se vea encapsulado en el comportamiento de tensiones y corrientes de forma no lineal por los

elementos lineales. Ejemplos de esta clase de anlisis se encuentran en [5153, 99].

2.4.1. Anlisis Matemtico

Del circuito de la Fig. 2.8 se obtiene su funcin de transferencia lineal (ver desarrollo

en B.1.1 en la pgina 171) :

F(S) =

U

s

(s)

U

e

(s)

=

R

S

+sCR

S

R

C

R

S

+R

L

+s(L+C(R

L

R

C

+R

L

R

S

+R

C

R

S

)) +s

2

LC(R

S

+R

C

)

(2.27)

Esta ecuacin, debido a que la resistencia de prdidas de la inductancia presenta menor efecto

que la resistencia equivalente serie del condensador, se suele aplicar con la forma simplicada:

72

2.4 El Filtro de Salida del Convertidor Reductor

F(S) =

U

s

(s)

U

e

(s)

=

R

S

+sCR

S

R

C

R

S

+s(L+CR

C

R

S

) +s

2

LC(R

S

+R

C

)

(2.28)

El modelo lineal del espacio de estados de este circuito es (ver desarrollo en B.1.2 en la

pgina 173):

_

di

L

(t)

dt

du

C

(t)

dt

_

=

_

R

C

R

S

+R

C

R

L

+R

L

R

S

L(R

C

+R

S

)

R

S

L(R

C

+R

S

)

R

S

C(R

C

+R

S

)

1

C(R

C

+R

S

)

_

_

i

L

(t)

u

C

(t)

_

+

_

1

L

0

_

u

E

(t) (2.29)

u

S

(t) =

_

R

C

R

S

R

C

+R

S

R

S

R

C

+R

S

_

_

i

L

(t)

u

C

(t)

_

(2.30)

La presencia del diodo en el ltro de salida hace que las caractersticas dinmicas del mismo

se vean afectadas, evitando que la corriente por la inductancia L sea negativa cuando la tensin

aplicada a la entrada del ltro es cero. Este efecto se modelar en el siguiente apartado mediante

integradores cuya salida est limitada entre dos valores: un mnimo y un mximo.

2.4.2. Implementacin Software del Modelo

Para modelar en SIMULINK el ltro de salida vamos a proceder a crear una serie de bloques,

cada vez ms complejos y precisos, a los que se denominan genericamente Filtros de Salida del

Reductor (F*SR), que aceptan las entradas de la Tabla 2.2 y permiten obtener en sus salidas las

variables de estado descritas por las Ec. 2.29 y 2.30.

Nombre Funcin o variable matemtica Valor

Ug u

e

(t)

valor que toma la seal modulada a

la entrada del ltro

L L valor de la inductancia del ltro

RL R

L

valor de la resistencia de prdidas

de la inductancia del ltro

IL0 i

L

(0) corriente inicial por la inductancia

C C valor del condensador del ltro

RC R

C

valor de la resistencia equivalente

serie del condensador del ltro

UC0 u

C

(0) tensin inicial en el condensador

RS R

S

valor de la resistencia de salida del

ltro

Tabla 2.2: Entradas de los bloques FSR

El primer bloque que se elabora es una descripcin en variables de estado aplicando los bloques

lineales existentes en la biblioteca de SIMULINK, al que se denomina FSR. Este modelo del sistema

73

Captulo 2. Mtodo de Modelado Aplicando ...

Modelo del Filtro de Salida

en Espacio de Estados con Condiciones Iniciales

3

Uc

2

IL

1

Us

x = Ax+Bu

y = Cx+Du

StateSpace

Demux

Demux

1

Ug

Figura 2.9: Modelo de SIMULINK del Filtro de Salida del Reductor (sin encapsular)

permite, fcil y rpidamente, obtener la funcin de transferencia lineal del sistema. El resultado se

muestra en la Fig. 2.9.

El FSR no presenta ninguna de las caractersitcas no lineales del ltro real. Para obtener un

sistema de este tipo se recurre a crear el modelo empleando elementos que modelan los diferentes

coecientes de las matrices de las Ec. 2.29 y 2.30 e integradores. Los integradores de la biblioteca

de SIMULINK presentan la posibilidad de limitar su salida entre dos valores mximo y mnimo.

Esto hace factible que la corriente por la inductancia no sea nunca negativa, que es el efecto que

provoca el diodo. Tambin es posible establecer que la tensin presente en el condensador de

salida no supere valores mximos y mnimos. El modelo resultante, denominado Filtro No Lineal

de Salida del Reductor (FNLSR) se muestra en la Fig. 2.10.

Este es el modelo no lineal en el espacio de estados

del Filtro de Salida del Convertidor Reductor

3

Uc

2

IL

1

Us

Suma2

Suma1

Suma

1

s

Integrador1

1

s

Integrador

C12

Gain9

C11

Gain8

B21

Gain6

B11

Gain4

A22

Gain3

A21

Gain2

D11

Gain10

A12

Gain1

A11

Gain

1

Ug

Figura 2.10: Modelo de SIMULINK del Filtro No Lineal de Salida del Reductor (sin

encapsular)

Para este nuevo bloque aparecen dos entradas ms, que se muestran en la Tabla 2.3. Sirven

74

2.4 El Filtro de Salida del Convertidor Reductor

para establecer los lmites mximos de los integradores. La primera representa la corriente de

saturacin de la inductancia. Modela, de manera simple, el comportamiento no lineal que presenta

una inductancia real cuando la corriente que circula por la misma provoca una saturacin del ujo

magntico. La segunda representa el valor de la tensin mxima del condensador. No modela

ningn fenmeno fsico no lineal presente en un condensador, aunque puede servir para modelar la

proteccin por sobretensin existente en paralelo con la resistencia de carga R

S

, tal como un surge

arrestor.

Nombre Funcin o variable matemtica Valor

ILMAX corriente mxima por la inductancia

UCMAX tensin mxima en el condensador

Tabla 2.3: Entradas adicionales para el bloque FNLSR

Si bien con estos dos bloques es factible obtener tanto diagramas de Bode, de respuesta al

primer armnico y transitorios (arranque suave, cambios de carga), no lo son de forma simple,

ya que la variacin de cualesquiera de los parmetros requiere detener la simulacin, guardar el

estado de las variables, cambiar el valor de los parmetros y continuar la simulacin. Con objeto

de remediar esta situacin se crea un nuevo modelo del ltro de salida, siguiendo un desarrollo

anlogo al anterior, pero dejando esta vez la variable R

S

como una entrada al bloque de SIMULINK,

de tal forma que para cambiar la respuesta del mismo slo sea necesario establecer la variacin de

la funcin que modele la resistencia de salida.

De esta variacin del ltro se han implantado dos versiones: la primera es el Filtro Variable

de Salida del Reductor (FVSR), que es totalmente lineal, y la segunda es el Filtro Variable No

Lineal de Salida del Reductor (FVNLSR), que presenta las mismas no linealidades del FNLSR. El

modelo de bloques del primero se muestra en la Fig. 2.11 y el segundo en la Fig. 2.12.

2.4.3. Ensayos de los Modelos de los FSR

Para comprobar que tanto el desarrollo matemtico como la implantacin funcional en el

modelo de SIMULINK de los distintos F*SR son correctas se llevan a cabo una serie de pruebas

cuyos resultados se muestran en el apartado 3.2 en la pgina 119 y posteriores.

75

C

a

p

t

u

l

o

2

.

M

t

o

d

o

d

e

M

o

d

e

l

a

d

o

A

p

l

i

c

a

n

d

o

.

.

.

Modelo del Filtro Variable de Salida

del Convertidor Reductor para

Encapsular

3

Uc

2

IL

1

Us

suma4

suma3

suma2

suma1

V2

V1

RC

RC

L

L

K3

K3

K2

K2

K1

K1

1

s

Integrador1

1

s

Integrador

C12

C11

C

C

B11

B11

A22

A21

A12

A113

A112

A111

A11

2

RS

1

Ug

RC

RC

RS/(RC+RS)

RS/(RC+RS)

IL

IL

IL

IL

IL

UC

UC

UC

UC

Ug

F

i

g

u

r

a

2

.

1

1

:

M

o

d

e

l

o

d

e

S

I

M

U

L

I

N

K

d

e

l

F

i

l

t

r

o

V

a

r

i

a

b

l

e

d

e

S

a

l

i

d

a

d

e

l

R

e

d

u

c

t

o

r

(

s

i

n

e

n

c

a

p

s

u

l

a

r

)

7

6

2

.

4

E

l

F

i

l

t

r

o

d

e

S

a

l

i

d

a

d

e

l

C

o

n

v

e

r

t

i

d

o

r

R

e

d

u

c

t

o

r

Modelo del Filtro Variable No Lineal de Salida

del Convertidor Reductor para

Encapsular

3

Uc

2

IL

1

Us

suma4

suma3

suma2

suma1

V2

V1

RC

RC

L

L

K3

K3

K2

K2

K1

K1

1

s

Integrador1

1

s

Integrador

C12

C11

C

C

B11

B11

A22

A21

A12

A113

A112

A111

A11

2

RS

1

Ug

RC

RC

RS/(RC+RS)

RS/(RC+RS)

IL

IL

IL

IL

IL

UC

UC

UC

UC

Ug

F

i

g

u

r

a

2

.

1

2

:

M

o

d

e

l

o

d

e

S

I

M

U

L

I

N

K

d

e

l

F

i

l

t

r

o

V

a

r

i

a

b

l

e

N

o

L

i

n

e

a

l

d

e

S

a

l

i

d

a

d

e

l

R

e

d

u

c

t

o

r

(

s

i

n

e

n

c

a

p

s

u

l

a

r

)

7

7

Captulo 2. Mtodo de Modelado Aplicando ...

2.5. El Filtro de Salida del Convertidor Elevador

Al igual que con el ltros de salida del reductor, de la observacin de la etapa de salida de los

convertidores de la Fig. 2.2, se aprecia que la disposicin topolgica de L+D+CR constituye un

ltro paso bajo destinado a suavizar los pulsos de corriente provenientes de la fuente de entrada,

la inductancia L y el interruptor controlado. Es, por lo tanto, parte fundamental de la dinmica que

presenta el convertidor. Para llevar a cabo el modelado se comenzar con el ltro de salida de una

topologa elevadora, que se representa en la Fig. 2.13 con los elementos parsitos ms importantes

de sus componentes.

Figura 2.13: Filtro de salida de un convertidor elevador con componentes parsitos

En el caso del convertidor reductor los elementos pasivos conforman un ltro pasivo de salida,

cuya topologa no cambia a lo largo de la secuencia de conmutacin. En el caso del convertidor

elevador la topologa se altera por la presencia de los interruptores semiconductores, dando paso a

un modelo no lineal, cuyo anlisis se aborda en B.7 en la pgina 186.

2.5.1. Anlisis Matemtico

Del circuito de la Fig. 2.13 y del anlisis en B.7 en la pgina 186, se obtiene el modelo no lineal

del espacio de estados, para el cual se denen

f

i

L

(t) =

_

0 i

L

(t) 0

1 i

L

(t) > 0

(2.31)

f

S

(t) =

_

0 Si interruptor cerrado

1 Si interruptor abierto

(2.32)

Lo que permite expresar las matrices del espacio de estados para el convertidor elevador como:

_

di

L

(t)

dt

du

C

(t)

dt

_

=

_

_

f

i

L

(t)

_

f

S

(t)

R

C

R

S

L(R

C

+R

S

)

R

L

L

_

f

S

(t) f

i

L

(t)

_

R

S

L(R

C

+R

S

)

_

f

S

(t) f

i

L

(t)

_

R

S

C(R

C

+R

S

)

_

1

C(R

C

+R

S

)

_

_

_

i

L

(t)

u

C

(t)

_

+

+

_

f

i

L

(t)

1

L

0

_

u

E

(t)

(2.33)

78

2.5 El Filtro de Salida del Convertidor Elevador

u

S

(t) =

_

f

S

(t) f

i

L

(t)

_

R

C

R

S

R

C

+R

S

_

R

S

R

C

+R

S

_

_

i

L

(t)

u

C

(t)

_

(2.34)

2.5.2. Implementacin Software del Modelo

Del mismo modo que se implanta el modelo en SIMULINK del ltro de salida del reductor,

vamos a proceder a crear un bloque, esta vez centrndonos en la capacidad de ser variable y no

lineal, al que denominamos Filtro Variable No Lineal de Salida del Elevador (FVNLSE), que

acepta las entradas de la Tabla 2.4 y permite obtener en sus salidas las variables de estado descritas

por las Ec. 2.33 y 2.34.

Nombre Funcin o variable matemtica Valor

Ug f

S

(t)

valor que toma la seal que modela

el interruptor controlado

L L valor de la inductancia del ltro

RL R

L

valor de la resistencia de prdidas

de la inductancia del ltro

IL0 i

L

(0) corriente inicial por la inductancia

ILMAX - corriente mxima por la inductancia

C C valor del condensador del ltro

RC R

C

valor de la resistencia equivalente

serie del condensador del ltro

UC0 u

C

(0) tensin inicial en el condensador

UCMAX - tensin mxima en el condensador

RS R

S

valor de la resistencia de salida del

ltro

Tabla 2.4: Entradas del bloque FVNLSE

En el caso del convertidor elevador, la corriente por la inductancia slo puede venir acotada

por dos valores. El primero es el que presenta el componente magntico cuando se satura, lo que

representa un mximo de corriente. El segundo es el valor cero, ya que la presencia del diodo en

el ltro hace imposible la circulacin de corriente desde el condensador a la fuente de entrada a

travs de la inductancia.

Los integradores de la biblioteca de SIMULINK presentan la posibilidad de limitar su salida

entre dos valores mximo y mnimo. Esto hace factible modelar que la corriente por la inductancia

no sea nunca negativa, que es el efecto que provoca el diodo. Tambin es posible establecer que la

tensin presente en el condensador de salida no supere valores mximos y mnimos.

Con este bloque es factible obtener tanto diagramas de Bode, de respuesta al primer armnico

y transitorios (arranque suave, cambios de carga) de forma simple. Esto se consigue dejando, tal

como se ha hecho con el ltro de salida del reductor, la variable R

S

como una entrada al bloque de

SIMULINK, de tal forma que para cambiar la respuesta del mismo slo sea necesario establecer la

79

Captulo 2. Mtodo de Modelado Aplicando ...

variacin de la funcin que modele la resistencia de salida. El modelo de bloques del FVNLSE se

muestra en la Fig. 2.14.

M

o

d

e

l

o

d

e

l

F

i

l

t

r

o

V

a

r

i

a

b

l

e

N

o

L

i

n

e

a

l

d

e

S

a

l

i

d

a

d

e

l

C

o

n

v

e

r

t

i

d

o

r

E

l

e

v

a

d

o

r

p

a

r

a

E

n

c

a

p

s

u

l

a

r

3

U

c

2

I

L 1

U

s

s

u

m

a

4

s

u

m

a

3

s

u

m

a

2

s

u

m

a

1

V

2

V

1

>

=

R

e

l

a

t

i

o

n

a

l

O

p

e

r

a

t

o

r

R

C

R

C

LL

B

1

1

K

B

1

1

K

2

K

2

K

1

K

1

1s

I

n

t

e

g

r

a

d

o

r

1

1s

I

n

t

e

g

r

a

d

o

r

0

C

e

r

o

C

1

2

C

1

1

CC

B

1

A

2

2

A

2

1

A

1

2

A

1

1

1

A

1

1

3

R

S

2

U

g1

U

e

R

C

R

C

R

S

/

(

R

C

+

R

S

)

R

S

/

(

R

C

+

R

S

)

R

S

/

(

R

C

+

R

S

)

R

S

/

(

R

C

+

R

S

)

I

L

I

L

I

L

I

L

I

L

U

C

U

C

U

C

U

C

F

I

L

F

I

L

U

g

Figura 2.14: Modelo de SIMULINK del Filtro Variable de Salida del Elevador (sin

encapsular)

El proceso de modelado de la topologa elevadora se presenta como punto de partida de las

lineas futuras de investigacin, que pueden dar lugar a la comprobacin funcional del modelo y su

aplicacin en paralelizado.

80

2.6 Los Circuitos Compensadores

2.6. Los Circuitos Compensadores

Para completar el desarrollo del modelo es necesario crear bloques que permitan compensar la

dinmica de la etapa de potencia (modelado por el conjunto de GTCc y F*SR). Con este objetivo se

han elaborado un conjunto de bloques que modelan diversos circuitos compensadores, obtenidos de

aplicaciones existentes en la literatura tcnica. No existe una nomenclatura especca para estos

circuitos, por lo que se ha adoptado un orden de menor a mayor nmero de componentes que

integran la red de compensacin.

2.6.1. Circuito Compensador Tipo I

La primera topologa que se modela se representa en la Fig. 2.15.

Figura 2.15: Compensador Tipo I

Su funcin de transferencia lineal viene dada por:

H(s) =

U

S

(s)

U

M

(s)

=

1+sR

2

C

2

s(C

1

+C

2

)R

1

+s

2

C

1

C

2

R

1

R

2

(2.35)

y su modelo en el espacio de estados lineal por:

_

du

C

1

(t)

dt

du

C

2

(t)

dt

_

=

_

1

R

2

C

1

1

R

2

C

1

1

R

2

C

2

1

R

2

C

2

_

_

u

C

1

(t)

u

C

2

(t)

_

+

_

1

R

1

C

1

1

R

1

C

1

0 0

__

u

e

(t)

u

re f

(t)

_

(2.36)

u

S

(t) =

_

1 0

_

u

C

1

(t)

u

C

2

(t)

_

+

_

0 1

_

u

e

(t)

u

re f

(t)

_

(2.37)

Para modelar en SIMULINK el compensador se crean dos bloques a los que se denominan

Compensador I (Comp1) y Compensador No Lineal I (CompNL1), que acepten las entradas de la

Tabla 2.5 y permitan obtener en sus salidas las variables descritas por las Ec. 2.36 y 2.37.

81

Captulo 2. Mtodo de Modelado Aplicando ...

Nombre Funcin o variable matemtica Valor

Um K

s

u

s

(t)

valor que toma la muestra de la

tensin de salida del convertidor a

la entrada del circuito compensador

Uref u

re f

(t) valor de la tensin de referencia

C1, C2, R1, R2 C

1

,C

2

, R

1

, R

2

valor de los condensadores y

resistores del circuito compensador

UC10, UC20 u

C

1

(t), u

C

2

(t) tensin inicial en los condensadores

Tabla 2.5: Entradas comunes de los bloques Comp1 y CompNL1

El primer bloque (Comp1) es una descripcin en el espacio de variables de estado aplicando los

bloques lineales existentes en la biblioteca de SIMULINK. Este modelo del sistema permite, fcil

y rpidamente, obtener la funcin de transferencia lineal del sistema y simular su comportamiento

en zonas de trabajo lineal. El bloque resultante se muestra en la Fig. 2.16.

Modelo del Espacio de Estados del Compensador Tipo 1

del Convertidor Reductor

3

Uc2

2

Uc1

1

Uctrl

x = Ax+Bu

y = Cx+Du

StateSpace

Mux Demux

Demux

2

Uref

1

Um

Figura 2.16: Modelo de SIMULINK del Compensador Tipo I (sin encapsular)

El Comp1 no presenta ninguna de las caractersitcas no lineales del compensador real.

Para modelarlas en el sistema se recurre nuevamente a elementos que modelan los diferentes

coecientes de las matrices de las Ec. 2.36 y 2.37 e integradores. Esto hace factible que las

tensiones en el condensador no superen nunca los valores mximos que acepta el circuito real. El

modelo resultante, denominado Compensador No Lineal I (CompNL1) se muestra en la Fig. 2.17.

Para este bloque las dos nuevas entradas, que se muestran en la Tabla 2.6 permiten modelar los

valores que producen no linealidades debido a las limitaciones fsicas de los circuitos electrnicos.

Con nimo de demostrar el correcto funcionamiento del modelo de SIMULINK se llevan a cabo

ensayos cuyos resultados se muestran en el apartado 3.3 en la pgina 126.

82

2.6 Los Circuitos Compensadores

3

Uc2

2

Uc1

1

Uctrl

Suma2

Suma1

Suma

Saturation

1

s

Integrador1

1

s

Integrador

C11

Gain8

B12

Gain5

B11

Gain4

A22

Gain3

A21

Gain2

D12

Gain11

A12

Gain1

A11

Gain

2

Uref

1

Um

Figura 2.17: Modelo de SIMULINK del Compensador No Lineal Tipo I (sin

encapsular)

Nombre Funcin o variable matemtica Valor

VDC

tensin de alimentacin del circuito

compensador

EAmpMax, EAmpMin

tensin mxima y mnima que se

puede obtener de la salida del

amplicador de error del circuito

compensador

Tabla 2.6: Entradas adicionales para el bloque CompNL1

83

Captulo 2. Mtodo de Modelado Aplicando ...

2.6.2. Circuito Compensador Tipo II

La segunda topologa que se modela se representa en la Fig. 2.18.

Figura 2.18: Compensador Tipo II

Su funcin de transferencia viene dada por:

H(s) =

U

S

(s)

U

M

(s)

=

U

s

(s)

U

e

(s)

=

C

1

C

2

R

2

R

3

s

2

+(C

1

R

2

+C

2

R

3

)s +1

C

1

C

2

R

1

R

2

s

2

+(C

2

R

2

+C

2

R

1

)s

(2.38)

y su modelo en el espacio de estados por:

_

du

C

1

(t)

dt

du

C

2

(t)

dt

_

=

_

_

1

R

2

C

1

+

1

R

1

C

1

_

0

1

R

1

C

2

0

_

_

u

C

1

(t)

u

C

2

(t)

_

+

_

1

R

1

C

1

1

R

1

C

1

1

R

1

C

2

_

1

R

1

C

2

+

1

R

4

C

2

_

_

_

u

e

(t)

u

re f

(t)

_

(2.39)

u

s

(t) =

_

R

3

R

1

1

_

_

u

C

1

(t)

u

C

2

(t)

_

+

_

R

3

R

1

1+

R

3

R

1

+

R

3

R

4

_

_

u

e

(t)

u

re f

(t)

_

(2.40)

Para modelar en SIMULINK el compensador se crean dos bloques a los que se denominan

Compensador II (Comp2) y Compensador No Lineal II (CompNL2), que acepten las entradas de

la Tabla 2.7 y permitan obtener en sus salidas las variables descritas por las Ec. 2.39 y 2.40.

Ntese que la resistencia R

5

no inuye en el modelo, pero su presencia suele ser necesaria

para compensar la dinmica del amplicador de error y su valor suele venir recomendado por

el fabricante a partir de una frmula emprica. El primer bloque (Comp2) es una descripcin

en el espacio de variables de estado aplicando los bloques lineales existentes en la biblioteca

de SIMULINK. Este modelo del sistema permite, fcil y rpidamente, obtener la funcin de

84

2.6 Los Circuitos Compensadores

Nombre Funcin o variable matemtica Valor

Um K

s

u

s

(t)

valor que toma la muestra de la

tensin de salida del convertidor a

la entrada del circuito compensador

Uref u

re f

(t) valor de la tensin de referencia

C1, C2, R1, R2, R3, R4 C

1

,C

2

, R

1

, R

2

, R

3

, R

4

valor de los condensadores y

resistores del circuito compensador

UC10, UC20 u

C

1

(t), u

C

2

(t) tensin inicial en los condensadores

Tabla 2.7: Entradas comunes de los bloques Comp2 y CompNL2

transferencia lineal del sistema y simular su comportamiento en zonas de trabajo lineal. El bloque

resultante es similar internamente al Comp1 y se muestra en la Fig. 2.16 en la pgina 82.

El Comp2 no presenta ninguna de las caractersitcas no lineales del compensador real.

Para modelarlas en el sistema se recurre nuevamente a elementos que modelan los diferentes

coecientes de las matrices de las Ec. 2.39 y 2.40 e integradores. Los integradores de la biblioteca

de SIMULINK presentan la posibilidad de limitar su salida entre dos valores mximo y mnimo.

Esto hace factible que las tensiones en el condensador no superen nunca los valores mximos que

acepta el circuito real. El modelo resultante, denominado Compensador No Lineal II (CompNL2)

se muestra en la Fig. 2.19.

Para este nuevo bloque aparecen dos entradas ms, que se muestran en la Tabla 2.8. Sirven para

establecer los lmites mximos de los integradores y de la saturacin existente a la salida. Estos

valores permiten modelar los valores que producen no linealidades debido a las limitaciones fsicas

de los circuitos electrnicos.

Nombre Funcin o variable matemtica Valor

VDC

tensin de alimentacin del circuito

compensador

EAmpMax, EAmpMin

tensin mxima y mnima que se

puede obtener de la salida del

amplicador de error del circuito

compensador

Tabla 2.8: Entradas adicionales para el bloque CompNL2

Con nimo de demostrar el correcto funcionamiento del modelo de SIMULINK se llevan a cabo

ensayos cuyos resultados se muestran en el apartado en la pgina 128

85

Captulo 2. Mtodo de Modelado Aplicando ...

3

Uc2

2

Uc1

1

Uctrl

Suma2

Suma1

Suma

Saturation

1

s

Integrador1

1

s

Integrador

C12

Gain9

C11

Gain8

B22

Gain7

B21

Gain6

B12

Gain5

B11

Gain4

A22

Gain3

A21

Gain2

D12

Gain11

D11

Gain10

A12

Gain1

A11

Gain

2

Uref

1

Um

Figura 2.19: Modelo de SIMULINK del Compensador No Lineal Tipo II (sin

encapsular)

86

2.7 Paralelizado de Convertidores Reductores

2.7. Paralelizado de Convertidores Reductores

2.7.1. El Filtro de Salida

En el caso de tener dos o ms convertidores reductores trabajando en paralelo, el modelo del

ltro de salida aumenta su complejidad. De la observacin del circuito de N convertidores en

paralelo, se aprecia nuevamente que todos son circuitos LCR+D. Sigue siendo, por lo tanto, parte

fundamental de la dinmica que presenta el conjunto de convertidores.

Figura 2.20: Filtro de salida de N convertidores reductores con componentes

parsitos

2.7.2. Anlisis Matemtico

De este circuito se obtiene el modelo del espacio de estados (ver el desarrollo matemtico en

el apartado B.6 en la pgina 183), que viene descrito por las siguientes matrices:

B =

_

_

1

L

1

0 0 0

0

1

L

2

0 0

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

0 0

1

L

N

0

0 0 0 0 0

_

_

(2.41)

C =

_

R

C

N

R

S

R

C

N

+R

S

R

C

N

R

S

R

C

N

+R

S

R

C

N

R

S

R

C

N

+R

S

R

S

R

C

N

+R

S

_

(2.42)

87

Captulo 2. Mtodo de Modelado Aplicando ...

A =

_

R

C

N

(R

S

+R

L

1

)+R

L

1

R

S

L

1(R

C

N

+R

S)

R

C

N

R

S

L

1(R

C

N

+R

S)

...

R

C

N

R

S

L

1(R

C

N

+R

S)

R

S

L

1(R

C

N

+R

S)

R

C

N

R

S

L

2(R

C

N

+R

S)

R

C

N

(R

S

+R

L

2

)+R

L

2

R

S

L

2(R

C

N

+R

S)

...

R

C

N

R

S

L

2(R

C

N

+R

S)

R

S

L

2(R

C

N

+R

S)

.

.

.

.

.

.

.

.

.

R

C

N

R

S

L

N(R

C

N

+R

S)

R

C

N

R

S

L

N(R

C

N

+R

S)

...

R

C

N

(R

S

+R

L

N

)+R

L

N

R

S

L

N(R

C

N

+R

S)

R

S

L

N(R

C

N

+R

S)

R

S

C

N(R

C

N

+R

S)

R

S

C

N(R

C

N

+R

S)

...

R

S

C

N(R

C

N

+R

S)

1

C

N

(R

C

+R

S

)

_

_

(2.43)

Nuevamente hay que destacar que la presencia de los diodos en el ltro de salida de N

convertidores hace que las caractersticas dinmicas del mismo se vean afectadas, evitando que las

corriente por la inductancias L

1,2...N

sean negativas. Es tambin factible establecer que la tensin

en el condensador equivalente C

N

slo puede ser positiva o cero.

2.7.3. Implementacin Software del Modelo

En el simulador no es posible crear un bloque que se adapte dinmicamente al nmero de

convertidores que deseamos simular. Por esta razn se modela, como ejemplo de la capacidad del

modelo, en SIMULINK el ltro de salida de 2 convertidores en paralelo. Se crean dos bloques,

empleando la misma tcnica de modelado que para el ltro de salida de un nico convertidor, a los

que se denominan genericamente Filtro de Salida de Dos Reductores (FS2R) y Filtro Variable de

Salida de Dos Reductores (FVS2R), que aceptan las entradas de la Tabla 2.9 y permiten obtener

en sus salidas las variables de estado u

S

(t), u

C

(t), I

L1

(t) e I

L2

(t).

Nombre Funcin o variable matemtica Valor

Ug1, Ug2 u

e

1

(t), u

e

2

(t)

valores de las seales de entrada al

ltro

L1, L2 L

1

, L

2

valores de las inductancias

RL1, RL2 R

L

1

, R

L

2

valores de las resistencias de

prdidas de las inductancias

IL0, IL1 i

L

1

(0), i

L

2

(0)

corrientes iniciales por las

inductancias

C C valor del condensador equivalente

RC R

C

valor de la resistencia equivalente

serie del condensador

UC0 u

C

(0) tensin inicial en el condensador

RS R

S

valor de la resistencia de salida del

ltro. Es una constante en FS2R y

una entrada en FVS2R

Tabla 2.9: Entradas de los bloques FS2R y FVS2R

88

2.7 Paralelizado de Convertidores Reductores

El primer bloque (FS2R) se crea empleando elementos que modelan los diferentes coecientes

de las matrices de las Ec. 2.43, 2.41 y 2.42 e integradores. Los integradores de la biblioteca de

SIMULINK presentan la posibilidad de limitar su salida entre dos valores mximo y mnimo. Esto

hace factible que las corrientes por las inductancias no sean nunca negativas, que es el efecto que

provocan los diodos. El modelo resultante, denominado Filtro de Salida del Dos Reductor (FS2R),

inheremente no lineal, se muestra en la Fig. 2.21.

Este es el modelo no lineal en el espacio de estados

del Filtro de Salida de Dos Convertidores Reductores en Paralelo

4

Uc

3

IL2

2

IL1

1

Us

Suma3

Suma2

Suma1

Suma

1

s

Integrador2

1

s

Integrador1

1

s

Integrador

[Uc]

Goto Uc

[IL2]

Goto IL2

[IL1]

Goto IL1

[Uc]

From Uc 3

[Uc]

From Uc 2

[Uc]

From Uc 1

[IL2]

From IL2 3

[IL2]

From IL2 2

[IL2]

From IL2 1

[IL1]

From IL1 3

[IL1]

From IL1 2

[IL1]

From IL1 1

C3

C3

C2

C2

C1

C1

B22

B22

B11

B11

A33

A33

A32

A32

A31

A31

A23

A23

A22

A22

A21

A21

A13

A13

A12

A12

A11

A11

2

Ug2

1

Ug1

Figura 2.21: Modelo de SIMULINK del Filtro de Salida de Dos Reductores (sin

encapsular)

Para este nuevo bloque aparecen tres entradas ms, que se muestran en la Tabla 2.10. Sirven

para establecer los lmites mximos de los integradores. Las dos primeras representan las corrientes

de saturacin de las inductancias. Modelan, de manera simple, el comportamiento no lineal que

presenta una inductancia real cuando la corriente que circula por la misma provoca una saturacin

del ujo magntico. La tercera representa el valor de la tensin mxima del condensador.

Si bien con este bloque es factible obtener tanto diagramas de Bode, de respuesta al primer

armnico y transitorios (arranque suave, cambios de carga), no lo son de forma simple, ya que la

89

Captulo 2. Mtodo de Modelado Aplicando ...

Nombre Funcin o variable matemtica Valor

IL1MAX, IL2MAX corriente mxima por la inductancia

UCMAX tensin mxima en el condensador

Tabla 2.10: Entradas adicionales para el bloque FS2R

variacin de cualesquiera de los parmetros requiere detener la simulacin, guardar el estado de las

variables, cambiar el valor de los parmetros y continuar la simulacin. Con objeto de remediar esta

situacin se crea un nuevo modelo del ltro de salida de dos reductores, siguiendo un desarrollo

anlogo al anterior, pero dejando esta vez la variable R

S

como una entrada al bloque de SIMULINK,

de tal forma que para cambiar la respuesta del mismo slo sea necesario establecer la variacin de

la funcin que modele la resistencia de salida.

Para conseguir esto se crea un bloque al que se denomina Filtro Variable de Salida de Dos

Reductores (FVS2R), que tambin es inherentemente no lineal y cuyo modelo se muestra en la

Fig. 2.22.

2.7.4. Ensayos de los Modelos FS2R y FVS2R

Para comprobar que tanto el desarrollo matemtico como la implantacin funcional en el

modelo de SIMULINK de los distintos F*S2R son correctas se llevan a cabo una serie de pruebas

cuyos resultados se muestran en el apartado 3.7 en la pgina 135.

90

2.7 Paralelizado de Convertidores Reductores

4

Uc

3

IL2

2

IL1

1

Us

V9

V8

V7

V6

V5

V4

V3

V2

V16

V15

V14

V13

V12

V11

V10

V1

Suma 4

Suma 3

Suma 2

Suma 1

S1

RL2

RL2

RL1

RL1

RC

RC

P9

P8

P7

P6

P5

P4

P3

P2

P13

P12

P11

P10

P1

L2

L2

L1

L1

1

s

Integrador 3

1

s

Integrador 2

1

s

Integrador

[Uc]

Goto Uc

[KV3]

Goto KV3

[KV2]

Goto KV2

[KV1]

Goto KV1

[IL2]

Goto IL2

[IL1]

Goto IL1

[B22]

Goto B22

[B11]

Goto B11

[A33]

Goto A33

[A3]

Goto A3

[A23]

Goto A23

[A22]

Goto A22

[A21]

Goto A21

[A13]

Goto A13

[A12]

Goto A12

[A11]

Goto A11

[Uc]

From Uc 3

[Uc]

From Uc 2

[Uc]

From Uc 1

[KV3]

From KV3 3

[KV3]

From KV3 2

[KV3]

From KV3 1

[KV2]

From KV2 4

[KV2]

From KV2 3

[KV2]

From KV2 2 [KV2]

From KV2 1

[KV1]

From KV1 1

[IL2]

From IL2 3

[IL2]

From IL2 2

[IL2]

From IL2 1

[IL1]

From IL1 3

[IL1]

From IL1 2

[IL1]

From IL1 1

[B22]

From B22 1

[B11]

From B11 1

[A33]

From A33 1

[A3]

From A3 2

[A3]

From A3 1

[A23]

From A23 1

[A22]

From A22 1

[A21]

From A21 2

[A21]

From A21 1

[A13]

From A13 1

[A12]

From A12 2

[A12]

From A12 1

[A11]

From A11 1

C

C

1

1.3

1

1.2

1

1.1

3

RS

2

Ug2

1

Ug1

RS

RC

RS+RC

Figura 2.22: Modelo de SIMULINK del Filtro Variable de Salida de Dos Reductores

(sin encapsular)

91

Captulo 2. Mtodo de Modelado Aplicando ...

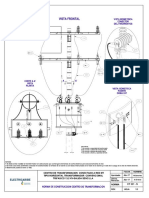

2.8. La Biblioteca de Simulink

Todos los desarrollos de los modelos y sus implantaciones software han dado lugar a una

biblioteca de mdulos, que se encuentra disponible en el CD adjunto de la tesis. Su empleo requiere

disponer de MATLAB versin 6 ( superior) y SIMULINK versin 4 ( superior) para poder simular

los modelos. Los bloques que contiene se muestran en la Fig. 2.23.

Ue

Delta

Phi

PS

Ug

Uc

GTCc

Ug

RS

Us

IL

Uc

FVSR

Ug1

Ug2

RS

Us

IL1

IL2

Uc

FVS2R

Ug

RS

Us

IL

Uc

FVNLSR

Ue

Ug

RS

Us

IL

Uc

FVNLSE

Ug

Us

IL

Uc

FSR

Ug1

Ug2

Us

IL1

IL2

Uc

FS2R

Ug

Us

IL

Uc

FNLSR

Um

Uref

Uctrl

Uc1

Uc2

CompNL2

Um

Uref

Uctrl

Uc1

Uc2

CompNL1

Um

Uref

Uctrl

Uc1

Uc2

Comp2

Um

Uref

Uctrl

Uc1

Uc2

Comp1

Figura 2.23: Biblioteca SIMULINK de bloques

92

También podría gustarte

- Seleccion Transformadores de Medida Medidor Conexionado Ra8 030 PDFDocumento49 páginasSeleccion Transformadores de Medida Medidor Conexionado Ra8 030 PDFJuan David Velasquez GomezAún no hay calificaciones

- Macros Visual Basic para ExcelDocumento43 páginasMacros Visual Basic para Excelsilroggero6746100% (1)

- Doble Tiro Media TensionDocumento17 páginasDoble Tiro Media TensionStiver MartinezAún no hay calificaciones

- Doble Tiro Media TensionDocumento2 páginasDoble Tiro Media TensionStiver MartinezAún no hay calificaciones

- Doble Tiro Media TensionDocumento17 páginasDoble Tiro Media TensionStiver MartinezAún no hay calificaciones

- Capitulo 11 Centros de Transformacion AereosDocumento12 páginasCapitulo 11 Centros de Transformacion AereosStiver MartinezAún no hay calificaciones

- Abb Subestaciones CompactasDocumento57 páginasAbb Subestaciones Compactasfernanditomt100% (1)

- Codificacion IpseDocumento1 páginaCodificacion IpseStiver MartinezAún no hay calificaciones

- NTC 3229Documento43 páginasNTC 3229Ricardo Valencia100% (1)

- Retencion GuitarraDocumento1 páginaRetencion GuitarraStiver MartinezAún no hay calificaciones

- Afloramiento para Alimentar Derivacion Area de Circuito de Nivel Ii NCS 842Documento1 páginaAfloramiento para Alimentar Derivacion Area de Circuito de Nivel Ii NCS 842Stiver MartinezAún no hay calificaciones

- Nociones Bascias de Sistemas de CCAADocumento27 páginasNociones Bascias de Sistemas de CCAAStiver MartinezAún no hay calificaciones

- PedestalDocumento19 páginasPedestalAndres AlonsoAún no hay calificaciones

- Ormaset-M: Instrucciones GeneralesDocumento16 páginasOrmaset-M: Instrucciones GeneralesStiver MartinezAún no hay calificaciones

- Constantes de Regulacion BT MTDocumento11 páginasConstantes de Regulacion BT MTCristian MontillaAún no hay calificaciones