Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Disciplina Estatica

Disciplina Estatica

Cargado por

xmen1993Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Disciplina Estatica

Disciplina Estatica

Cargado por

xmen1993Copyright:

Formatos disponibles

DISIPLINA ESTATICA EN TRANSISTORES MOSFET

DISIPLINA ESTATICA La disciplina esttica es una especificacin para dispositivos digitales. La disciplina esttica requiere dispositivos para interpretar correctamente los voltajes que se encuentran dentro de los umbrales de entrada (VIL y VIH). Mientras las entradas vlidas se proporcionan a los dispositivos, la disciplina tambin requiere que los dispositivos para producir voltajes de salida vlidos que satisfacen los umbrales de salida (VOL y VOH). En este tema se introduce el elemento del circuito del interruptor y demuestra cmo las puertas lgicas digitales se pueden construir usando MOSFET (Metal Oxide Semiconductor Transistor de efecto de campo). EL INTERRUPTOR El interruptor est normalmente apagado y se comporta como un circuito abierto. cuando la presin es aplicada al interruptor, se cierra y se comporta como un alambre y conduce la corriente. FIGURA 6.1

En consecuencia, el interruptor puede ser modelado como el dispositivo de tres terminales se muestra en la Figura 6.2. Las tres terminales incluyen un terminal de control, un terminal de entrada y un terminal de salida. Los terminales de entrada y de salida de un interruptor comnmente exhiben propiedades simtricas. Cuando el terminal de control tiene un VERDADERO o una seal de 1 lgico en l, la entrada est conectada a la salida a travs de un corto circuito, y el interruptor se dice que est en su estado ON. De lo contrario, existe un circuito abierto entre la entrada y la salida, y el interruptor se dice que est en su estado OFF.

FIGURA 6.2

como se ilustra en la figura 6.3, cuando la entrada de control es un 0 lgico, la curva VI para el par terminal de entrada-salida indica que la corriente a travs del interruptor es 0, independientemente de la tensin aplicada. Por el contrario, el interruptor se comporta como un corto circuito entre su entrada y terminales de salida cuando la entrada de control es un 1 lgico. Cuando se comporta como un cortocircuito, el voltaje a travs de los terminales de entrada y de salida es cero, y la corriente no est restringida por el interruptor (en lugar, se determina por las limitaciones que son externos al interruptor). Las caractersticas vi de un interruptor tambin se pueden expresar en forma algebraica como: para el Control ='' 0'' i = 0 y para el Control ='' 1'', v = 0.

FIGURA 6.3

FUNCIONES LOGICAS UTILIZANDO INTERRUPTORES A continuacin, consideremos el circuito de bombilla con un par de interruptores conectados en serie como se muestra en la figura 6.6a. La bombilla se puede activar slo mediante el cierre de los dos interruptores A y B. De forma similar, la figura 6.6b muestra un circuito con un par de interruptores conectados en paralelo. En esta ltima configuracin, la bombilla se puede activar mediante el cierre o bien el interruptor A o interruptor B. FIGURA 6.6

EL DISPOSITIVO MOSFET Y SU MODELO S El MOSFET pertenece a una clase de dispositivos llamados transistores. El MOSFET es un dispositivo de tres terminales con un terminal de control, un terminal de entrada y un terminal de salida.

Como se muestra en la Figura 6.8, el terminal de control del MOSFET se llama a su puerta G, el terminal de entrada de su drenaje D, y el terminal de salida de su fuente S. Para nuestros propsitos, podemos tratar la fuente y el drenaje de una manera simtrica.

FIGURA 6.8

Un modelo de circuito simple para un tipo especfico de dispositivo MOSFET llamado MOSFET de canal n. Este modelo basado en un simple interruptor se llama del interruptor MOSFET modelo, o S Modelo. El dispositivo est en el estado ON cuando vGS cruza una tensin de umbral VT, de lo contrario, est desactivado. En el estado OFF, existe un circuito abierto entre el drenaje y la fuente. Como se ilustra en la figura 6.10, existe un circuito abierto entre la puerta y la fuente, y entre la puerta y el drenaje en todo momento.

FIGURA 6.10

Podemos resumir el modelo S para el MOSFET en forma algebraica declarando sus caractersticas v i de la siguiente manera: para vGS <VT, IDS = 0 y para vGS VT, vDS = 0

podemos tratar el par de terminales G y S como el puerto de entrada o el puerto de control y el par de terminales D y S como el puerto de salida del MOSFET.

a) El inversor MOSFET b) El mismo circuito inversor utilizando la notacin abreviada de alimentacin y tierra.

Una forma mas simbolica de representar el inversor del MOSFET donde IN y OUT representan los valores logicos VIN y vOUT.

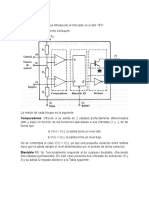

Figura 6.17 muestra el modelo equivalente para el circuito mostrado en la Figura 6.14. Supongamos que un alto lgico se representa mediante 5 V y una lgica baja 0 con V. Como se muestra en la Figura 6.17, cuando el VIN de entrada es alta, el MOSFET est en el estado ON (suponiendo que el nivel de alta tensin est por encima del umbral VT), tirando de ese modo la tensin de salida a un valor bajo. En contraste, cuando la entrada es baja, el MOSFET est apagado, y la salida se eleva a un valor alto por RL. Aqu vemos el propsito de la resistencia de carga RL que proporciona una salida de 1 lgico cuando el MOSFET est apagado. Adems, RL se elige generalmente para ser grande de modo que la corriente est limitada cuando el MOSFET est en ON. Debido a que la resistencia entre los puertos del drenaje-fuente del MOSFET de puerta a fuente y es infinito en el modelo S, el iIN actual es 0. FIGURA 6.17

La figura 6.18 muestra una forma de onda de entrada de la muestra y la forma de onda de salida correspondiente a nuestro circuito. FIGURA 6.18

FIGURA 6.19

Tambin podemos construir otras puertas de la misma manera. La figura 6.20 muestra un circuito de puerta NAND y la Figura 6.21 muestra el modelo de circuito equivalente S. Es fcil ver que la salida es un 0 slo cuando ambas entradas son altas. La salida es alta cuando es lo contrario.

FIGURA 6.20

FIGURA 6.21

Usando la intuicin del circuito NAND de dos entradas, podemos construir NAND y NOR de entradas mltiples. La figura 6.22a muestra un n-entradas para la compuerta NOR y 6.22b muestra n-entrada para la compuerta NAND. En la entrada de la puerta NOR mltiple, la salida se tira a tierra cuando cualquiera de las entradas es alta. De la misma manera, en la puerta NAND, la salida sigue siendo alta, incluso si una entrada es baja. La conexin en paralelo de dos transistores (o grupo de ellos) acta como una puerta OR. La conexin en serie de dos transistores (o grupo de ellos) acta como una puerta AND.

FIGURA 6.22

EJEMPLO: Dadas las funciones dibujar su equivalente:

Primera funcin:

Segunda funcin

Anlisis esttico utilizando el modelo S La curva de transferencia de entrada-salida para el inversor mostrado en la Figura 6.19, o la caracterstica del inversor, contiene toda la informacin necesaria para determinar si el inversor satisface una disciplina esttica dada. Recordemos que la disciplina esttica para una puerta lgica garantiza que las salidas de la puerta se reunirn las restricciones de salida especificados por la disciplina, proporcionado a sus entradas de satisfacer las restricciones de entrada. La figura 6.26 ilustra la asimetra entre las entradas y las salidas. En la entrada de la puerta, cualquier nivel de voltaje ms bajo que VIL es reconocido como una baja vlida, y cualquier voltaje ms alto que VIH es un alto vlido. A su salida, la puerta se garantiza para producir un nivel de tensin superior a VOH un alto vigente, con un nivel de tensin inferior a VOL para una baja vlido. Los niveles de tensin entre VIL y VIH no son vlidos en la entrada, y los niveles entre VOL y VOH no son vlidos en la salida. Debido a que los niveles de produccin son ms estrictos que los umbrales de entrada, la disciplina esttica prev mrgenes de ruido.

En base a las caractersticas del convertidor (se repite aqu en la figura 6.27 por conveniencia), podemos determinar si el inversor cumple una disciplina esttica determinada. Como ejemplo, vamos a determinar si el inversor cumple una disciplina esttica con los siguientes umbrales de tensin: VOH = 4,5 V, VOL = 0,5 V, VIH = 4 V y VIL = 0,9 V.

La caracterstica de transferencia del inversor.

Valores lgicos y niveles de tensin correspondientes a una disciplina esttica adecuada para el inversor. Figura 6.28 muestra los umbrales de tensin para la disciplina esttica dado superpuesta a la funcin de transferencia del inversor. Vamos a ver cada uno de los umbrales de entrada y salida.

VOH: El inversor produce una salida alta de 5 V. Evidentemente, este nivel de tensin de salida para un 1 lgico es mayor que la salida-alto umbral 4,5-V requerida por la disciplina esttica. VOL: El inversor produce una salida baja de 0 V. Esta tensin de salida es inferior a la produccin bajo el umbral de 0,5 V requerida por la disciplina esttica. VIH: Para nuestra disciplina esttica, VIH = 4 V. Para obedecer la disciplina esttica del inversor debe interpretar cualquier voltaje por encima de 4 V como un 1 lgico. Esto es especialmente cierto para nuestro inversor. Nuestro inversor se enciende cuando la tensin de entrada es mayor que VT = 1 V y tira de la salida a un voltaje bajo vlidas. Por lo tanto, interpreta cualquier voltaje por encima de 1 V como un 1 lgico.

VIL: Para nuestra disciplina esttica, VIL = 0,9 V. Esto significa que obedecen a la disciplina esttica el inversor debe interpretar cualquier tensin por debajo de 0,9 V como un 0 lgico. Esto es cierto para nuestra inversor. El inversor est apagado cuando la tensin de entrada es inferior VT = 1 V, y su salida es a las 5 V. Dado que el inversor produce una tensin de salida de alta vlido (salida) para tensiones de entrada por debajo de 0,9 V, cumple la disciplina esttica. Ejemplo disciplina esttica Vamos a ver para ver si nuestro inversor satisface una disciplina esttica utilizado por Disco Systems Inc. Supongamos que algunos de los sistemas de disco se adhieren a una disciplina esttica con los siguientes umbrales de tensin: VOH = 4 V, VOL = 1 V, VIH = 3,5 V y VIL = 1,5 V. Para operar bajo esta disciplina esttica, sabemos que nuestros inversores deben operar de la siguiente manera:

Cuando la salida de un 1 lgico, el voltaje de sus salidas producen debe ser al menos VOH = 4 V. Dado que nuestros inversores producen una salida de 5 V para un 1 lgico, que se cumpla esta condicin. Cuando se emite un 0 lgico, el voltaje de sus salidas producen debe ser no mayor que VOL = 1 V. Dado que nuestros inversores producen una salida de 0-V para un 0 lgico, que se cumpla esta condicin fcilmente. En sus entradas los inversores deben reconocer tensiones superiores a VIH = 3,5 V como un 1 lgico. Ya que nuestros inversores reconocen tensiones superiores a 1 V como un 1 lgico, que se cumpla esta condicin. Por ltimo, en sus entradas, los inversores deben reconocer tensiones de menos de VIL = 1,5 V como un 0 lgico si son para satisfacer disciplina esttica de Disco. Desafortunadamente, nuestros inversores pueden reconocer tensiones slo por debajo de 1 V como un 0, y por lo tanto no satisfacer esta condicin. Por lo tanto, nuestros inversores no se pueden utilizar en los sistemas de disco.

Cuando se utiliza el modelo de S para el MOSFET, los umbrales de entrada y salida de voltaje para el NAND y otros circuitos digitales vienen a ser idnticos a los del inversor. Por lo tanto, los resultados de anlisis esttico para estos circuitos son idnticos a aquellos para el inversor. Por ejemplo, como el inversor, el circuito NAND satisface una disciplina esttica con los siguientes umbrales de tensin: VOH = 4,5 V, VOL = 0,5 V, VIH = 4 V, y VIL = 0,9 V. Del mismo modo, el NAND no es capaz de satisfacer la disciplina esttica con estos umbrales de tensin: VOH = 4 V, VOL = 1 V, VIH = 3,5 V y VIL = 1,5 V. EL MODELO SR DEL MOSFET En particular, un MOSFET prctica muestra una resistencia no-cero entre sus terminales D y S cuando est encendido. En consecuencia, un modelo ligeramente ms preciso para el MOSFET utiliza una resistencia RON en lugar del corto entre D y S cuando el MOSFET est encendido. La figura 6.29 muestra el modelo de resistencia-conmutador (o modelo SR) del MOSFET de canal n. Cuando el MOSFET est apagado, no hay conexin entre el drenaje y la fuente. Si la tensin VGS entre los terminales de puerta y la fuente est por encima de VT, el MOSFET se

enciende y muestra una resistencia RON entre sus terminales D y S. Al igual que antes, existe un circuito abierto entre los terminales de puerta y de fuente de los terminales de puerta y drenador del MOSFET, por lo que iG = 0. El modelo SR es una mejor aproximacin del comportamiento MOSFET que el modelo S. De hecho, es fcil ver que el modelo SR reduce al modelo S si RON es cero. Sin embargo, el modelo SR an es una burda simplificacin de la conducta MOSFET. En particular, aunque el MOSFET muestra un comportamiento de resistencia cuando VDS << VGS - VT, la resistencia RON no es fijo. Ms bien, es una funcin de VGS. Por otra parte, cuando VDS es comparable, o mayor que, VGS - VT, el comportamiento de drenaje-fuente no es resistiva en absoluto, sino que ms bien es la de una fuente de corriente. Sin embargo, el modelo de resistencia fija es mucho ms simple y suficiente para el anlisis de algunos aspectos de los circuitos digitales debido a que el voltaje de puerta es bimodal baja o alta. Cuando el voltaje es bajo, el MOSFET se apaga, y cuando la tensin es alta, la conexin de drenajefuente RON ofrece una resistencia relacionada con la tensin de puerta. Dado que slo hay un valor para el voltaje de la puerta cuando la entrada es alta (por ejemplo VS), y, en consecuencia, un valor para la resistencia RON, podemos utilizar este valor para RON en nuestro modelo. En resumen, el modelo SR es vlida slo cuando VDS<<VGS - VT, y cuando slo hay un valor para el voltaje de la puerta cuando la entrada es alta (por ejemplo vGS = VS).

FIGURA 6.31: Caractersticas del MOSFET de acuerdo con el modelo SR. La regin en la que el MOSFET muestra un comportamiento resistivo es dentro de la regin trodo de operacin MOSFET.

El modelo SR para el MOSFET tambin se puede expresar en forma algebraica como:

iDS = 0

Para VGS VT Para VGS<VT

Anlisis esttico utilizando el modelo SR La presencia de la resistencia en RON complica el diseo de puertas lgicas ligeramente, pero aade ms realismo al modelo. Analicemos el circuito inversor familiarizado como se muestra en la figura 6.14 utilizando el modelo SR del MOSFET. En particular, vamos a derivar la caracterstica de transferencia de entrada y salida. La figura 6.39 muestra el modelo de circuito del inversor mediante el modelo SR del MOSFET.

FIGURA 6.39

Cuando la entrada es baja, el MOSFET est apagado, y la salida se eleva a un valor alto. Sin embargo, cuando el VIN de entrada es alta (y por encima del umbral VT), el MOSFET est en RON y muestra una resistencia entre sus terminales S y D, tirando de ese modo la tensin de salida inferior. Sin embargo, la tensin de salida no es 0 V como se predijo por el modelo ms simple S del MOSFET. En su lugar, el valor de la tensin de salida est dada por la relacin del divisor de voltaje: 6.5

Las caractersticas resultantes del invertidor de transferencia, asumiendo VS = 5V, VT =1V, RON = 1k Y RL = 14 k , Se muestran en la Figura 6.40. Tenga en cuenta que el voltaje de salida ms bajo del inversor ya no es 0 V, sino que es

Caractersticas de transferencia del inversor mediante el modelo SR.

FIGURA 6.40

En particular, vamos a analizar la relacin entre VT, VS, RL, y Ron y el comportamiento de conmutacin del inversor. Como mnimo, cuando un inversor enva unidades a un inversor de recepcin, el emisor debe ser capaz de conmutar el MOSFET en el inversor que recibe en su estado ON cuando el emisor produce una tensin alta. Del mismo modo, el emisor debe ser capaz de conmutar el MOSFET en el inversor que recibe en su estado OFF cuando el emisor produce un voltaje bajo. Nuestro inversor produce un alto rendimiento de VS, por lo que es fcil ver que el alto rendimiento puede girar el MOSFET en un inversor que recibe en su estado ON (siempre, claro est, que VS> VT). Debido a que el inversor produce un bajo gasto distinto de cero, ms cuidado hay que tener en la eleccin de los valores de resistencia y los parmetros del MOSFET. Especficamente, para nuestro diseo del inversor, la salida de voltaje para un 0 lgico debe ser lo suficientemente baja para que el MOSFET en el receptor permanece en OFF. Debido a que el MOSFET se activa para una tensin de entrada mayor que VT, la siguiente condicin debe cumplirse para la baja salida de un inversor para poder conducir el MOSFET en otro inversor en estado OFF: 6.6

Ecuacin 6.6 especifica una relacin clave entre los parmetros del dispositivo inversor para que pueda utilizarse como un dispositivo de conmutacin. Tenga en cuenta que no se distingue entre el MOSFET o parmetros de valor de la resistencia para el emisor y el receptor, puesto que el dispositivo debe ser capaz de servir como un emisor y un receptor. En los sistemas reales, sin embargo, debe tambin prever mrgenes de ruido adecuados mediante el cumplimiento de una disciplina esttica. La caracterstica del inversor se muestra en la Figura 6.40 nos proporciona informacin suficiente para determinar si el inversor cumple una disciplina esttica determinada. Como ejemplo, vamos a determinar si el inversor cumple una disciplina esttica con los siguientes umbrales de tensin:

VOH = 4,5 V, VOL = 0,5 V, VIH = 4 V y VIL = 0,9 V. La figura 6.41 muestra los umbrales de tensin para la disciplina esttica dada superpuesta a la funcin de transferencia del inversor. Vamos a ver cada uno de los resultados y los umbrales de entrada. VOH: El inversor produce una salida alta de 5 V. Evidentemente, esta salida nivel de tensin para un 1 lgico es mayor que el 4,5 V-salida de alta umbral requerido por la disciplina esttica. VOL: El inversor produce una salida baja de 0,33 V. Esta tensin de salida es inferior a la produccin bajo el umbral de 0,5 V requeridos por la disciplina esttica. VIH: Para nuestra disciplina esttica, VIH = 4 V. Para obedecer la disciplina esttica inversor debe interpretar cualquier voltaje por encima de 4 V como un 1 lgico. Es cierto para nuestro inversor. VIL: Para nuestra disciplina esttica, VIL = 0,9 V. Esto significa que para obedecer la disciplina esttica del inversor debe interpretar cualquier voltaje por debajo de 0,9 V como un 0 lgico. Esto tambin es cierto para nuestro inversor. FIGURA 6.41

As, nuestro inversor cumple la disciplina esttica con los umbrales de tensin: VOH = 4,5 V, VOL = 0,5 V, VIH = 4 V, y VIL = 0,9 V, incluso cuando el modelo SR se utiliza cuando RL = 14 k y RON = 1 k. Supongamos que se nos da una disciplina esttica con los siguientes Voltajes umbrales: VOH = 4,5V, VOL = 0,2V, VIH =4V y VIL =0,9V. Vamos a determinar si nuestro inversor satisface las limitaciones de esta disciplina esttica, y si no es as, vamos a redisear el inversor para que lo haga. Comencemos comparando las caractersticas de transferencia de nuestro inversor frente al voltaje umbral de la disciplina esttica dada. Como se muestra en la Figura 6.40,

recordar que nuestro inversor produce una alta salida de 5 V, y una salida baja de 0,33 V. Se puede interpretar voltajes debajo de VT = 1 V como un 0 lgico y tensiones por encima de VT = 1 V como un 1 lgico. 1. Cuando la salida es un 1 lgico, el voltaje producido por nuestro inversor debe ser mayor de VOH = 4,5 V. Dado que nuestros inversores producen una salida de 5 V para un 1 lgico, se satisface esta condicin. 2. Cuando la salida es un 0 lgico, la tensin debe ser mayor que VOL = 0,2 V. Dado que nuestros inversores producen una salida de 0,33 V para un 0 lgico, entonces esta condicin es violada. 3. En sus entradas, se debe reconocer los voltajes superiores a VIH = 4 V como una entrada lgica 1. Dado que nuestros inversores reconocen voltajes superiores a 1 V como un 1 lgico, tambin se cumple esta condicin 4. Por ltimo, en las entradas, los inversores deben reconocer voltajes menores que VIL = 0,9 V como una lgica 0 si (es) son (estn) para satisfacer la disciplina esttica. Dado que el bajo voltaje de salida producido por nuestros inversores es 0,33 V, es ms alto que el requerido VOL = 0,2 V, nuestros inversores no cumplen con las restricciones de la disciplina esttica dada. Cmo podramos redisear nuestro inversor para cumplir con la disciplina esttica dada? Observe que de acuerdo con la Ecuacin 6.5 el voltaje de salida del inversor para una entrada de alta est dada por:

La salida VOUT es 0,33 V para VS = 5V, RON = 1k y RL = 14 k. Necesitamos nuestro inversor para producir una potencia inferior a 0,2 V para una entrada de alta. En otras palabras:

Tenemos tres opciones para reducir el voltaje de salida: reduciendo el VS, reduciendo el RON, o aumentando RL. La reduccin de VS tambin reducir la alta tensin de salida (Alto Voltaje), por lo que tal no es una buena estrategia. En su lugar, trabajaremos con las resistencias. En primer lugar, vamos a tratar de aumentar el RL. Reordenando la ecuacin 6.7, obtenemos:

Para VS = 5 V and RON = 1 k, tenemos

En otras palabras, podemos elegir RL> 24 k, Lo que resultar en un voltaje de salida para un 0 lgico que es inferior a 0.2 V. Sin embargo, resulta que los grandes valores de la resistencia son difciles de lograr en la tecnologa VLSI. La Seccin 6.11 muestra cmo otro MOSFET puede ser utilizado en lugar de la resistencia pull-up. Alternativamente, se puede tratar de reducir el RON aumentando el rango W/L del MOSFET. Determinaremos el rango W/L mnimo. De la ecuacin 6.7, podemos encontrar la restriccin en RON, esto permite que el bajo voltaje de salida sea inferior a 0,2 V:

Para VS = 5 V y RL = 14 k, tenemos Desde (ver ecuacin 6.4), y asumiendo que Rn = 5 k para nuestro transistor MOSFET, tendremos

En otras palabras si elegimos un MOSFET con W/L > 8.62 resultara en un voltaje de salida para una lgica 0 que es menor que 0.2V ANALISIS ESTATIDO DE LA COMPUERTA NAND USANDO EL MODELO SR Tambin podemos analizar otras compuertas de la misma manera. Figura 6.42 muestra el circuito equivalente para la compuerta NAND mostrada en la Figura 6.20 basndose en el modelo SR MOSFET. En este caso, el voltaje de salida, cuando ambas entradas son altas viene dado por:

Determinaremos si nuestra compuerta NAND con VS = 5 V, RL = 14 k, y las propiedades MOSFET RON = 1 k y VT = 1 V, satisface la disciplina esttica con los siguientes voltajes umbrales:

Recuerde nuestro inversor con caractersticas mostrado en la Figura 6.40 que satisface esta disciplina esttica. Ahora revisemos nuestra compuerta NAND. La Figura 6.43 muestra los voltajes umbrales para la disciplina esttica dada superpuesta a la funcin de transferencia del inversor. Al igual que antes, vamos a ver cada uno de los de entrada y salida. Al igual que el inversor, la compuerta NAND produce una salida alta de 5 V y por lo tanto, satisface la salida de Voltaje umbral Alto de 4,5 V. Asimismo, el Compuerta NAND satisface tanto a el VIH = 4 y a el VIL = 0.9 V ya que interpreta tensiones por encima de 4 V en su entrada como un 1 lgico y la alimentacin por debajo de 0,9 V en sus entradas como un 0 lgico. Veamos ahora en VOL. Cuando la salida de un 0 lgico, la compuerta NAND produce un voltaje

Los niveles corresponden a esttica Superpuesta a las transferibles en NAND

de la

voltajes disciplina

caractersticas la compuerta

Para VS = 5 V, RL = 14 k, Y RON = 1k, Obtenemos VOUT = 0.625 V, que es casi el doble de la producida por el inversor para una salida lgica 0. Esto no es sorprendente, ya que hay dos MOSFETs en serie en la red desplegable. Dado que esta tensin de salida es mayor que VOL = 0,5 V, concluimos de que nuestra NAND no cumple con la disciplina esttica. Cmo podemos redisear nuestra puerta NAND de tal manera que satisfaga la disciplina esttica? Un mtodo es aumentar RL de tal manera que

En otras palabras

Para VS = 5 V y RON = 1 k, tenemos RL > 18 k.

Esto quiere decir que podemos elegir RL > 18 k para la compuerta NAND, que resultara en un voltaje de salida para un lgico 0 que es menor que 0.5 V, satisfaciendo as la disciplina esttica.

También podría gustarte

- Armónicas en Sistemas Eléctricos IndustrialesDe EverandArmónicas en Sistemas Eléctricos IndustrialesCalificación: 4.5 de 5 estrellas4.5/5 (12)

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiDe EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiCalificación: 5 de 5 estrellas5/5 (1)

- Fuentes Con LM2596-LM2577Documento11 páginasFuentes Con LM2596-LM2577Facundo LopezAún no hay calificaciones

- Prueba de Resistencia de Aislamiento Del NúcleoDocumento12 páginasPrueba de Resistencia de Aislamiento Del NúcleonoctyopAún no hay calificaciones

- Resumen Grupo6Documento42 páginasResumen Grupo6Santiago BuitragoAún no hay calificaciones

- Laboratorio 1-PrevioDocumento15 páginasLaboratorio 1-Previoleslie1906Aún no hay calificaciones

- Informe Previo 3 Lab Circuitos DigitalesDocumento7 páginasInforme Previo 3 Lab Circuitos DigitalesBilly Markos Felix Gutierrez100% (1)

- Telecomunicaciones 2Documento18 páginasTelecomunicaciones 2Darwin Jesús Arela QuispeAún no hay calificaciones

- Multivibrador Astable Con Un 555Documento7 páginasMultivibrador Astable Con Un 555Meza Puchoc JeanAún no hay calificaciones

- Amplificador Operacional - Comparadores - S13.s1 PDFDocumento67 páginasAmplificador Operacional - Comparadores - S13.s1 PDFNilo Cardenas SudarioAún no hay calificaciones

- Comparador de UmbralDocumento7 páginasComparador de UmbralOmpar OmpadiriAún no hay calificaciones

- Historia Del 555Documento3 páginasHistoria Del 555Marko Boissieu0% (1)

- Tarea PWM ReporteDocumento7 páginasTarea PWM ReporteRichard QuinteroAún no hay calificaciones

- Circuitos Osciladores Con PWM 2017Documento12 páginasCircuitos Osciladores Con PWM 2017Matias GarayAún no hay calificaciones

- Electronica Comparadores 02Documento7 páginasElectronica Comparadores 02Robert BirdAún no hay calificaciones

- Fan-Out y Margenes de Ruido Del Ejercicio A Mano - Respuesta AlumnoDocumento3 páginasFan-Out y Margenes de Ruido Del Ejercicio A Mano - Respuesta Alumnosara gonzález rodríguezAún no hay calificaciones

- Amplificadores Operacionales Ideales. Cap8Documento50 páginasAmplificadores Operacionales Ideales. Cap8Francisco AndrésAún no hay calificaciones

- A.O. 2Documento93 páginasA.O. 2JORGECOLLANAún no hay calificaciones

- Informe Laboratorio Amplificadores OperacionalesDocumento40 páginasInforme Laboratorio Amplificadores OperacionalesGustavoMartinezAún no hay calificaciones

- Circuito BootstrapDocumento4 páginasCircuito BootstrapFabricio Veintimilla BautistaAún no hay calificaciones

- INFORME PREVIO N2 UtrillaDocumento12 páginasINFORME PREVIO N2 UtrillaKaren Peña ReyesAún no hay calificaciones

- RecortadoresDocumento5 páginasRecortadoresJorgeNitalesAún no hay calificaciones

- Familias TTL y CmosDocumento14 páginasFamilias TTL y CmosDiana OlivaresAún no hay calificaciones

- Consulta Detector Picos Conversor Ac DC Circuito Zona MuertaDocumento15 páginasConsulta Detector Picos Conversor Ac DC Circuito Zona MuertaDWilliam93Aún no hay calificaciones

- Circuito Integrado 555Documento24 páginasCircuito Integrado 555ToÑo Zednem NamzugAún no hay calificaciones

- Parador Con Amplificador Operacional 2012Documento8 páginasParador Con Amplificador Operacional 2012Clau SanPerAún no hay calificaciones

- El A.O ComparadorDocumento17 páginasEl A.O ComparadorTDFRIOGRANDEAún no hay calificaciones

- Familia DTLDocumento3 páginasFamilia DTLHenry LazoAún no hay calificaciones

- Comparadores 1Documento11 páginasComparadores 1napoleon_velasc3617Aún no hay calificaciones

- Practica 5 - Inversores y Puertas LogicasDocumento4 páginasPractica 5 - Inversores y Puertas LogicasJose YucraAún no hay calificaciones

- Practica de Electronica IndustrialDocumento28 páginasPractica de Electronica IndustrialJose Gabriel Torrealba OropezaAún no hay calificaciones

- Flores - Espinoza - Efren - Jair - Tema 4Documento27 páginasFlores - Espinoza - Efren - Jair - Tema 4JairAún no hay calificaciones

- Tipos de Amplificadores OperacionalesDocumento13 páginasTipos de Amplificadores Operacionalesdani ramirezAún no hay calificaciones

- CMOS - Compuertas LogicasDocumento6 páginasCMOS - Compuertas LogicasCarlos Andres Montaña100% (1)

- Polarizacion Del Transistor BJTDocumento29 páginasPolarizacion Del Transistor BJTLarry Christian Tumialán BorjaAún no hay calificaciones

- Circuitos de Lazo de Corriente Juan Moreno V27681003 Lab. Auto Industrial O1013Documento6 páginasCircuitos de Lazo de Corriente Juan Moreno V27681003 Lab. Auto Industrial O1013JuanAún no hay calificaciones

- Funcion de TransferenciaDocumento18 páginasFuncion de Transferenciavimpher33% (3)

- Recortadores, Sujetadores y Multiplicadores de VoltageDocumento12 páginasRecortadores, Sujetadores y Multiplicadores de VoltageCamara FoscamAún no hay calificaciones

- Practica 1 Electrónica DigitalDocumento7 páginasPractica 1 Electrónica DigitalMartaLópezAún no hay calificaciones

- Reguladores de Voltaje en C.I. 19766 23871Documento29 páginasReguladores de Voltaje en C.I. 19766 23871Henry H. Huaman GarcíaAún no hay calificaciones

- PachecoDocumento46 páginasPachecojonathanAún no hay calificaciones

- Zona MuertaDocumento5 páginasZona MuertaManuel BenegasAún no hay calificaciones

- Seguidor y ComparadorDocumento12 páginasSeguidor y ComparadorJose Enrique Miranda Garcia100% (1)

- Amplificador Colector ComúnDocumento16 páginasAmplificador Colector ComúnJeseniaQuispeAún no hay calificaciones

- Familias TTL y CmosDocumento10 páginasFamilias TTL y CmosSantiago NúñezAún no hay calificaciones

- Compuertas LógicasDocumento4 páginasCompuertas LógicassololevelingticonaAún no hay calificaciones

- Configuraciones de Los OpamsDocumento12 páginasConfiguraciones de Los Opamsagab ojAún no hay calificaciones

- TimersDocumento11 páginasTimersErick ASAún no hay calificaciones

- Taller Electrónica-Primer PrevioDocumento3 páginasTaller Electrónica-Primer PrevionazlybetzabethmilenaccAún no hay calificaciones

- Aplicaciones No Lineales de Los OVAsDocumento12 páginasAplicaciones No Lineales de Los OVAsYasmani de la TorreAún no hay calificaciones

- Amplificador Con BJT en Emisor ComúnDocumento6 páginasAmplificador Con BJT en Emisor ComúnDaniel OliveraAún no hay calificaciones

- Info Previo 01digi IIDocumento12 páginasInfo Previo 01digi IIFelipe CarreñoAún no hay calificaciones

- PRAC4-APLICACIONES - 2a - PARTE (PDF - Io)Documento13 páginasPRAC4-APLICACIONES - 2a - PARTE (PDF - Io)Robert Rosas AgAún no hay calificaciones

- Circuitos Recortadores de Ond1Documento15 páginasCircuitos Recortadores de Ond1Yordan ChavezAún no hay calificaciones

- OpamDocumento6 páginasOpamYilmar Guillen ChaconAún no hay calificaciones

- Guia Practica 1Documento9 páginasGuia Practica 1Eduardo Jesús Sucno HerenciaAún no hay calificaciones

- 04 Polarizacion de Circuitos TransistorizadosDocumento60 páginas04 Polarizacion de Circuitos TransistorizadosEnrique CalvettyAún no hay calificaciones

- Polarizacion Del Transistor BJTDocumento29 páginasPolarizacion Del Transistor BJTElias Wilder Solano HuaroccAún no hay calificaciones

- Ect TTDocumento4 páginasEct TTQR RichardAún no hay calificaciones

- Semiconductores 2Documento11 páginasSemiconductores 2Miguel RamírezAún no hay calificaciones

- Avance Parte1 Proyecto FinalDocumento34 páginasAvance Parte1 Proyecto FinalMiguel BorjaAún no hay calificaciones

- PC2 Ee532 - Fiee UniDocumento2 páginasPC2 Ee532 - Fiee UniDavidAún no hay calificaciones

- Silabo Análisis de Circuitos Eléctricos I 2016-IDocumento9 páginasSilabo Análisis de Circuitos Eléctricos I 2016-IRUBEN GALEAS ARANAAún no hay calificaciones

- SQL02912Documento2 páginasSQL02912romina fernanda peralta jaraAún no hay calificaciones

- Aparatos de MandoDocumento7 páginasAparatos de Mandoaicvigo1973100% (2)

- Tema I Generalidades Del Sistema de MedidaDocumento20 páginasTema I Generalidades Del Sistema de MedidaGerardo Antonio TrejoAún no hay calificaciones

- Trabajo de Corriente Continua y AlternaDocumento8 páginasTrabajo de Corriente Continua y AlternaBrichyazuri BbllAún no hay calificaciones

- Ejercicios ElectrodinamicaDocumento4 páginasEjercicios ElectrodinamicaIsis SC0% (1)

- Cuadros de Carga RevDocumento4 páginasCuadros de Carga RevOscar LandazabalAún no hay calificaciones

- Interpretación de Planos MecánicosDocumento84 páginasInterpretación de Planos MecánicosAlex GarciaAún no hay calificaciones

- Clase Automatización 6 y 7 SeptiembreDocumento4 páginasClase Automatización 6 y 7 SeptiembreAbelardo RubioAún no hay calificaciones

- Informe Digitales 2Documento14 páginasInforme Digitales 2Rodrigo ZuñigaAún no hay calificaciones

- Cronograma ResidenciaDocumento21 páginasCronograma Residenciagenaro cruzAún no hay calificaciones

- Ejemplo de Cálculo de Sección Por El Criterio de La Intensidad de CortocircuitoDocumento12 páginasEjemplo de Cálculo de Sección Por El Criterio de La Intensidad de CortocircuitoCarlos CastilloAún no hay calificaciones

- Plano de Gas - MergedDocumento4 páginasPlano de Gas - MergedabrilAún no hay calificaciones

- Carro A Control RemotoDocumento22 páginasCarro A Control Remotoesteban viellardAún no hay calificaciones

- Investigación Del Tema 1.1Documento4 páginasInvestigación Del Tema 1.1Vrayan AlejandroAún no hay calificaciones

- 280101055Documento4 páginas280101055Aldair0% (2)

- LoooooDocumento10 páginasLoooooclinton ramirez abarcaAún no hay calificaciones

- Bichi Parte 3 y 4Documento19 páginasBichi Parte 3 y 4Pahola Fuentes ZamudioAún no hay calificaciones

- Trabajo Monografico #1Documento5 páginasTrabajo Monografico #1Wilmer Ahuanari RuizAún no hay calificaciones

- Practica 4 de Laboratorio de Fisca 3Documento11 páginasPractica 4 de Laboratorio de Fisca 3Jonathan Téllez AlmazánAún no hay calificaciones

- Transformador Catalogo de Conceptos Laura GallardoDocumento2 páginasTransformador Catalogo de Conceptos Laura GallardoZoe Jair BautistaAún no hay calificaciones

- Informe Previo-Vibrometro PdsDocumento6 páginasInforme Previo-Vibrometro PdsRenzoJesusAún no hay calificaciones

- Cálculo de Pérdidas Energéticas Por Efecto JouleDocumento3 páginasCálculo de Pérdidas Energéticas Por Efecto JouleCamilo Daniel Soto Ruíz DiazAún no hay calificaciones

- Cuaderno de Obra Diciembre MDocumento3 páginasCuaderno de Obra Diciembre MMairv ConstructoraAún no hay calificaciones

- 2022 - Sesión 1 - Curso Simaris SelectivdadDocumento49 páginas2022 - Sesión 1 - Curso Simaris SelectivdadJose Luis Quispe LuqueAún no hay calificaciones