Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Circuito Sumador Restador Con 7483

Cargado por

axefecDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Circuito Sumador Restador Con 7483

Cargado por

axefecCopyright:

Formatos disponibles

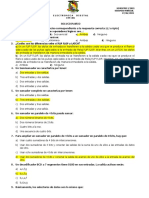

Circuito Sumador Restador con 7483

Veamos la figura de abajo. Si el interruptor S=0, entonces la salida del 7483 es igual a A+B I. Si S=1, entonces la salida del 7483 es A-BI. Donde A y BI son los nmeros binarios de 4 bits introducidos por el usuario y se sealan en la siguiente figura:

Ahora veamos qu ocurre en detalle:

Las entradas de cada compuerta XOR son: S y un bit de BI. Vemos que la salida de cada compuerta XOR est conectada a cada entrada del puerto B del 7483, respetando el subndice de las entradas BI. Es decir: si a una compuerta XOR entra el bit menos significativo del nmero binario BI, de esa compuerta sale el bit menos significativo del nmero binario B; y as ocurre con el resto de los bits. As mismo, C0=S. Hagamos una tabla de la verdad para S, un bit de BI, un bit de B y C0:

S 0

un bit de BI un bit de B 0 0

C0 0

0 1 1

1 0 1

1 1 0

0 1 1

Sea C la salida del 7483 y A la otra entrada que no se ha mencionado.

Vemos que si S=0, entonces cada bit de BI es igual a cada bit de B (respetando las cifras significativas), y C0=S=0. Por lo tanto, B=BI y: C = C0+A+B = 0+A+BI = A+BI : SUMA de los nmeros binarios introducidos.

Ahora bien, vemos que si S=1, entonces cada bit de BI es igual al negado de cada bit de B (respetando las cifras significativas), y C0=S=1. Por lo tanto, B=(BI)' y: C = C0+A+B = 1+A+(BI)' = A+[1 +(BI)' ]: RESTA de los nmeros binarios introducidos.

También podría gustarte

- 5-9 Circuitos Aritméticos.: La Unidad Aritmética/lógicaDocumento31 páginas5-9 Circuitos Aritméticos.: La Unidad Aritmética/lógicaluisAún no hay calificaciones

- Man Sistemas Digitales 2023-1Documento55 páginasMan Sistemas Digitales 2023-1HIDOKI KanshomAún no hay calificaciones

- Preinforme de La Practica 3 Diseño de Sumador-Restador de 8 BitsDocumento8 páginasPreinforme de La Practica 3 Diseño de Sumador-Restador de 8 BitsGabrielCordobaAún no hay calificaciones

- Ilovepdf Merged PDFDocumento6 páginasIlovepdf Merged PDFEduardo Saavedra LizarazúAún no hay calificaciones

- Memoria RAM 6116Documento10 páginasMemoria RAM 6116Joel AlconAún no hay calificaciones

- Most BusDocumento102 páginasMost Busjoaq.diazvAún no hay calificaciones

- Laboratorio 6 de Electronica Digital IDocumento3 páginasLaboratorio 6 de Electronica Digital IVic VigaAún no hay calificaciones

- Pablo Recabarren - Introduccion A La Electronica DigitalDocumento83 páginasPablo Recabarren - Introduccion A La Electronica DigitalFELIPE DANIEL MONTERO BRUNIAún no hay calificaciones

- Circuitos DigitalesDocumento11 páginasCircuitos DigitalesShirley Beleño BarriosAún no hay calificaciones

- Etn-506 Circuito RLC Axl Aparicio PDFDocumento7 páginasEtn-506 Circuito RLC Axl Aparicio PDFaxlhellfish666Aún no hay calificaciones

- Practica 2 DAC0808Documento15 páginasPractica 2 DAC0808javier_valdivia_42Aún no hay calificaciones

- Interpretar DatasheetDocumento6 páginasInterpretar DatasheetDidier Dorado IpiaAún no hay calificaciones

- Cómo Funciona Un Chip 7490Documento1 páginaCómo Funciona Un Chip 7490Leo AriasAún no hay calificaciones

- Practica1 Instrumentacion IDocumento2 páginasPractica1 Instrumentacion Ianderson “proxy”Aún no hay calificaciones

- AMC2 CP2 (Listo)Documento9 páginasAMC2 CP2 (Listo)CarlosAlejandroArroligaAmadorAún no hay calificaciones

- De Martin Negrin Guillermo TRABAJO 10Documento15 páginasDe Martin Negrin Guillermo TRABAJO 10GuillermoAún no hay calificaciones

- Informe MosfetDocumento4 páginasInforme MosfetmanucasttAún no hay calificaciones

- Carga Descarga CondensadorDocumento9 páginasCarga Descarga CondensadorPaul NarvaezAún no hay calificaciones

- Man Sistemas Digitales 2022-1 UnlockedDocumento52 páginasMan Sistemas Digitales 2022-1 UnlockedPaola YGAún no hay calificaciones

- td3 PDFDocumento226 páginastd3 PDFTecnicasdigitales3 UtnAún no hay calificaciones

- Circuitos MSI: Sumadores y Restadores DigitalesDocumento8 páginasCircuitos MSI: Sumadores y Restadores DigitalesJhonatan MartínezAún no hay calificaciones

- Informe 3 Unidad 2 Vicente AlvarezDocumento21 páginasInforme 3 Unidad 2 Vicente AlvarezVicente AlvarezAún no hay calificaciones

- Multiplex OresDocumento17 páginasMultiplex Oresyouacrazy100% (1)

- Definicion de Circuitos MixtosDocumento10 páginasDefinicion de Circuitos MixtosFrancisco Andrès Sepúlveda Vàsquez100% (1)

- Unidad 3 Portafolio Electronica DigitalDocumento37 páginasUnidad 3 Portafolio Electronica DigitalAlfredo De Santiago MedinaAún no hay calificaciones

- Decodificador DAC0800Documento4 páginasDecodificador DAC0800COBRACAN2208Aún no hay calificaciones

- Luces AudioritmicasDocumento5 páginasLuces Audioritmicasilm86Aún no hay calificaciones

- PROYECTO Termometro DigitalDocumento5 páginasPROYECTO Termometro DigitalJoel Rubiano ArevaloAún no hay calificaciones

- Clase 5 Set Reset Flancos Not PDFDocumento7 páginasClase 5 Set Reset Flancos Not PDFAntonio AntaloAún no hay calificaciones

- Ejercicio 1 Neumática Control de La Puerta de Un AutobúsDocumento1 páginaEjercicio 1 Neumática Control de La Puerta de Un AutobúsReinaldo Araúz AramayoAún no hay calificaciones

- Colores RGBDocumento21 páginasColores RGBBoris SalazarAún no hay calificaciones

- Documento Reloj y AlarmaDocumento8 páginasDocumento Reloj y AlarmaDavid AkramAún no hay calificaciones

- Transistor de Efecto de CampoDocumento51 páginasTransistor de Efecto de CampoMaria Alejandra Cardozo GuzmanAún no hay calificaciones

- Innforme Practica VHDL ALUDocumento13 páginasInnforme Practica VHDL ALUNatalia_meneses8Aún no hay calificaciones

- Conversores Adc DacDocumento6 páginasConversores Adc DacKevin Barahona VelascoAún no hay calificaciones

- CI1MA-GE-AP04 - APLICACIÓN DE LA CONGRUENCIA DE TRIÁNGULOS - Prof. Aldo Baldera SosaDocumento4 páginasCI1MA-GE-AP04 - APLICACIÓN DE LA CONGRUENCIA DE TRIÁNGULOS - Prof. Aldo Baldera SosaFenix 800Aún no hay calificaciones

- Diseño SFV Off-Grid Universidad de NariñoDocumento5 páginasDiseño SFV Off-Grid Universidad de NariñoAlejo BastidasAún no hay calificaciones

- Sistema de Bus Multiplexado para Cuatro RegistrosDocumento10 páginasSistema de Bus Multiplexado para Cuatro RegistrosRoberto BahenaAún no hay calificaciones

- Laboratorio VirtualDocumento3 páginasLaboratorio VirtualRicardo MCAún no hay calificaciones

- Proyecto Mecanica AnaliticaDocumento21 páginasProyecto Mecanica AnaliticaGersson AChAún no hay calificaciones

- CLASE - Amplificador Operacional SumadorDocumento8 páginasCLASE - Amplificador Operacional SumadorGregory Villamarin100% (1)

- Instrucciones Aritmeticas At89s52Documento8 páginasInstrucciones Aritmeticas At89s52ElBuenDany0% (1)

- Parcial Circuito Digital EsDocumento1 páginaParcial Circuito Digital EsFernando OrtizAún no hay calificaciones

- Marcador de Baloncesto Con PicDocumento16 páginasMarcador de Baloncesto Con Piccorpses88Aún no hay calificaciones

- Clase 3Documento7 páginasClase 3Iván CrespoAún no hay calificaciones

- Evolucion de La Conmutacion TelefonicaDocumento26 páginasEvolucion de La Conmutacion TelefonicarefnanAún no hay calificaciones

- Informe Flip FlopsDocumento11 páginasInforme Flip FlopsLeonardo López Avila100% (1)

- Voltimetro DigitalDocumento15 páginasVoltimetro DigitalAfir MinayaAún no hay calificaciones

- Esquemas Genericos de Cierre Centralizado PDFDocumento82 páginasEsquemas Genericos de Cierre Centralizado PDFalejandro sosaAún no hay calificaciones

- Tema 6 Teclado Digital DecimalDocumento4 páginasTema 6 Teclado Digital Decimal2mercedesAún no hay calificaciones

- Solucionario Segundo Parcial I-2021Documento4 páginasSolucionario Segundo Parcial I-2021Alverto FernandezAún no hay calificaciones

- C1 Contador de RizoDocumento4 páginasC1 Contador de RizoGarcía Román Itzel JocelynAún no hay calificaciones

- Diseño y Fabricacion de Antena Log PeriodicaDocumento9 páginasDiseño y Fabricacion de Antena Log PeriodicaJose Rafael CentenoAún no hay calificaciones

- SUMADORESDocumento18 páginasSUMADORESDiana BardónAún no hay calificaciones

- SUMADORESDocumento18 páginasSUMADORESMaribel CoronacionAún no hay calificaciones

- Sumador Restador 4 BitsDocumento10 páginasSumador Restador 4 BitsLuis Alfonso Bacab EkAún no hay calificaciones

- Sistemas DigitalesDocumento49 páginasSistemas DigitalesanaisAún no hay calificaciones

- Practica 2 Simulacion de Restador de 4 BitsDocumento12 páginasPractica 2 Simulacion de Restador de 4 BitskorinaAún no hay calificaciones

- Sumador BinarioDocumento5 páginasSumador BinarioFranco Emanuel PalaciosAún no hay calificaciones

- Circuitos AritmeticosDocumento15 páginasCircuitos AritmeticosJean Pier IzarraAún no hay calificaciones

- Electricista 2Documento3 páginasElectricista 2axefecAún no hay calificaciones

- Normas para Ensayos TC y TPDocumento1 páginaNormas para Ensayos TC y TPaxefecAún no hay calificaciones

- Ejemplo y Explicacion de Analisis CriticoDocumento3 páginasEjemplo y Explicacion de Analisis Criticoaxefec70% (10)

- Etapas de Carga de Una BateríaDocumento4 páginasEtapas de Carga de Una BateríaaxefecAún no hay calificaciones

- Consecuencias de Las Fallas EvidentesDocumento1 páginaConsecuencias de Las Fallas EvidentesaxefecAún no hay calificaciones

- Qué Es La Pirámide de MaslowDocumento7 páginasQué Es La Pirámide de MaslowaxefecAún no hay calificaciones

- Proyecto Lab de Electronica, Robot Seguidor de LineasDocumento2 páginasProyecto Lab de Electronica, Robot Seguidor de LineasaxefecAún no hay calificaciones

- Telemecanique Automatizacion y ControlDocumento98 páginasTelemecanique Automatizacion y ControlOmaira SanchezAún no hay calificaciones

- AMEF OriginalDocumento16 páginasAMEF OriginalaxefecAún no hay calificaciones

- Sugerencias Fallas Rele TermicoDocumento1 páginaSugerencias Fallas Rele TermicoaxefecAún no hay calificaciones

- Teoria ArrancadoresDocumento10 páginasTeoria ArrancadoresaxefecAún no hay calificaciones

- Radio Interferencia y Ruido Audible Generado Por El Efecto Corona en L Neas de Transmisi NDocumento6 páginasRadio Interferencia y Ruido Audible Generado Por El Efecto Corona en L Neas de Transmisi NDaniel EstradaAún no hay calificaciones

- Conectar Dos Equipos Con Un Cable CruzadoDocumento8 páginasConectar Dos Equipos Con Un Cable CruzadoaxefecAún no hay calificaciones