Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Circuitos Secuenciales

Circuitos Secuenciales

Cargado por

Alexander Jesús Pineda SánchezTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Circuitos Secuenciales

Circuitos Secuenciales

Cargado por

Alexander Jesús Pineda SánchezCopyright:

Formatos disponibles

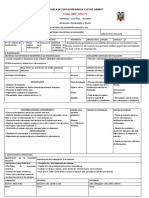

Estructura de computadores

Tema 5: Sistemas secuenciales

Tema 5:

Circuitos secuenciales

5.1 Introduccin: tablas de transicin, cronogramas.

Hemos visto como en los circuitos combinacionales, las salidas slo dependen de las entradas en el mismo instante de tiempo. Existe otro tipo de circuitos digitales en los cuales esto no es as. Son los llamados circuitos o sistemas secuenciales.

Circuitos secuenciales Son aquellos en los cuales las salidas en un instante de tiempo determinado dependen de las entradas en ese instante y en instantes anteriores de tiempo.

Como consecuencia de la definicin anterior podemos llegar a la conclusin de que este tipo de circuitos son capaces de memorizar informacin y que esta informacin en un momento dado depende de las entradas ocurridas en el circuito hasta ese momento. El circuito no es capaz de memorizar todas las entradas ocurridas hasta un instante de tiempo determinado, sino solo una cierta parte. A la informacin almacenada se le denomina estado del sistema, y el nmero mximo de informaciones almacenables es el nmero de estados posibles del sistema. El diagrama de bloques de un circuito secuencial es: E Q(t) Circuito combinacional Q(t+1) S

Elementos de almacenamiento

El circuito secuencial recibe informacin binaria de su ambiente a travs de las entradas E, las cuales, en combinacin con el estado actual Q(t) (almacenado en los elementos de almacenamiento), determinan el valor binario de las salidas S y el siguiente estado Q(t+1). Las salidas de un circuito secuencial son las salidas del circuito combinacional.

Estructura de computadores

Tema 5: Sistemas secuenciales

5.1.1 Funciones de transicin

Un circuito o sistema secuencial queda definido por dos funciones lgicas, llamadas funciones de transicin: 1. Funcin de salida: nos indica cmo depende la salida o salidas, de las entradas actuales y del estado actual. 2. Funcin de transicin de estado: nos indica como depende el nuevo estado del estado anterior y de las entradas al sistema. 5.1.1.1 Funcin de salida Si designamos por: S(t) = salidas en el mismo instante de tiempo t E(t) = entradas en el mismo instante de tiempo t Q(t) = estado en el instante de tiempo t La funcin de salida puede expresarse: S (t) = F [ E (t), Q (t) ] 5.1.1.2 Funcin de transicin de estado Nos indica si unas determinadas entradas producen un cambio en el estado y a qu estado se cambia. La funcin puede expresarse: Q(t+1) = G [ E(t), Q(t) ] Tanto F como G son funciones lgicas, exactamente iguales a las estudiadas hasta ahora. La nica novedad, que confiere a los circuitos secuenciales propiedades totalmente distintas a los combinacionales, es el hecho de que existe realimentacin. La funcin G nos da los valores Q en funcin de los propios valores Q anteriores. Las mismas variables son variables de entrada y salida de la funcin. Las funciones F y G pueden expresarse mediante tablas de verdad. como cualquier otra funcin. Por el hecho de existir realimentacin, se les denomina tablas de transicin del circuito secuencial.

5.1.2 Cronogramas

Hemos visto que los circuitos secuenciales tienen una estructura tal que las salidas dependen del tiempo, ya que el estado depende de las entradas y stas son funcin del tiempo. Aunque las tablas de transicin permiten definir un circuito secuencial, cuando ste es complejo, es ms cmodo manejar una representacin grfica de las variables en funcin del tiempo. A esta representacin se le llama cronograma. Ms adelante veremos los cronogramas de los distintos biestables. 2

Estructura de computadores

Tema 5: Sistemas secuenciales

5.2 Biestables

Los biestables son circuitos lgicos capaces de permanecer en uno de entre dos estados estables, an despus de desaparecer la causa que provoc el paso al estado alcanzado. Son, pues, capaces de almacenar una informacin binaria (1 bit).

5.2.1 Tipos de biestables.

Deben distinguirse tres aspectos en las seales de entrada que producen la transicin de un estado a otro: 1. La lgica de disparo, que determinar que el biestable cambie de estado cuando en sus entradas se d una cierta combinacin de seales. Es el modo de funcionamiento. Puede haber tantos biestables como lgicas de cambio nos imaginemos. En la prctica slo se usan 4 tipos de biestables. 2. El tipo de disparo, que determinar la forma en que las excitaciones de entrada afectan al estado del biestable. 3. El sincronismo en el disparo, que determinar si el funcionamiento del biestable se har de acuerdo con la presencia de una seal adicional a las entradas, y que se denomina seal de reloj. Combinando estos tres aspectos, los fabricantes han comercializado una gran variedad de biestables, que son suficientes para las necesidades de diseo. Podemos clasificar los biestables segn estos criterios. 1. Atendiendo a la lgica de disparo (modo de funcionamiento): q Biestables R-S q Biestables J-K q Biestables D q Biestables T 2. Atendiendo al sincronismo en el disparo y tipo de disparo: q Asncronos (latches): funcionan sin seal de reloj. q Sncronos (flip-flops): funcionan con seal de reloj. Disparo por nivel de tensin: alto ("1") o bajo ("0") Nivel alto ("1"): El biestable podr cambiar de estado cuando la seal de reloj est a "1". Nivel bajo ("0"): El biestable podr cambiar de estado cuando la seal de reloj est a "0". Disparo por flanco: de subida o bajada Flanco de subida: El biestable podr cambiar de estado en el instante en que la seal de reloj pase de "0" a "1". Flanco de bajada: El biestable podr cambiar de estado en el instante en que la seal de reloj pase de "1" a "0". 3

Estructura de computadores

Tema 5: Sistemas secuenciales

5.2.1.1 Biestables asncronos (latches) Asncronos quiere decir que funcionan sin seal de reloj; cualquier cambio en las entradas produce un cambio en las salidas, en cualquier momento. En el caso de tener varios biestables asncronos en un circuito, cada uno actuara de forma independiente a los otros.

5.2.1.2 Biestables sncronos (flip-flops) Son los que funcionan en sincronismo con una seal de reloj. A estos tambin se les llama circuitos secuenciales sincronizados, y son el tipo de circuito ms utilizados en la prctica, ya que son relativamente sencillos de disear. Un circuito secuencial sncrono emplea seales que afectan los elementos de almacenamiento slo a instantes discretos de tiempo. La sincronizacin se logra por medio de un dispositivo de sincrona, llamado generador de reloj, que produce un tren peridico de pulsos de reloj, a intervalos fijos. Esto significa que en los biestables sncronos, la tabla de transicin solo se cumple cuando se activa la seal de reloj. Si la seal de reloj no se activa, no se produce ninguna transicin. Por tanto, aunque en las entradas haya una combinacin de seales que conduzcan a una transicin de estado, sta no se producir hasta que se active la seal de reloj, y no volver a producirse una nueva transicin hasta que se active de nuevo la seal de reloj.

La seal de reloj puede activarse de dos formas: por nivel o por flanco. 5.2.1.2.1 Biestables activados por nivel (de tensin): Un biestable activado por nivel podr cambiar de estado cuando la seal de reloj est a un determinado nivel de tensin: "1" (nivel alto) o "0" (nivel bajo).

Nivel alto

Nivel bajo

5.2.1.2.2 Biestables activados por flanco: Un biestable activado por flanco ignora el pulso de reloj mientras est en un nivel constante y se dispara slo durante una transicin de la seal de reloj, de "0" a "1" (flanco de subida) o de "1" a "0" (flanco de bajada).

Reloj

Reloj

t

Flanco de subida Flanco de bajada

Estructura de computadores

Tema 5: Sistemas secuenciales

El diseo de circuitos asncronos complejos es ms difcil que el de circuitos sncronos, puesto que su comportamiento depende en gran medida de los retardos de propagacin de las puertas lgicas y de la sincrona de los cambios de las entradas. De todas formas, siempre se necesita algo de diseo asncrono, ya que: 1. los latches (elementos de almacenamiento en circuitos asncronos) se utilizan como bloques de construccin de los flip-flops (elementos de almacenamiento en circuitos sncronos). 2. Los biestables (flip-flops) que vamos a estudiar decimos que tienen entradas sncronas, ya que los datos se transfieren sincronizados con la seal de reloj, slo durante el flanco de disparo del pulso de reloj. Pero la mayora de los IC disponibles en el mercado presentan tambin entradas asncronas, las cuales pueden cambiar el estado del flip-flop independientemente del reloj. Estas entradas pueden ser por nivel alto ("1") o por nivel bajo ("0") y son prioritaras sobre las otras seales de entrada. Podemos tener las siguientes: Inicializacin o Preset (PRE): pone al biestable en estado SET ("1"). Borrado o Clear (CLR): pone al biestable en estado RESET ("0").

En su forma ms elemental, un biestable consiste en dos inversores interacoplados (realimentados), la salida de uno conectada a la entrada del otro y viceversa, como se ve en la figura: 1 0 0 1

Este circuito es capaz de estar en dos estados estables, pero para cambiar de estado, hay que actuar sobre las salidas, por lo que no es til. Se requiere un circuito de entrada, separado del de salida. Adems, se necesita que el biestable responda a una lgica de disparo, es decir, cambie de estado segn un criterio preestablecido fijo.

Ahora vamos a estudiar los 4 tipos bsicos de biestables: R-S, J-K, D y T, estudiando su tabla de de transicin, circuito y cronograma, tanto para el caso de que funcionen asncronamente (sin seal de reloj) como sncronamente (con seal de reloj). Veremos los casos en que la seal de reloj se activa por nivel (alto/bajo) o por flanco (subida/bajada).

Estructura de computadores

Tema 5: Sistemas secuenciales

5.2.2 Biestable R-S (latch)

El nico biestable que tiene sentido como asncrono es el R-S. Los dems requieren reloj para un correcto funcionamiento. Este biestable tiene dos entradas: R (Reset): permite poner a 0 el estado del biestable. S (Set): permite ponerlo a 1. Tiene dos salidas complementarias: Q y Q'. Para analizar la tabla de transicin basta con que nos fijemos en Q. La tabla de transicin es la siguiente, en forma normal y forma compacta: R 0 0 0 0 1 1 1 1 S 0 0 1 1 0 0 1 1 Q(t) Q(t+1) 0 0 1 1 0 1 1 1 0 0 1 0 0 ND 1 ND R 0 0 1 1 S 0 1 0 1 Q(t+1) Q(t) 1 0 ND Comentario No cambia Se activa Set Se activa Reset No Definido

ND = No definido

En el ltimo caso, el hecho de que el nuevo estado no est definido no quiere decir que el biestable se deteriore si R=S=1. Lo que significa es que no podemos predecir en qu estado quedar. El smbolo como bloque del biestable R-S es el siguiente: R S Q Q' R' S' Q Q'

y el circuito puede ser implementado con slo dos puertas NOR con acoplamiento cruzado y con entrada activa a nivel alto o con dos puertas NAND con entrada activa a nivel bajo: R Q Q' R' Q Q'

S'

En el caso de utilizar puertas NAND, las rdenes Reset y Set suceden para entradas a nivel bajo (0); en este caso, el biestable se llama biestable R'S', y su tabla de verdad es todo invertido (R=S=0 no permitido, etc.)

Estructura de computadores

Tema 5: Sistemas secuenciales

Vamos a explicar el funcionamiento del biestable R-S (latch) con el primer circuito (con puertas NOR). Lo que hacemos es cambiar los valores de las dos entradas R y S y observaremos las seales de salida Q y Q'. R

1

Q Q'

Suponemos que R=S=Q=0 (nivel bajo). Dado que la salida Q se realimenta a una entrada de la puerta 2 y su otra entrada es S=0, la salida de la puerta 2 tiene que ser Q'=1. Pero esta salida est acoplada de nuevo a una entrada de la puerta 1, asegurando as que su salida sea Q=0, es decir, el biestable no cambia de estado. Cuando la salida Q est a nivel bajo (Q=0), el latch se encuentra en estado RESET ("0") y permanecer indefinidamente en l hasta que se le aplique un nivel alto en la entrada S (S=1). Al tener S=1, la salida de la puerta 2 se pone a nivel bajo (Q'=0). Como tenemos que R=0 y Q'=0, la salida de la puerta 1 se pone a nivel alto (Q=1). Este nivel alto en la salida Q se realimenta a una de las entradas de la puerta 2, asegurando que su salida Q' permanece a nivel bajo (Q'=0) incluso cuando se elimine el nivel alto de la entrada S (S=0). Cuando la salida Q est a nivel alto (Q=1), el latch se encuentra en estado SET ("1"), y permanecer indefinidamente en l hasta que se le aplique un nivel alto en la entrada R (R=1). Si estando en este estado SET (Q=1), eliminamos simultnemente los niveles altos de las dos entradas (R=S=0), como la salida Q se realimenta en una entrada de la puerta 2, y la otra entrada es S=0, su salida estar a nivel bajo (Q'=0). Como esta salida est acoplada de nuevo a una entrada de la puerta 1, y la otra entrada es R=0, su salida estar a nivel alto (Q=1). Vemos que el biestable no cambia de estado. En operacin normal, las salidas de un latch (Q y Q') son siempre complementarias una de la otra. Sin embargo, se produce una condicin de funcionamiento no vlida en un biestable R-S cuando se aplican simultneamente niveles altos a las dos entradas R y S ( R=S=1). En esta situacin, las dos salidas deberan estar forzsamente a nivel bajo (Q=Q'=0), lo que viola la condicin de complementariedad de las salidas. Adems, si se eliminan simultnemente los niveles altos de las dos entradas ( R=S=0), las dos salidas van a tender al nivel alto y, dado que siempre va a existir un cierto retraso de propagacin de la seal elctrica a travs de las puertas, una de las puertas dominar en la transicin a nivel alto (una de las puertas siempre ser ms lenta que la otra). Esto har que la salida de la puerta ms lenta permanezca a nivel bajo. Cuando se produce esta situacin, no se puede predecir el siguiente estado del latch. Si los tiempos de propagacin de las dos puertas fueran exactamente iguales se produciran oscilaciones 0,1,0,1,... 7

Estructura de computadores

Tema 5: Sistemas secuenciales

Los cronogramas correspondientes a un biestable R-S con puertas NOR y NAND son los siguientes. Como estamos analizando el biestable como asncrono, no depender de una seal de reloj, sino de cmo cambiemos las entradas R y S y del estado anterior. Igual que hemos hecho antes, lo que hacemos ahora es cambiar los valores de las dos entradas R y S y observaremos las seales de salida Q y Q'. Los estados de las entradas R y S los hemos elegido arbitrariamente para realizar los cronogramas, partiendo en ambos casos de que Q se encuentra a nivel bajo (Q=0).

R S Q Q' t

Cronograma biestable R-S (puertas NOR)

Estados no definidos

Mantiene el estado anterior

NOTA: La condicin R=S=1 origina un modo de funcionamiento no vlido del biestable, lo que es un gran inconveniente en cualquier latch de tipo RESET-SET. NOTA: Mientras no se diga lo contrario, de ahora en adelante supondremos que los tiempos de propagacin de las puertas lgicas que componen los biestables son nulos, con lo cual la respuesta del biestable ser inmediata.

R' S' Q Q' t

Cronograma biestable R-S (puertas NAND)

Mantiene el estado anterior

NOTA: en este caso, la condicin R=S=0 tiene el mismo problema que antes. 8

Estructura de computadores

Tema 5: Sistemas secuenciales

Este tipo de biestable, y todos los que vamos a ver, pueden tener una entrada adicional de habilitacin (STROBE o ENABLE), que puede activarse en estado alto ("1") o bajo ("0"). Cuando esta seal est activa, el biestable funciona (puede cambiar de estado); cuando est inactiva, no funciona. En el caso del biestable R-S, debemos aadir la siguiente lgica al circuito para tener dicha entrada de habilitacin. El smbolo lgico o de bloques es el mismo que antes pero aadimos esta entrada de habilitacin. R Q EN S Q'

El biestable R-S puede funcionar de forma asncrona (tal como hemos visto hasta ahora), pero tambin de forma sncrona, es decir, utilizando una seal de reloj como entrada de habilitacin. Cuando enumeramos los distintos tipos de biestables, dentro de los sncronos (flip-flops) vimos que la seal de reloj se poda activar por "nivel" o por "flanco". Los smbolos lgicos o de bloques de los biestables R-S sncronos son los siguientes. Todos tienen una entrada adicional de reloj (Clock). En el caso de los flip-flops disparados por flanco colocamos un tringulo dentro del bloque en la entrada del reloj. Este tringulo se denomina "indicador de entrada dinmica". Para distinguir si se activa por flanco de subida o por flanco de bajada, colocamos un crculo (como los de negacin) en la entrada del reloj. Activados por nivel: R

Clock

R

Clock

Q'

Q'

Activado por nivel alto ("1")

Activado por nivel bajo ("0")

Activados por flanco: R

Clock

R

Clock

Q'

Q'

Activado por flanco de subida

Activado por flanco de bajada

NOTA: Esta misma nomenclatura se utiliza en el resto de biestables.

Estructura de computadores

Tema 5: Sistemas secuenciales

Vamos a analizar ahora los cronogramas correspondientes a estos cuatro casos. Al tratarse de biestables sncronos, ahora dependern de una seal de reloj. Igual que antes, cambiamos las entradas R y S y comprobamos las seales de salida Q y Q'. Podemos poner los cuatro casos en un slo cronograma.

Reloj R S Qna Qnb Qfs Qfb t

Cronograma biestables R-S (sncronos)

Donde: Qna = Salida biestable activado por nivel alto ("1") Qnb = Salida biestable activado por nivel bajo ("0") Qfs = Salida biestable activado por flanco de subida Qfb = Salida biestable activado por flanco de bajada Nota: Las salidas Q' las ignoramos, puesto que su seal simplemente es la inversa de Q. Recuerda:

q

Un flip-flop activado por nivel slo puede cambiar mientras la seal de reloj est en un determinado nivel: nivel alto ("1") o nivel bajo ("0"). Un flip-flop activado por flanco no puede cambiar de estado excepto en el flanco de disparo de un pulso de reloj. Las entradas R y S se pueden cambiar en cualquier momento sin que vare la salida, salvo en esos instantes. Para detectar los flancos, se utiliza un circuito "detector de transicin de impulsos", que se conecta a la entrada ENABLE.

Ejemplo de IC : el 74LS279 tiene 4 latches R'S'.

10

Estructura de computadores

Tema 5: Sistemas secuenciales

5.2.3 Biestable J-K

El flip-flop J-K es uno de los ms ampliamente utilizados. Las denominaciones J y K de sus entradas no tienen ningn significado conocido, excepto el hecho de que son dos letras consecutivas del alfabeto. Es similar al R-S, pero elimina la indeterminacin que se presenta cuando las dos entradas son "1". En este caso, para esa combinacin el estado cambia de valor, es decir, si tena el valor "0" pasa a valor "1" y viceversa. La razn de utilizar el biestable R-S es porque es mucho ms simple y econmico que el biestable J-K. Hay muchos casos en que tenemos la certeza de que el circuito conectado al biestable no podr activar simultnemente las dos entradas a la vez ("1"). La tabla de transicin es la siguiente, en forma normal y forma compacta: J 0 0 0 0 1 1 1 1 K 0 0 1 1 0 0 1 1 Q(t) Q(t+1) 0 0 1 1 0 0 1 0 0 1 1 1 0 1 1 0 J 0 0 1 1 K 0 1 0 1 Q(t+1) Q(t) 0 1 Q(t)' Comentario No cambia Se activa Reset Se activa Set Invierte Q(t)

ND = No definido

El smbolo como bloque es: J

Clock

J

Clock

Q'

Q'

Activado por flanco de subida

Activado por flanco de bajada

Ejemplo de IC : el 74HC112 tiene 2 flip-flops J-K (flanco de bajada), con entradas asncronas de inicializacin y borrado.

11

Estructura de computadores

Tema 5: Sistemas secuenciales

Ejemplo de cronograma: se aplican las siguientes formas de onda a las entradas J, K y de reloj. Determinar la salida Q para un biestable activado por flanco de subida y para otro activado por flanco de bajada, suponiendo que se encuentran inicialmente en estado RESET ("0").

Reloj J K Qfs Qfb

Cronograma biestables J-K (flanco de subida y flanco de bajada)

Donde: Qfs = Salida biestable activado por flanco de subida Qfb = Salida biestable activado por flanco de bajada El biestable J-K no tiene sentido como asncrono: Supongamos que el estado inicial es Q(0)=0 y que J=K=1. Mirando la tabla de transicin vemos que, para las entradas indicadas, el estado cambia al estado Q(1)=1. Ahora bien, apenas ha cambiado, como las seales de entrada siguen indicando que cambie, volver a cambiar a un estado Q(2)=0, y as sucesivamente. Vemos que el funcionamiento es inestable, pues el estado estara cambiando continuamente. Si por el contrario, dotamos al biestable J-K de una entrada de reloj que sincronice las transiciones, el problema puede solucionarse. Para que efectivamente se solucione, es necesario que la seal de reloj se active durante un periodo de tiempo muy breve, de tal modo que en este periodo no pueda haber ms que una transicin. Es conveniente pues, que la seal de reloj acte por flanco, reduciendo as al mnimo el perodo de tiempo en el cual est activa. Para que las seales de entrada puedan ser tenidas en cuenta cuando se producen flancos de la seal de reloj, debern estar en unos niveles claramente definidos. Por tanto, las restantes seales de entrada deben actuar siempre por nivel.

12

Estructura de computadores

Tema 5: Sistemas secuenciales

Finalmente, como ya hemos comentado, hay biestables sncronos con entradas asncronas. El ms utilizado es el J-K sncrono, con dos entradas asncronas adicionales, llamadas Preset (puesta a "1") y Clear (puesta a "0"), anlogas a las Set y Reset de un biestable R-S. Estas entradas PRE' y CLR' (asncronas) son prioritarias sobre las entradas sncronas, y se activan por nivel bajo (las complementamos), por lo que deben mantenerse en estado alto para el funcionamiento sncrono. El smbolo de este biestable es:

Preset Set (Biestable R-S)

PRE' J

Clock

Q Q' CLR'

Clear Reset (Biestable R-S)

Ejemplo de cronograma para el biestable anterior, teniendo en cuenta que Q est inicialmente a nivel bajo:

Reloj J K PRE' CLR' Qfs Qfb t

Cronograma biestables J-K (sncronos y con 2 entradas asncronas)

Debera seguir a "1" hasta el siguiente flanco de subida pero la entrada CLR' se ha activado.

Debera cambiar a "0", pero la entrada PRE' se ha activado; ya no podr cambiar hasta el prximo flanco.

Donde: PRE' = Entrada asncrona PRESET (se ignora cuando es "1") CLR' = Entrada asncrona CLEAR (se ignora cuando es "1") Qfs = Salida biestable activado por flanco de subida Qfb = Salida biestable activado por flanco de bajada

13

Estructura de computadores

Tema 5: Sistemas secuenciales

5.2.4 Biestable D (Datos)

Slo tiene una entrada D, y su funcionamiento es tal, que el estado siguiente Q(t+1) es la entrada D, independientemente del estado actual del biestable Q(t). Su tabla de transicin es: D 0 0 1 1 Q(t) Q(t+1) 0 0 1 0 0 1 1 1 D 0 1 Q(t+1) Comentario 0 No depende de Q(t) 1 No depende de Q(t)

Puede observarse que el nuevo estado coincide siempre con la entrada D. Si lo definimos as, esto no es un biestable, ya que no almacena ninguna informacin. Lo que ocurre es que este biestable no tiene sentido como asncrono. El biestable D sncrono es un elemento tpico de almacenamiento gobernado por la seal de reloj. La seal lgica que haya en la entrada D, no modificar el estado Q hasta que se active la seal de reloj. Esto constituye una memoria elemental de 1 bit, ya que el valor presente en la entrada D, queda almacenado al llegar la seal de reloj. Para cambiar el contenido de esta celdilla de memoria, no hay ms que colocar el nuevo valor en la entrada D y activar la seal de reloj, momento en el cual el nuevo valor queda almacenado en el biestable. Su smbolo como bloque es: D

Clock

D

Clock

Q'

Activado por flanco de subida

Q'

Activado por flanco de bajada

Puede obtenerse tambin a partir de un biestable J-K y un inversor, segn podemos observar en el esquema siguiente:

J

Clock

Q'

J 0 0 1 1

K 0 1 0 1

Q(t+1) Q(t) 0 1 Q(t)'

Biestable D a partir de un J-K

14

Estructura de computadores

Tema 5: Sistemas secuenciales

Ejemplo de IC : el 74AHC74 tiene 2 flip-flops D (flanco de subida), con entradas asncronas de inicializacin y borrado. Vamos a analizar ahora los cronogramas.

Reloj D Qna Qnb Qfs Qfb t

Cronograma biestables D (sncronos)

Donde: Qna = Salida biestable activado por nivel alto ("1") Qnb = Salida biestable activado por nivel bajo ("0") Qfs = Salida biestable activado por flanco de subida Qfb = Salida biestable activado por flanco de bajada Nota: Las salidas Q' las ignoramos, puesto que su seal simplemente es la inversa de Q.

Recuerda:

q

Un flip-flop activado por nivel slo puede cambiar mientras la seal de reloj est en un determinado nivel: nivel alto ("1") o nivel bajo ("0"). Un flip-flop activado por flanco no puede cambiar de estado excepto en el flanco de disparo de un pulso de reloj. Las entradas R y S se pueden cambiar en cualquier momento sin que vare la salida, salvo en esos instantes.

15

Estructura de computadores

Tema 5: Sistemas secuenciales

5.2.5 Biestable T

Tiene una nica entrada T. Si esta entrada est inactiva ("0"), el estado no cambia. Si T est activa ("1"), el estado cambia. Su tabla de transicin es: T 0 0 1 1 Q(t) Q(t+1) 0 0 1 1 0 1 1 0 T 0 1 Q(t+1) Q(t) Q(t)' Comentario No cambia el estado Invierte el estado

Su smbolo como bloque es: T

Clock

T

Clock

Q'

Activado por flanco de subida

Q'

Activado por flanco de bajada

Puede comprobarse que un biestable J-K con las dos entradas unidas acta como un biestable T, razn por la cual ste no existe comercialmente, slo existe a nivel terico. T J

Clock

Q'

J 0 0 1 1

K 0 1 0 1

Q(t+1) Q(t) 0 1 Q(t)'

Biestable T a partir de un J-K

Por tanto, todo lo dicho para el biestable J-K es aplicable para el biestable T. Reloj T Qfs Qfb

Cronograma biestables T (flanco de subida y bajada)

NOTA: Si lo hacemos por nivel (alto o bajo), el biestable estar oscilando continuamente entre 0 y 1, cuando T=1 en el nivel correspondiente, y despus no sabremos en que estado se ha quedado.

16

Estructura de computadores

Tema 5: Sistemas secuenciales

5.2.6 Flip-flops Maestro-Esclavo

Otra clase de flip-flops son los maestro-esclavo disparados por nivel, que han sido reemplazados progresivamente por los dispositivos disparados por flanco. Consiste en dos latches R-S con una entrada de habilitacin (reloj), un inversor y algn circuito adicional. Al latch de la izquierda lo llamaremos "maestro", y al de la derecha lo llamaremos "esclavo". La diferencia es que el "maestro" est sincronizado con una seal de reloj, y el "esclavo" lo est por una seal de reloj invertida y se controla mediante las salidas del "maestro" en lugar de por las entradas externas. El "maestro" podr cambiar de estado durante los flancos de subida, y este estado se transfiere al "esclavo" durante el siguiente flanco de bajada. El estado del "esclavo" depende nicamente del estado del "maestro" en el momento que se produce el flanco de bajada, y aparece en sus salidas Q y Q'. 5.2.6.1 Biestable R-S maestro-esclavo

S Reloj R Q

S

Clock

S

Clock

Q'

Q'

Q'

La tabla de verdad es la misma que la estudiada para biestables R-S. J 0 0 1 1 K 0 1 0 1 Q(t+1) Comentario Q(t) No cambia 0 Reset 1 Set Q(t)' Invierte Q(t) R 0 0 1 1 S 0 1 0 1 Q(t+1) Q(t) 1 0 ND Comentario No cambia Set Reset No Definido

Podemos ver un ejemplo de funcionamiento en el siguiente cronograma:

Reloj S = Sm R = Rm Qm = S e Q = Qe

Cronograma biestable J-K Maestro-Esclavo

17

Estructura de computadores

Tema 5: Sistemas secuenciales

5.2.6.2 Biestable J-K maestro-esclavo

J Reloj K

S

Clock

S

Clock

Q'

Q'

Q'

La tabla de verdad es la misma que la estudiada para biestables J-K. J 0 0 1 1 K 0 1 0 1 Q(t+1) Comentario Q(t) No cambia 0 Reset 1 Set Q(t)' Invierte Q(t) R 0 0 1 1 S 0 1 0 1 Q(t+1) Q(t) 1 0 ND Comentario No cambia Set Reset No Definido

18

Estructura de computadores

Tema 5: Sistemas secuenciales

5.3 Registros y Contadores

Hasta ahora hemos estudiado circuitos combinacionales y circuitos secuenciales por separado. En este apartado vamos a unir ambos conceptos, para poder analizar los bloques funcionales secuenciales bsicos, como son los registros y los contadores. Los registros y los contadores son bloques funcionales secuenciales que se utilizan extensamente en el diseo de sistemas digitales. Los registros son tiles para almacenar y manipular informacin; los contadores se emplean en los circuitos que secuencian y controlan las operaciones de los sistemas digitales.

5.3.1 Registros

Un registro no es ms que una agrupacin de biestables del mismo tipo. Puesto que un biestable es capaz de almacenar 1 bit de informacin, si tenemos "n" biestables, el registro ser capaz de almacenar "n" bits de informacin binaria (de forma temporal). El registro ms sencillo consta tan slo de flip-flops sin puertas lgicas externas. Estas puertas son las que determinan los nuevos datos a almacenar.

5.3.1.1 Registros de almacenamiento (tipo D) El registro tipo D es un conjunto de biestables D y es el ms utilizado como almacn temporal de informacin. Cada entrada D se conecta a una lnea de entrada de informacin y cada salida Q se conecta a una lnea de salida de informacin. Por otro lado, todas las seales de reloj van unidas entre s, activando todos los flip-flops por flanco (de subida o bajada) o por nivel para que la informacin se almacene en todos los biestables al mismo tiempo. El esquema es el de la figura (para n=4 bits): Q3 Q2 Q1 Q0

Q

Clock

Q

Clock

Q

Clock

Q

Clock

R Reloj Clear

D3

D2

D1

D0

19

Estructura de computadores

Tema 5: Sistemas secuenciales

En este caso, la seal de reloj es con flanco de subida. Adems, podemos observar como estos flip-flops tienen una entrada asncrona de Reset activada por 0 (Clear') para la inicializacin del registro con ceros antes de su operacin, aunque esto es opcional (depende del uso que vayamos a darle al registro en el sistema). Lo que haremos ser tener la entrada Clear' a un valor de "1" durante la operacin normal sincronizada, haremos que sea "0" slo cuando queramos inicializar el registro. La transferencia de informacin nueva a un registro se conoce como carga del registro. Como estamos utilizando una seal de reloj por flanco para la sincronizacin de todos los flip-flops, todos los bits del registro se cargan de manera simultnea. Por ello decimos que la carga se hace en paralelo. La entrada de reloj en los biestables tipo D puede ser por flanco o por nivel. La actuacin por flanco requiere un circuito mucho ms caro que por nivel y no presenta ventajas salvo en casos muy particulares. Por esta razn, en los computadores se utilizan casi siempre registros D activados por nivel, pero con una seal de reloj, realmente se trata de actuacin por nivel con seal de reloj de corta duracin.

5.3.1.2 Registros de desplazamiento Son registros en los cuales la informacin contenida en un biestable puede ser transferida al biestable adyacente. La transferencia se realiza en todos los biestables simultneamente, es decir, la informacin contenida en el biestable 1 pasa al 2, al mismo tiempo que la informacin que haba antes en el 2 pasa al 3, y as sucesivamente. Estn conectados en cascada. La nueva informacin en el primer biestable se toma de una entrada, y la informacin del ltimo biestable se pierde. Hay varios tipos de registros de desplazamiento : 1. Atendiendo a la entrada de informacin en el registro: 1.1. Entrada paralelo : se puede modificar el valor de todos los biestables a la vez (igual que en un registro tipo D). 1.2. Entrada serie : slo hay una entrada conectada a un biestable (como hemos descrito anteriormente). 2. Atendiendo a la salida de informacin: 2.1. Salida paralelo : todos los biestables son accesibles (sus salidas). 2.2. Salida serie : slo el ltimo biestable (su salida) es accesible. Los datos van saliendo uno detrs de otro, mediante desplazamientos sucesivos. 3. Atendiendo al sentido del desplazamiento : 3.1. Desplazamiento slo hacia la derecha / izquierda. 3.2. Desplazamiento en ambos sentidos, no simultneo. 3.3. Rotacin hacia la izquierda / derecha.

20

Estructura de computadores

Tema 5: Sistemas secuenciales

Para caracterizar o designar un registro de desplazamiento hay que indicar todas sus caractersticas: tipo de entrada, tipo de salida y sentido del desplazamiento. Por ejemplo, la designacin: "SRG8" indica que es un registro de desplazamiento (SRG, Shift Register) con una capacidad de 8 bits. Suponiendo registros de 4 bits, los posibles movimientos de datos en los registros de desplazamiento son:

Caso 1 Entrada: Serie Salida : Serie Desplazamiento: Hacia la derecha Caso 2 Entrada: Serie Salida : Serie Desplazamiento: Hacia la izquierda

Entrada

Salida

Salida

Entrada

Caso 3 Entrada: Paralelo Salida : Serie

Entradas

Caso 4 Entrada: Serie Salida : Paralelo

Caso 5 Entrada: Paralelo Salida : Paralelo

Entradas

Salida

Entrada

Salidas

Salidas

Caso 6 Desplazamiento: Rotacin a la derecha

Caso 7 Desplazamiento: Rotacin a la izquierda

Sus aplicaciones son muy numerosas. Entre ellas podemos citar: Conversin paralelo-serie y viceversa Rotaciones de los datos (multiplicar y dividir por 2 n ) Registros de memoria transitorios (buffers) Sistemas para unidades aritmticas (+,,/) Como retardo de lnea digital Como generadores de secuencias

21

Estructura de computadores

Tema 5: Sistemas secuenciales

El circuito puede implementarse con biestables R-S, J-K o D sncronos, con seal de reloj activa por flanco. Veamos unos ejemplos de circuitos (esquemas). Caso 1: Un registro de desplazamiento de 4 bits con entrada y salida serie, desplazamiento a derecha. Biestables R-S:

Entrada

S1 Q1

Clock

S2 Q2

Clock

S3 Q3

Clock

S4 Q4

Clock

Salida

R1 Q1'

Reloj

R2 Q2'

R3 Q3'

R4 Q'

Vamos a construir un cronograma para comprobar el funcionamiento del registro. Suponemos que el registro se activa por flanco de subida.

Reloj E' = R1 E = S1 Q1 Q2 Q3 S = Q4 t

Cronograma del registro con biestables R-S (sncronos con flanco de subida)

22

Estructura de computadores

Tema 5: Sistemas secuenciales

Biestables D:

Entrada

D1 Q1

Clock

D2 Q2

Clock

D3 Q3

Clock

D4 Q4

Clock

Salida

Q1'

Reloj

Q2'

Q3'

Q4'

Vamos a ver dos ejemplos de cronogramas, para comprobar el funcionamiento, uno con flanco de subida y otro con flanco de bajada.

Reloj E = D1 Q1 Q2 Q3 S = Q4 t

Cronograma del registro con biestables D (sncronos con flanco de subida)

Reloj E = D1 Q1 Q2 Q3 S = Q4 t

Cronograma del registro con biestables D (sncronos con flanco de bajada)

23

Estructura de computadores

Tema 5: Sistemas secuenciales

Caso 4: Un registro de desplazamiento de 4 bits con entrada serie y salida paralelo. Biestables D:

Entrada

D1 Q1

Clock

D2 Q2

Clock

D3 Q3

Clock

D4 Q4

Clock

Q1'

Reloj

Q2'

Q3'

Q4'

S1

S2

S3

S4

Salidas de datos en paralelo

Caso 5: Un registro de desplazamiento de 4 bits con entrada paralelo y salida paralelo. Biestables D:

Entradas de datos en paralelo

E1

E2

E3

E4

D1 Q1

Clock

D2 Q2

Clock

D3 Q3

Clock

D4 Q4

Clock

Q1'

Reloj

Q2'

Q3'

Q4'

S1

S2

S3

S4

Salidas de datos en paralelo

Como podemos observar, en este tipo de registros no se realiza ningn desplazamiento, por lo que no se puede considerar como registro de desplazamiento.

24

Estructura de computadores

Tema 5: Sistemas secuenciales

5.3.2 Contadores

Un contador es un registro que pasa por una secuencia predeterminada de estados al aplicrsele pulsos de reloj. Bsicamente, son circuitos capaces de contar los impulsos que llegan por una lnea. El valor de la cuenta se expresa mediante un cdigo, que en la mayora de los casos es binario natural, y a veces, BCD. Los impulsos de entrada que son capaces de detectar son los flancos de la seal de entrada. Dado que el estado del contador debe cambiar cuando llega un flanco de la seal de entrada, se utilizan biestables T para construir los contadores, conectando la lnea con los impulsos a contar a la entrada de reloj. Tambin podemos utilizar biestables J-K. 5.3.2.1 Tipos de contadores 1. Atendiendo al cdigo que cuentan 1.1. Binario (natural) 1.2. BCD 1.3. En anillo 1.4. En Gray 1.5. Johnson 2. Atendiendo al sentido de conteo 2.1. Contador hacia arriba (ascendentes) 2.2. Contador hacia abajo (descenentes) 2.3. Contador en ambos sentidos, no simultneos 3. Atendiendo a la posibilidad de preseleccin 3.1. Contador con carga en paralelo 3.2. Contador con puesta a cero inicial solamente 4. Atendiendo a la forma de propagarse la seal de reloj internamente 4.1. Contador asncrono (contadores con propagacin) 4.2. Contador sncrono con acarreo serie 4.3. Contador sncrono con acarreo paralelo Para caracterizar un contador se indican todas las posibilidades. Por ejemplo, un contador BCD Aiken ascendente asncrono.

Un contador es asncrono cuando la salida del biestable es la entrada de reloj del biestable siguiente. Estos contadores llevan una secuencia (ascendente o descencente) que se repite indefinidamente. Un contador es sncrono cuando la seal de reloj se conecta a la entrada de reloj de cada uno de los biestables. Se utiliza cuando los estados por los que pasa (secuencia) no son correlativos. Por ejemplo: 1,8,7,4, etc.

25

Estructura de computadores

Tema 5: Sistemas secuenciales

5.3.2.2 Diseo de contadores asncronos Supongamos un contador de mdulo N, siendo (N-1) el mayor nmero representable que contamos. Seguiremos los siguientes pasos: 1. Calcular el nmero de biestables (flip-flops) necesarios: n. Deberemos cumplir que: 2n-1 < N 2n Donde: N = Nmero de estados (0..N-1) n = Nmero de biestables (T o J-K). 2. Conectar las entradas de reloj de todos los biestables. Activacin del reloj Flanco de bajada Flanco de subida Tipo contador Ascendente Descendente Ascendente Descendente Salida a conectar a la entrada de reloj del siguiente biestable Q Q' Q' Q

3. Conectar las entradas de todos los biestables a "1" lgico. Biestables T: conectando T="1" Biestables J-K: conectando J=K="1" Ambos tipos podrn tener o no entradas asncronas de PRESET Y CLEAR. Slo si nuestros biestables tienen una entrada asncrona PRESET seguimos con los siguientes pasos: 4. Escribir el nmero N-1 en binario. 5. Para todos los biestables que tienen un 1 en dicho valor binario, conectar su salida Q junto con la seal de reloj en una puerta NAND. 6. Conectar la salida de la puerta NAND a las entradas PRESET del resto de biestables, los que su valor binario era 0 en el valor N-1. Por otro lado, slo si nuestros biestables tienen una entrada asncrona CLEAR seguimos con los siguientes pasos: 4. Escribir el nmero N-1 en binario. 5. Para todos los biestables que tienen un 0 en dicho valor binario, conectar su salida Q junto con la seal de reloj en una puerta NAND. 6. Conectar la salida de la puerta NAND a las entradas CLEAR del resto de biestables, los que su valor binario era 1 en el valor N-1. Lgicamente, si tenemos biestables con las dos entradas asncronas PRESET y CLEAR podemos utilizar cualquiera de los dos mtodos descritos. Si estas entradas se activan a nivel bajo lo hacemos como hemos descrito; si se activan por nivel alto, utilizaremos una puerta AND en lugar de la NAND.

26

Estructura de computadores

Tema 5: Sistemas secuenciales

Un contador asncrono es de mdulo N cuando cuenta todos los estados desde el 0 hasta el N-1 correlativamente. Si nos piden disear un contador asncrono mdulo 5, ste contar 0,1,2,3,4. Lo que hacemos utilizar biestables con entrada CLEAR, detectamos la ltima combinacin (N-1) y procedemos como hemos explicado para biestables CLEAR, para que se reinicie la cuenta al llegar a N-1. Esto no es necesario si fuera mdulo potencia de 2, ya que se reinicia slo. Por ejemplo, mdulo 8.

Ejemplo Vamos a ver como ejemplo , el circuito y cronograma de un contador asncrono de 3 bits, binario, con cuenta hacia arriba, sin preseleccin (PRESET) ni puesta a cero (CLR). Utilizamos biestables T para realizar el circuito. Recordemos la tabla de transicin del biestable T : T 0 0 1 1 Q(t) Q(t+1) 0 0 1 1 0 1 1 0 T 0 1 Q(t+1) Q(t) Q(t)' Comentario No cambia el estado Invierte el estado

Necesitaremos "n" biestables. Tenemos que N = 8 estados. Se debe cumplir: 2n-1 < N 2n 2n-1 < 8 2n n 3

Con cuenta hacia arriba: Q1 (LSB) "1"

Pulsos de reloj

Q2 T2 Q2

Clock

Q3 (MSB) "1" T3 Q3

Clock

T1 Q1

Clock

"1"

Q1'

Q2'

Q3'

El funcionamiento se puede analizar en el siguiente cronograma:

Reloj

Q1 Q2 Q3

0 1 0 1 0 1 0 1 0 1

Cronograma reloj asncrono 3 bits (cuenta hacia arriba)

27

Estructura de computadores

Tema 5: Sistemas secuenciales

Con cuenta hacia abajo: Lo nico que tenemos que cambiar en el circuito anterior es la seal de reloj, para que se active por flanco de subida. Q1 (LSB) "1"

Pulsos de reloj

Q2 T2 Q2

Clock

Q3 (MSB) "1" T3 Q3

Clock

T1 Q1

Clock

"1"

Q1'

Q2'

Q3'

El funcionamiento se puede analizar en el siguiente cronograma:

Reloj

Q1 Q2 Q3

1 0 1 0 1 0 1 0 1

Cronograma reloj asncrono 3 bits (cuenta hacia abajo)

Otra posibilidad hubiera sido conectar la salida Q' de cada biestable a la entrada de reloj del siguiente, en vez de Q, manteniendo el flanco de bajada. Q1 (LSB) "1"

Pulsos de reloj

Q2 T2 Q2

Clock

Q3 (MSB) "1" T3 Q3

Clock

T1 Q1

Clock

"1"

Q1'

Q2'

Q3'

La mayor parte de los contadores asncronos no funciona bien para frecuencias elevadas, sobre todo cuando implementamos contadores con mdulo que no son potencia de 2. Cuando utilizamos contadores que si son potencia de 2 (2,4,8,...), estos funcionan bastante bien, tanto en modo ascendente como en modo descendente. Sin embargo, en los otros casos conviene utilizar contadores sncronos.

28

Estructura de computadores

Tema 5: Sistemas secuenciales

5.3.2.3 Diseo de contadores sncronos Para los contadores sncronos podemos utilizar cualquier tipo de biestables: R-S, J-K, D y T. El procedimiento de diseo de contadores sncronos es: 1. Calcular el nmero de biestables (flip-flops) necesarios: n. Deberemos cumplir que: Donde: 2n-1 < N 2n N = Nmero de estados n = Nmero de biestables (R-S, J-K, D T).

2. Escribimos la tabla de funcionamiento del biestable . 3. Construimos una tabla de transiciones y excitaciones correspondientes a las entradas del biestable utilizado. En esta tabla, averiguamos el valor que deben de tener las entradas del biestable para que en la salida se produzca cualquier transicin (0-0, 0-1, 1-0, 1-1). 4. Utilizando esta ltima tabla, construimos la tabla de transiciones y excitaciones del contador. En esta tabla averiguamos el valor que debemos tener en las entradas para producir la secuencia de estados pedida. Lo que conocemos son las salidas Q de los biestables, puesto que son las combinaciones que queremos que cuente. Por tanto, ponemos como posibles combinaciones de entrada los distintos valores que va a contar en binario, y se trata de calcular las funciones lgicas correspondientes a cada una de las entradas de los biestables en funcin de las salidas. 5. Simplificar por Karnaugh las funciones lgicas obtenidas. Las tablas de Karnaugh se pueden obtener directamente de la tabla anterior. 6. Realizacin del circuito a partir de las funciones simplificadas. 7. Comprobar el funcionamiento realizando un cronograma.

29

Estructura de computadores

Tema 5: Sistemas secuenciales

Ejemplo Vamos a disear un contador que siga la siguiente secuencia con biestables J-K: 0, 4, 6, 1, 14, 7 y vuelvan a repetirse. Utilizamos biestables J-K, sin preseleccin (PRESET) ni puesta a cero (CLR). 1. Nmero de biestables: Tenemos 6 posibles estados (N=6), por tanto: 2n-1 < N 2n 2n-1 < 16 2n En este ejemplo vamos a utilizar n=4. 2. Tabla de funcionamiento del biestable: J 0 0 1 1 K 0 1 0 1 Q(t+1) Q(t) 0 1 Q(t)' Comentario No cambia Reset Set Invierte Q(t) n 3

3. Tabla de transiciones y excitaciones de las entradas del biestable: Transicin Q(t) Q(t+1) 00 01 10 11 J 0 1 X X K X X 1 0 Qu valores pueden tomar las entradas J-K para conseguir dicha transicin en la salida?

4. Tabla de transiciones y excitaciones del contador: Q1 0 0 0 0 1 0 Q2 0 1 1 0 1 1 Q3 0 0 1 0 1 1 Q4 0 0 0 1 0 1 J1 0 0 0 1 X 0 K1 X X X X 1 X J2 1 X X 1 X X K2 X 0 1 X 0 1 J3 0 1 X 1 X X K3 X X 1 X 0 1 J4 0 0 1 X 1 X K4 X X X 1 X 1

Para cada biestable x, rellenamos las columnas de Jx y Kx con los valores que deben tomar las entradas para que en el siguiente estado cambie su correspondiente Qx al valor del siguiente valor de la secuencia; si fuese el ltimo, entonces consideramos de nuevo el primero para que comience de nuevo el ciclo.

30

Estructura de computadores

Tema 5: Sistemas secuenciales

5. Simplificamos por Karnaugh las funciones de las entradas.

q

J1 = Q2' 00 0 0 X X 01 1 X X X 11 X 0 X X 10 X 0 X X

J3 = Q2+Q4 00 0 1 X X 01 1 X X X 11 X X X X 10 X X X X

Q3 Q4 Q1Q2 00 01 11 10

Q3 Q4 Q1Q2 00 01 11 10

K1 = 1

K3 = Q1' 00 X X X X 01 X X X X 11 X 1 X X 10 X 1 0 X

No es necesario construir un mapa de Karnaugh pues todas las casillas sern X menos un "1". Como podremos hacer un grupo de 16 casillas (todas), la funcin lgica ser "1".

Q3 Q4 Q1Q2 00 01 11 10

q q q

J4 = Q3 00 0 0 X X 01 X X X X 11 X X X X 10 X 1 1 X

J2 = 1 K2 = Q1' 00 X X X X 01 X X X X 11 X 1 X X 10 01 X 1 0 X

q

Q3 Q4 Q1Q2 00 01 11 10

Q3 Q4 Q1Q2 00

11 10

K4 = 1

31

Estructura de computadores

Tema 5: Sistemas secuenciales

6. Circuito a partir de las funciones simplificadas. Q1 (MSB) Q2 Q3 Q4 (LSB)

J1

CLK1

Q1 Q1'

J2

CLK2

Q2 Q2'

J3

CLK3

Q3 Q3'

J4

CLK3

Q4 Q4'

K1

K2

K3

K4

Reloj

"1"

7. Cronograma:

Reloj

0 0 0 0 1 0 0 0 0 1

(MSB) Q1

0 1 1 0 1 1 0 1 1 0

Q2

0 0 1 0 1 1 0 0 1 0

Q3

0 0 0 1 0 1 0 0 0 1

(LSB) Q4 0 4 6 1 14 7 0 4 6 1

Cronograma reloj sncrono (Secuencia: 0, 4, 6, 1, 14, 7)

NOTA: Para construir el cronograma, como ahora cambian todos los biestables al mismo tiempo, tendremos que mirar la entrada de cada uno en el estado anterior.

Ejemplos de IC:

q q q q

74LS93: Asncrono binario 4 bits 74LS163: Sncrono binario de 4 bits 74LS160: Dcadas BCD sncrono 74LS190: Dcadas ascendente / descendente

32

También podría gustarte

- Manual Carrusel USUARIO TÉCNICODocumento81 páginasManual Carrusel USUARIO TÉCNICOmarcela aracenaAún no hay calificaciones

- 01 - Conexion Remota A EquiposDocumento19 páginas01 - Conexion Remota A EquiposEva SuárezAún no hay calificaciones

- Circuitos SecuencialesDocumento5 páginasCircuitos SecuencialesJuan BagurAún no hay calificaciones

- LM2907 CtoDocumento2 páginasLM2907 CtoNelson Camilo QuinayasAún no hay calificaciones

- Pae Monitoreo PiccoDocumento4 páginasPae Monitoreo PiccoLaura CuevasAún no hay calificaciones

- Documento Proyecto Final Prototipo MotocicletasDocumento28 páginasDocumento Proyecto Final Prototipo MotocicletasAndres Felipe Rubiano CetinaAún no hay calificaciones

- Capitulo 1 - ProblemasDocumento11 páginasCapitulo 1 - ProblemasHerber PintoAún no hay calificaciones

- DICOMDocumento17 páginasDICOMvaleria rodriguez0% (1)

- 4.capitulo 4 - Aplicacion Al Modelo de La DiabetesDocumento23 páginas4.capitulo 4 - Aplicacion Al Modelo de La Diabetesmdgrulo_978229267Aún no hay calificaciones

- Manual Del ClienteDocumento29 páginasManual Del ClientelexAún no hay calificaciones

- Presentación Tesis Italo BrionesDocumento38 páginasPresentación Tesis Italo BrionesItalo Nicolas Briones CanovasAún no hay calificaciones

- Manual Urgencia Web AdmisionDocumento16 páginasManual Urgencia Web AdmisionelizabethAún no hay calificaciones

- Introduccion Al Bus ISA PDFDocumento14 páginasIntroduccion Al Bus ISA PDFByron PanchiAún no hay calificaciones

- Clase 13 I2cDocumento80 páginasClase 13 I2cDavid Alejandro Espejo GarciaAún no hay calificaciones

- Filtros PasivosDocumento22 páginasFiltros PasivosJhoel René Mamani HuancaAún no hay calificaciones

- Currículum VitaeDocumento4 páginasCurrículum VitaeJosé Pablo Montesinos AbujatumAún no hay calificaciones

- Cobas h232 Brochure ESDocumento8 páginasCobas h232 Brochure ESjazzanovaqbAún no hay calificaciones

- Tema 05 - Sistemas RealimentadosDocumento12 páginasTema 05 - Sistemas RealimentadosSebastian Rodrigo Contreras GamboaAún no hay calificaciones

- Masterclass CtoDocumento27 páginasMasterclass CtoFacu GuerreroAún no hay calificaciones

- Documento Conductor V - 3 - Reporte Mensual GRD MinsalDocumento7 páginasDocumento Conductor V - 3 - Reporte Mensual GRD MinsalFernanda Blaskovic100% (1)

- Desarrollo de Un Sistema Mecatrónico Tipo Péndulo Invertido Sobre Base MóvilDocumento142 páginasDesarrollo de Un Sistema Mecatrónico Tipo Péndulo Invertido Sobre Base MóvilAlexander WalkerAún no hay calificaciones

- Coca ColaDocumento121 páginasCoca ColaLEONCICO180% (1)

- Tesis Dispensador de Medicamentos PDFDocumento83 páginasTesis Dispensador de Medicamentos PDFCalaka EncisoAún no hay calificaciones

- Indicador para Sustitución de Equipo MédicoDocumento4 páginasIndicador para Sustitución de Equipo MédicoJuan AlemánAún no hay calificaciones

- Rehabilitacion de Los Paraplejicos y Tetraplejicos AdultosDocumento16 páginasRehabilitacion de Los Paraplejicos y Tetraplejicos AdultosAlan RuizAún no hay calificaciones

- Regresion Lineal y LogisticaDocumento2 páginasRegresion Lineal y LogisticaAdrian PolitAún no hay calificaciones

- Instrumentacion BiomedicaDocumento9 páginasInstrumentacion BiomedicaAuro ÑacatoAún no hay calificaciones

- Como Restablecer El Funcionamiento de Un PLC Micrologix Cuando Está en FaultDocumento2 páginasComo Restablecer El Funcionamiento de Un PLC Micrologix Cuando Está en Faultrtapia_9100% (1)

- Análisis de Teoría de Colas e Invetarios Farmacias AhumadaDocumento14 páginasAnálisis de Teoría de Colas e Invetarios Farmacias AhumadaMax Power VillagranAún no hay calificaciones

- Capitulo 6 - BalotarioDocumento2 páginasCapitulo 6 - BalotarioRodrigo LaucataAún no hay calificaciones

- TPR Nº2a U2 ColaiacovoDocumento18 páginasTPR Nº2a U2 ColaiacovoGino FabrizioAún no hay calificaciones

- Comunica C I On SerialDocumento39 páginasComunica C I On SerialMabel Lorena Ochoa ContrerasAún no hay calificaciones

- Peter Senge J Calidad Total .Documento7 páginasPeter Senge J Calidad Total .Carlos AlasAún no hay calificaciones

- VG70 Brochure EspañolDocumento2 páginasVG70 Brochure EspañolCasique OldemarAún no hay calificaciones

- Informe RelojDigDocumento11 páginasInforme RelojDigGerson PinedaAún no hay calificaciones

- 01 - Función Coincidir & Función Índice - Parte 1Documento17 páginas01 - Función Coincidir & Función Índice - Parte 1James WilsonAún no hay calificaciones

- Caso Pollo Brujo 22 Leyes Inmutables de La MarcaDocumento1 páginaCaso Pollo Brujo 22 Leyes Inmutables de La MarcaEstuardo GarciaAún no hay calificaciones

- PRIMERA PARTE Prueba Final N°2 (Eunacom 2022) Forma 1ADocumento31 páginasPRIMERA PARTE Prueba Final N°2 (Eunacom 2022) Forma 1AMariaVivesAún no hay calificaciones

- Unidad II. Maquinas de Estados FinitosDocumento6 páginasUnidad II. Maquinas de Estados FinitosNNeft MrtzAún no hay calificaciones

- Epi InfoDocumento27 páginasEpi InfoAlex MoreanoAún no hay calificaciones

- Estructura y Tecnologia de ComputadoresDocumento392 páginasEstructura y Tecnologia de Computadoresemail4556Aún no hay calificaciones

- DICOM. Conceptos BásicosDocumento7 páginasDICOM. Conceptos BásicosAlejandro BertoletAún no hay calificaciones

- Telemedicina - FInalDocumento72 páginasTelemedicina - FInalRodrigo Muñoz GarcíaAún no hay calificaciones

- Invoperacionescaso de Aplicacion 2 WorkDocumento3 páginasInvoperacionescaso de Aplicacion 2 WorkMantilla BtoAún no hay calificaciones

- Angio TepDocumento62 páginasAngio Tepcarlosvlad100% (2)

- Segunda Tarea RedesDocumento16 páginasSegunda Tarea RedesJoyd Lasprilla CollazosAún no hay calificaciones

- Instrumentación INTELIGENTEDocumento30 páginasInstrumentación INTELIGENTEpablosky33Aún no hay calificaciones

- Variables y Magnitudes Físicas PDFDocumento36 páginasVariables y Magnitudes Físicas PDFDiego IvanAún no hay calificaciones

- Vias de Eliminación de Medios de ContrasteDocumento10 páginasVias de Eliminación de Medios de Contrastedaniel lopez lopezAún no hay calificaciones

- Manual Terminal CPX PLCDocumento146 páginasManual Terminal CPX PLCampowersidAún no hay calificaciones

- Introducción A Las Técnicas de NeuroimagenDocumento93 páginasIntroducción A Las Técnicas de NeuroimagenIsabel Torres MarinAún no hay calificaciones

- Teoria de Sistemas v2Documento36 páginasTeoria de Sistemas v2Diego Eduardo Cabrera Eyzaguirre100% (1)

- El Diseño de Tableros de Instrumentos Ejecutivos TomDocumento7 páginasEl Diseño de Tableros de Instrumentos Ejecutivos TomRoberto Gomez SanchezAún no hay calificaciones

- Registro Sanitario RX ListemDocumento1 páginaRegistro Sanitario RX ListemJONATHAN ALEXANDER RAMIREZ GARCIAAún no hay calificaciones

- Manual Movemaster EspañolDocumento33 páginasManual Movemaster EspañolRuben Amaro MichelAún no hay calificaciones

- Balon de Contrapulsación - Arrow AutoCAT2 WAVEDocumento2 páginasBalon de Contrapulsación - Arrow AutoCAT2 WAVEPaola LorenzattoAún no hay calificaciones

- Sistema de Gestion de Equipos Medicos en El Sector de Salud PublicaDocumento61 páginasSistema de Gestion de Equipos Medicos en El Sector de Salud PublicaalexAún no hay calificaciones

- Mitos Actividad FisicaDocumento10 páginasMitos Actividad FisicaCarmenp100% (1)

- ArritmiasDocumento31 páginasArritmiasVanessa ClaroAún no hay calificaciones

- Bie StablesDocumento18 páginasBie Stableslady67lauraAún no hay calificaciones

- Lectura y Tarea Capítulo 1Documento2 páginasLectura y Tarea Capítulo 1TharileonAún no hay calificaciones

- Chipoco, Carlos - El Sistema de Protección Universal de Los DDHHDocumento3 páginasChipoco, Carlos - El Sistema de Protección Universal de Los DDHHElMaic CardozoAún no hay calificaciones

- F4 Padron de Proveedores 1T-2021Documento214 páginasF4 Padron de Proveedores 1T-2021David C100% (1)

- V Delalande en Chile ProgramaDocumento5 páginasV Delalande en Chile Programaanna perez gomezAún no hay calificaciones

- Diapositiva Semana 7.1 - Funciones RacionalesDocumento39 páginasDiapositiva Semana 7.1 - Funciones RacionalesHarol RcAún no hay calificaciones

- Guia Matemática Semana 2Documento6 páginasGuia Matemática Semana 2Daniela AngamarcaAún no hay calificaciones

- ElectrostáticaDocumento4 páginasElectrostáticaBonitzuZTAún no hay calificaciones

- Cuál Debe Ser La Duración Del Período de Prueba Según El Término Del Contrato de TrabajoDocumento1 páginaCuál Debe Ser La Duración Del Período de Prueba Según El Término Del Contrato de TrabajoSotelo GuevaraAún no hay calificaciones

- Ordenanza 017-2023 El Peruano Modificacion Al Reglamento de Organizacion y Funciones (Rof)Documento3 páginasOrdenanza 017-2023 El Peruano Modificacion Al Reglamento de Organizacion y Funciones (Rof)kevin camavilcaAún no hay calificaciones

- Balance de Energia en Excel FinalDocumento32 páginasBalance de Energia en Excel FinalMayra SolangeAún no hay calificaciones

- Jovellanos Fiestas PudientesDocumento5 páginasJovellanos Fiestas PudientesPaula ArzaAún no hay calificaciones

- Erase Una Vez Una FabricaDocumento3 páginasErase Una Vez Una FabricaValentina RivillasAún no hay calificaciones

- Atlas de Seguridad y La Defensa de Mexico 2020 277 294Documento18 páginasAtlas de Seguridad y La Defensa de Mexico 2020 277 294raymondpkAún no hay calificaciones

- Seguridad de La NacionDocumento8 páginasSeguridad de La NacionkevinC995Aún no hay calificaciones

- ¿Qué Es Confianzac Su Definición y Significado (2023)Documento1 página¿Qué Es Confianzac Su Definición y Significado (2023)edAún no hay calificaciones

- Caso Mediacion Familiar SolucionadoDocumento4 páginasCaso Mediacion Familiar SolucionadoInma SAAún no hay calificaciones

- Libros 2Documento22 páginasLibros 2PA SPAún no hay calificaciones

- Villancico NegroDocumento1 páginaVillancico NegroIván Ramos GutiérrezAún no hay calificaciones

- 03 - Fuentes de EnergiaDocumento4 páginas03 - Fuentes de EnergiaRubén Méndez100% (1)

- Escuela de Educación Básica "Luz Del Mundo": Ventanas - Los Ríos - Ecuador Dirección: Esmeraldas y SucreDocumento13 páginasEscuela de Educación Básica "Luz Del Mundo": Ventanas - Los Ríos - Ecuador Dirección: Esmeraldas y SucreSarita CbAún no hay calificaciones

- SaltabilidadDocumento67 páginasSaltabilidadBarbara Andrade QuirozAún no hay calificaciones

- Apunte 2 RemuneracionesDocumento4 páginasApunte 2 RemuneracionesAndrea Vera PezoaAún no hay calificaciones

- 3° Sesión Día 3 Mat Apreciamos Nuestros Talentos Representando y Comparando NúmerosDocumento10 páginas3° Sesión Día 3 Mat Apreciamos Nuestros Talentos Representando y Comparando NúmerosDaniela Burgos nazarioAún no hay calificaciones

- Silabo Formulación de Trabajo para TitulaciónDocumento16 páginasSilabo Formulación de Trabajo para TitulaciónKleber MorilloAún no hay calificaciones

- HidrostaticaDocumento9 páginasHidrostaticaeusebioAún no hay calificaciones

- Hedonismo, Virtudes, UtilitarismoDocumento3 páginasHedonismo, Virtudes, UtilitarismoMontserrat MartínezAún no hay calificaciones

- 1517 7076 Rmat S1517 7076201700010298.pt - EsDocumento15 páginas1517 7076 Rmat S1517 7076201700010298.pt - EsAldair EP100% (1)

- OPS - 2020 Desinstitucionalización de La Atención Psiquiátrica en América Latina y El CaribeDocumento54 páginasOPS - 2020 Desinstitucionalización de La Atención Psiquiátrica en América Latina y El CaribeRofegobuAún no hay calificaciones

- Proyecto de SANEAMIENTO BÁSICODocumento41 páginasProyecto de SANEAMIENTO BÁSICODiana CampoAún no hay calificaciones

- El Procedimiento Ante Los JPL (Parte I)Documento46 páginasEl Procedimiento Ante Los JPL (Parte I)TarikAún no hay calificaciones