Documentos de Académico

Documentos de Profesional

Documentos de Cultura

lab7

Cargado por

LEONARDO ZENON VELASQUEZ MEJIADerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

lab7

Cargado por

LEONARDO ZENON VELASQUEZ MEJIACopyright:

Formatos disponibles

UNIVERSIDAD MAYOR DE SAN SIMON

FACULTAD DE CIENCIAS Y TECNOLOGIA

Practica N°7

CONTADOR UP/DOWN (VHDL)

Estudiante: Cardozo Cervantes Yerko

Docente: Jose Antonio Urrutia Medrano

Carrera: Ing. electrónica

Grupo: lunes 1115-1245

Fecha: 24/06/2022

LABORATORIO ELECTRONICA DIGITAL ll

Cochabamba-Bolivia

CONTADOR UP/DOWN (VHDL)

Objetivo

• Desarrollar un programa en Quartus II (VHDL) que realice la operación de un contador

ascendente y descendente de 4 bits.

Fundamento teórico

VHDL lenguaje de descripción en hardware

En la actualidad, el lenguaje de descripción en hardware más utilizado a nivel industrial es VHDL

(Hardware Description Language), que apareció en la década de los ochenta como un lenguaje

estándar, capaz de soportar el proceso de diseño de sistemas electrónicos complejos, con

propiedades para reducir el tiempo de diseño y los recursos tecnológicos requeridos.

Después de varias versiones revisadas por el gobierno de los Estados Unidos, industrias y

universidades, el IEEE (Instituto de Ingenieros Eléctricos y Electrónicos) publicó en diciembre de

1987 el estándar IEEEstd 1076-1987. Un año más tarde, surgió la necesidad de describir en VHDL

todos los ASIC creados por el Departamento de Defensa, por lo que en 1993 se adoptó el estándar

adicional de VHDL IEEE1164.

Hoy en día VHDL se considera como un estándar para la descripción, modelado y síntesis de

circuitos digitales y sistemas complejos. Este lenguaje presenta diversas características que lo

hacen uno de los HDL más utilizados en la actualidad.

Ventajas de circuitos integrados con VHDL

• Los circuitos integrados VHDL cuentan con una notación que permite su uso en cualquier

diseño electrónico.

• Disponibilidad pública. VHDL es un estándar no sometido a patente o marca registrada

alguna, por lo que cualquier empresa o institución puede utilizarla sin restricciones.

• Independencia tecnológica de diseño. VHDL se diseñó para soportar diversas tecnologías de

diseño (PLD, FPGA, ASIC, etc.) con distinta funcionalidad (circuitos combinacionales,

secuenciales, síncronos y asíncronos), a fin de satisfacer las distintas necesidades de diseño.

• Independencia de la tecnología y proceso de fabricación. VHDL se creó para que fuera

independiente de la tecnología y del proceso de fabricación del circuito o del sistema

electrónico.

• El lenguaje funciona en circuitos diseñados con tecnología MOS, bipolares, BICMOS, etc.

• VHDL permite el intercambio de información a lo largo de todas las etapas del proceso de

diseño, con lo cual favorece el trabajo en equipo.

• El uso de VHDL como lenguaje estándar permite reutilizar los códigos en diversos diseños,

sin importar que hayan sido generados para una tecnología (CMOS, bipolar, etc.) e

implementación (FPGA, ASIC, etc.) en particular.

Desventajas de circuitos integrados con VHDL

• En algunas ocasiones, el uso de una herramienta provista por alguna compañía en especial

tiene características adicionales al lenguaje, con lo que se pierde la libertad de diseño.

Como método alternativo, se pretende que entre diseñadores que utilizan distintas

herramientas exista una compatibilidad en sus diseños, sin que esto requiera un esfuerzo

importante en la traducción del código.

• Debido a que VHDL es un lenguaje diseñado por un comité, presenta una alta complejidad,

ya que se debe dar gusto a las diversas opiniones de los miembros de éste, por lo que

resulta un lenguaje difícil de aprender para un novato.

Simulación

• Contador UP/DOWN

Código

--lab7 -> contador up/down

------------------------------------------------------------

--librerias

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

------------------------------------------------------------

------------------------------------------------------------

--definimos la entidad

entity contador is

port( clock: in std_logic;

salida: out integer range 0 to 15;

pulsador: in std_logic

);

end contador;

------------------------------------------------------------

------------------------------------------------------------

--definimos la arquitectura

architecture up_down of contador is

signal puesto: integer range 0 to 7;

begin

contar: process (clock)

begin

if(clock' event and clock='0') then

if(pulsador='0') then

if(puesto=7) then

puesto <=0;

else

puesto <= puesto+1;

end if;

else

if(puesto=0) then

puesto <=7;

else

puesto <=puesto-1;

end if;

end if;

end if;

end process contar;

with puesto select

salida <= 5 when 0,

8 when 1,

3 when 2,

7 when 3,

9 when 4,

10 when 5,

2 when 6,

6 when others;

end up_down;

------------------------------------------------------------

Diagrama de bloques generado por Quartus2

Resultado

Conclusiones y recomendaciones

Con la utilización del programa quartu2 se pudo demostrar y comprobar el funcionamiento del

contador ascendente descendente mediante código VHDL así mismo obteniendo mayor

comprensión del programa

También podría gustarte

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeDe EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeAún no hay calificaciones

- Integración de Arduino para el control de luces mediante programaciónDocumento16 páginasIntegración de Arduino para el control de luces mediante programaciónEdwin Alberto Poveda RomeroAún no hay calificaciones

- Practica No.4 - Sandoval Frias DavidDocumento10 páginasPractica No.4 - Sandoval Frias DavidDavid Sandoval FriasAún no hay calificaciones

- Lab 9 Sisdig PDFDocumento9 páginasLab 9 Sisdig PDFHeberth PalaciosAún no hay calificaciones

- Tema 6 - Uso de PantallasDocumento8 páginasTema 6 - Uso de PantallasAntonioMonteolivaGarcíaAún no hay calificaciones

- Sistemas Digitales II Lab7Documento6 páginasSistemas Digitales II Lab7Natalia Berrocal GámezAún no hay calificaciones

- Cubo de LedsDocumento57 páginasCubo de Leds6EM Rios Ramirez Cristopher UrielAún no hay calificaciones

- Contador VHDL Ascendente y DescendenteDocumento7 páginasContador VHDL Ascendente y DescendenteDavid Sandoval FriasAún no hay calificaciones

- Timer, Practicas de MicroProgramables DRBDocumento7 páginasTimer, Practicas de MicroProgramables DRBDomingo ArroyoAún no hay calificaciones

- Taller 4-Manejo de Registro de DesplazamientoDocumento8 páginasTaller 4-Manejo de Registro de Desplazamientoferney alexander nava trujilloAún no hay calificaciones

- Lógica Secuencial con PLDDocumento17 páginasLógica Secuencial con PLDAlex RMAún no hay calificaciones

- Introducción a Verilog y sus estilos de descripciónDocumento42 páginasIntroducción a Verilog y sus estilos de descripciónAndrés M. FernándezAún no hay calificaciones

- Practica 05 - Introduccion A La Programacion de FPGAsDocumento6 páginasPractica 05 - Introduccion A La Programacion de FPGAsJoel AmezquitaAún no hay calificaciones

- Practica1 Arias CabreraDocumento6 páginasPractica1 Arias CabreraCarlos C. AriasAún no hay calificaciones

- Test BenchDocumento21 páginasTest BenchFernando MartinezAún no hay calificaciones

- Sesion 04 - 02 Practica Con Sensors y Actuadores Con Arduino Ultrasonido LCD ZumbadorDocumento34 páginasSesion 04 - 02 Practica Con Sensors y Actuadores Con Arduino Ultrasonido LCD ZumbadorRonalAlcantaraHuaripataAún no hay calificaciones

- IMPLEMENTACIÓN BÁSICA DE PICOBLAZE CON ENTRADA Y SALIDA PARALELAS DE 8 BITSDocumento14 páginasIMPLEMENTACIÓN BÁSICA DE PICOBLAZE CON ENTRADA Y SALIDA PARALELAS DE 8 BITSFabian BallenAún no hay calificaciones

- Practica 7Documento8 páginasPractica 7Jose Eduardo Garcia LopezAún no hay calificaciones

- Practica 2.3 PDFDocumento14 páginasPractica 2.3 PDFyoqsanAún no hay calificaciones

- Domain Specific Language (Lenguaje Especifico Del Dominio)Documento21 páginasDomain Specific Language (Lenguaje Especifico Del Dominio)fparraleAún no hay calificaciones

- Informe Labo 7Documento11 páginasInforme Labo 7Fati EspindolaAún no hay calificaciones

- Arduino IDEDocumento11 páginasArduino IDEDiego AlejandroAún no hay calificaciones

- Guia # 1Documento31 páginasGuia # 1Rigoberto AmayaAún no hay calificaciones

- Iniciando Con Los Microcontroladores Texas IntrumentsDocumento44 páginasIniciando Con Los Microcontroladores Texas IntrumentsSimon SosaAún no hay calificaciones

- UntitledDocumento18 páginasUntitledFrank RinconAún no hay calificaciones

- Alter Informe Lote 11Documento4 páginasAlter Informe Lote 11Chistian SanchezAún no hay calificaciones

- Guia 1 para Sistemas Digitales de La UESDocumento20 páginasGuia 1 para Sistemas Digitales de La UESEduardo100% (1)

- Guia 1 SDI215Documento20 páginasGuia 1 SDI215joel.arnoldolopezAún no hay calificaciones

- EJER9ERDocumento20 páginasEJER9ERmanuAún no hay calificaciones

- Ejervhdl 3Documento6 páginasEjervhdl 3manuAún no hay calificaciones

- Informe Motor de Induccion Parte 1Documento19 páginasInforme Motor de Induccion Parte 1Cristian MolinaAún no hay calificaciones

- Clase - 6 - Código Secuencial en VHDLDocumento31 páginasClase - 6 - Código Secuencial en VHDLDeysi LeonelaAún no hay calificaciones

- Practica No.2 - VHDLDocumento5 páginasPractica No.2 - VHDLDavid Sandoval FriasAún no hay calificaciones

- Laboratorio de Electrónica IiDocumento15 páginasLaboratorio de Electrónica IiLeonardoAún no hay calificaciones

- Programación PLC TIA PORTALDocumento9 páginasProgramación PLC TIA PORTALdarkaAún no hay calificaciones

- Arduino Con C++Documento80 páginasArduino Con C++Rommel LoayzaAún no hay calificaciones

- Practica 1Documento6 páginasPractica 1JuanMIguelPaezAún no hay calificaciones

- BennyAlvaro L8 PDFDocumento15 páginasBennyAlvaro L8 PDFJefte Torres SilvaAún no hay calificaciones

- Informe de Laboratorio 1Documento6 páginasInforme de Laboratorio 1Andres SuarezAún no hay calificaciones

- Laboratorio 3: Sumador y compuertas lógicas en VHDL y QuartusDocumento5 páginasLaboratorio 3: Sumador y compuertas lógicas en VHDL y QuartusSebastián RodríguezAún no hay calificaciones

- Ejercicios de Arduino ResueltosDocumento31 páginasEjercicios de Arduino ResueltosAlberto Espinoza92% (12)

- Intro Mecatrónica LED Control PotDocumento11 páginasIntro Mecatrónica LED Control Potsoly santos100% (1)

- Informe Taller ArduinoDocumento6 páginasInforme Taller ArduinoJhojan QuevedoAún no hay calificaciones

- Programación en VHDLDocumento17 páginasProgramación en VHDLsinchyAún no hay calificaciones

- Programacion Gal Unidad3Documento14 páginasProgramacion Gal Unidad3Ruben Angel RoqueAún no hay calificaciones

- Letrero LCD con ArduinoDocumento21 páginasLetrero LCD con ArduinoRicardo RamirezAún no hay calificaciones

- AVANCE RELOJ DESPERTADOR MICROCONTROLADORDocumento4 páginasAVANCE RELOJ DESPERTADOR MICROCONTROLADOR4r73m154Aún no hay calificaciones

- Diseño de Sistemas Electrónicos Digitales Avanzados: Ángel GrediagaDocumento37 páginasDiseño de Sistemas Electrónicos Digitales Avanzados: Ángel GrediagaHi HiutoAún no hay calificaciones

- MemoriaDocumento30 páginasMemoriaIrene Merino FernandezAún no hay calificaciones

- Tutorial Verilog BloqueDocumento42 páginasTutorial Verilog BloqueterrysconAún no hay calificaciones

- Aprender Arduino, electrónica y programación con 100 ejercicios prácticosDe EverandAprender Arduino, electrónica y programación con 100 ejercicios prácticosCalificación: 4.5 de 5 estrellas4.5/5 (14)

- Programación con lenguajes de guión en páginas web. IFCD0110De EverandProgramación con lenguajes de guión en páginas web. IFCD0110Aún no hay calificaciones

- Prácticas de redes de datos e industrialesDe EverandPrácticas de redes de datos e industrialesCalificación: 4 de 5 estrellas4/5 (5)

- Arduino: aplicaciones en robótica, mecatrónica e ingenieríasDe EverandArduino: aplicaciones en robótica, mecatrónica e ingenieríasAún no hay calificaciones

- Compilador C CCS y Simulador Proteus para Microcontroladores PICDe EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICCalificación: 2.5 de 5 estrellas2.5/5 (5)

- Programación gráfica para ingenierosDe EverandProgramación gráfica para ingenierosCalificación: 4.5 de 5 estrellas4.5/5 (3)

- Ejercicios AlgoritmosDocumento3 páginasEjercicios AlgoritmosLEONARDO ZENON VELASQUEZ MEJIAAún no hay calificaciones

- Sol_SP_cir2Documento4 páginasSol_SP_cir2LEONARDO ZENON VELASQUEZ MEJIAAún no hay calificaciones

- Planta ExternaDocumento195 páginasPlanta ExternamarcosAún no hay calificaciones

- lab2Documento7 páginaslab2LEONARDO ZENON VELASQUEZ MEJIAAún no hay calificaciones

- Clase ExtraDocumento1 páginaClase ExtraLEONARDO ZENON VELASQUEZ MEJIAAún no hay calificaciones

- lab4Documento4 páginaslab4LEONARDO ZENON VELASQUEZ MEJIAAún no hay calificaciones

- Burbujas resistentes y experimentos ópticos sencillosDocumento5 páginasBurbujas resistentes y experimentos ópticos sencillosCristhian RamirezAún no hay calificaciones

- Dmpa 11 III Unidad 4to Grado 2021Documento14 páginasDmpa 11 III Unidad 4to Grado 2021Betina GuevaraAún no hay calificaciones

- DípticoDocumento3 páginasDípticoCarol Elena Laimes TrinidadAún no hay calificaciones

- Cebo y AnzueloDocumento7 páginasCebo y AnzueloNICOLAS ARTEAGA BUSTAMANTEAún no hay calificaciones

- Enzima Transglutaminasa Evaluación Del Efecto Enzimatico A Temperatura Ambiente y A 60°cDocumento9 páginasEnzima Transglutaminasa Evaluación Del Efecto Enzimatico A Temperatura Ambiente y A 60°cLesne Santiago Franco PerezAún no hay calificaciones

- Ficha Semana 3Documento2 páginasFicha Semana 3Richard SalasAún no hay calificaciones

- Qué es la asertividad: 10 ejemplos de respuestas asertivasDocumento4 páginasQué es la asertividad: 10 ejemplos de respuestas asertivaslarmmxAún no hay calificaciones

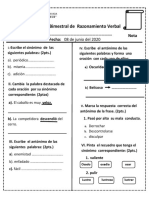

- Examenes Bimestrales Razonamiento Verbal 2do GradoDocumento2 páginasExamenes Bimestrales Razonamiento Verbal 2do GradoGustavo Carrera Becerra100% (1)

- Memoria DescriptivaDocumento11 páginasMemoria DescriptivaJosmell Kerlin Fabian GuerraAún no hay calificaciones

- SILABO Planificacion y Control de ObrasDocumento6 páginasSILABO Planificacion y Control de ObrasAlex pumaAún no hay calificaciones

- Conocimientos sensibles, conceptuales y holísticos en psicologíaDocumento3 páginasConocimientos sensibles, conceptuales y holísticos en psicologíaAspirantes Folio 205672606Aún no hay calificaciones

- Manual Del Comité Escolar de Administración ParticipativaDocumento19 páginasManual Del Comité Escolar de Administración ParticipativaMicho ChávezAún no hay calificaciones

- 2018 Tesis Sanchez Diaz Maria AlejandraDocumento154 páginas2018 Tesis Sanchez Diaz Maria AlejandrabrayanAún no hay calificaciones

- Equipo endodoncia clínica estomatológicaDocumento1 páginaEquipo endodoncia clínica estomatológicaLeslie GarciaAún no hay calificaciones

- 21 Proyecto Planta de Acido Sulfurico Mejillones PDFDocumento42 páginas21 Proyecto Planta de Acido Sulfurico Mejillones PDFEdward IllescasAún no hay calificaciones

- El Modelo: CapítuloDocumento25 páginasEl Modelo: CapítuloLIZETH PAOLA PAUCARA QUISPEAún no hay calificaciones

- Cáncer de Cavidad OralDocumento5 páginasCáncer de Cavidad OralDiana Valeria Corral GuardadoAún no hay calificaciones

- Paralelo Entre Windows 7 y Windows 8Documento6 páginasParalelo Entre Windows 7 y Windows 8leonardoAún no hay calificaciones

- PMBOK Ver 5 Procesos Vs Areas ConocimientoDocumento85 páginasPMBOK Ver 5 Procesos Vs Areas Conocimientojuanfdo1985Aún no hay calificaciones

- Ipc 368 Nov 012Documento108 páginasIpc 368 Nov 012DrTecno PcAún no hay calificaciones

- Perfil de Atención Al ClienteDocumento4 páginasPerfil de Atención Al ClienteAriel GranjaAún no hay calificaciones

- Desquinche de RocasDocumento38 páginasDesquinche de RocasEder Bustamante88% (8)

- Boletín Agroecología #23Documento13 páginasBoletín Agroecología #23Johana MonfardiniAún no hay calificaciones

- Guia 7 Hematologia AdyDocumento4 páginasGuia 7 Hematologia AdyElias David Suarez VasquezAún no hay calificaciones

- Ficha Tecnica Baldosa AMF Thermaclean SDocumento1 páginaFicha Tecnica Baldosa AMF Thermaclean SWill HMAún no hay calificaciones

- Vdocuments - MX - Juanita y El Conejo Perdido PDFDocumento6 páginasVdocuments - MX - Juanita y El Conejo Perdido PDFEMILY ZARETH CARDONA SABOGALAún no hay calificaciones

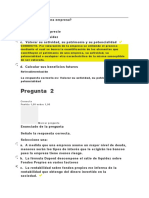

- Cómo valorar una empresa mediante el análisis de su actividad, patrimonio y potencialDocumento4 páginasCómo valorar una empresa mediante el análisis de su actividad, patrimonio y potencialramón monsalveAún no hay calificaciones

- Reprogramar La Mente y Alimentar El EspírituDocumento3 páginasReprogramar La Mente y Alimentar El EspírituOlga AmarantaAún no hay calificaciones

- Robo Agrav X Lesiones 166Documento33 páginasRobo Agrav X Lesiones 166A. DuAún no hay calificaciones

- Curriculum Vitae Dr. Cesar Morales2019Documento3 páginasCurriculum Vitae Dr. Cesar Morales2019Cesar Eduardo Morales0% (1)