MAPAS DE MEMORIAS - DISEÑO DE SISTEMAS MICROPROGRAMABLES

EJEMPLOS

1. Implementar con compuertas lógicas el siguiente mapa de memoria:

FFFF RAM de 4k*8

F000

07FF ROM de 2K*8

0000

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

FFFF 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

RAM X X X X X X X X X X X X

F000 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0

EFFF

8000

07FF 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1

ROM X X X X X X X X X X X

0000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

RAM ROM

4KX8 2KX8

CS CS

A15

A14

A13

A12 CSRAM

A15

A14

A13

A12

A11 CSROM

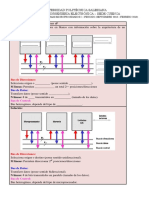

� 2. Implementar con decodificadores el siguiente mapa de memoria:

FFFF ROM de 8k*8

E000 CI de 4K*8

0FFF RAM de 4K*8

0000 CI de 2K*8

FUNCIÓN DIR. A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

8K ROM2 FFFF 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

4K X X X X X X X X X X X X

R F000 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0

O ROM1 EFFF 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1

M 4K X X X X X X X X X X X X

E000 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0

DFFF

1000

4K RAM2 0FFF 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1

2K X X X X X X X X X X X

R 0800 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0

A RAM1 07FF 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1

M 2K X X X X X X X X X X X

0000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

RAM 1 RAM 2 ROM 1 ROM 2

2K 2K 4K 4K

D CS CS CS CS

E

A11 CSRAM1

C 0

O

1 CSRAM2

E

0

1

D 2

E 3

C 4

A15 O

A14 5

D 6

A13 I

A12 7

F 8

I 9

C 10

A 11

D 12

O 13 CSROM1

R 14

15

CSROM2

� 3. Diseñar un sistema con 8 controladores y con direcciones en los rangos 1200-120F y 34F0-

34FF

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

FFFF 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

RAM X X X X X X X X X X X X

F000 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0

34FF 0 0 1 1 0 1 0 0 1 1 1 1 1 1 1 1

C7…C4 X X X X

34F0 0 0 1 1 0 1 0 0 1 1 1 1 0 0 0 0

120F 0 0 0 1 0 0 1 0 0 0 0 0 1 1 1 1

C3…C0 X X X X

1200 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0

07FF 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1

ROM X X X X X X X X X X X

0000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

C4 C5 C6 C7

A1 A0 CS A1 A0 CS A1 A0 CS A1 A0 CS

A1 A0 A1 A0 A1 A0 A1 A0

D 0

A2 E

C 1

A3 O

2

E 3

A=B

A COMPARADOR B

12 12

� 16 A15… A4

A15 34F (001101001111)

BUS

A0

� 4. Diseñar un sistema microprogramable con un microprocesador que puede direccionar 64

KB, cuyo vector de Reset se encuentra en la dirección 0000, con un sistema de memoria de:

16 KB * 8 de RAM ( con CI de 8 KB * 8 ) y

8 KB * 8 de memoria ROM ( con CI de 4 KB * 8).

También tiene 4controladores de e/s en los rangos de direcciones 8000 – 800F.

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

FFFF 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

RAM2 X X X X X X X X X X X X X

RAM E000 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0

16 K DFFF 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1

RAM1 X X X X X X X X X X X X X

C000 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0

BFFF

CONTR. 800F 1 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1

C3…C0 X X X X

E/S 8000 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

2000

1FFF 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1

ROM2 X X X X X X X X X X X X

ROM

1000 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0

8K 0FFF 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1

ROM1 X X X X X X X X X X X X

0000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

A15 A15

A14 CSRAM2 A14 CSROM2

A13 A13

A12

A15

A15

CSRAM1 A14

A14 CSROM1

A13

A13

A12

� RAM 1 RAM 2 ROM 1 ROM 2

4K 4K 8K 8K

CS CS CS CS

CSROM1

0

1

D 2 CSROM2

E 3

C 4

A15 O

A14 5

D 6

A13 I

A12 7

F 8

I 9

C 10

A 11

D CSRAM1

12

O 13

R 14

15

CSRAM2

��5. Implementar con decodificadores y con compuertas el siguiente mapa de memoria:

FFFF ROM de 8k*8

E000 CI de 8K*8

0FFF RAM de 4K*8

0000 CI de 4K*8

6. Diseñar un sistema microprogramable con un microprocesador que puede direccionar 64

KB, cuyo vector de Reset se encuentra en la dirección FF00, con un sistema de memoria de:

8 KB * 8 de RAM (con CI de 8 KB * 8) y

4 KB * 8 de memoria ROM (con CI de 4 KB * 8).

También tiene 4controladores de e/s en los rangos de direcciones A000 – A00F.