Documentos de Académico

Documentos de Profesional

Documentos de Cultura

2do Exámen SD-2022-1 +1

Cargado por

Marcos SuarezTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

2do Exámen SD-2022-1 +1

Cargado por

Marcos SuarezCopyright:

Formatos disponibles

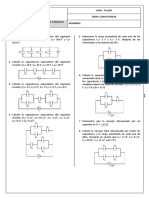

UNIDADES TECNOLOGICAS DE SANTANDER

FACULTAD DE CIENCIAS NATURALES E INGENIERIA

SEGUNDO EXAMEN PARCIAL ELECTRÓNICA DIGITAL I

PRUEBA ESCRITA (60 %)

Nombre: Código: Resultado:

Programa: Grupo: Fecha: Prof.: M.I. Nathaly Murcia S.

RESULTADOS DE APRENDIZAJE Ítem

Realiza simplificación de circuitos Lógicos por Mapas de Karnaugh y Quine McClusey 1

Diseña circuitos lógicos combinacionales 2

Conoce los sumadores (medio, completo, binario) y restadores. 3

Recuerde:

1. Lea detenidamente el contenido del parcial, cualquier inquietud se resolverá 3. Maneje el tiempo del cuestionario de manera adecuada: 1 hora 30 minutos.

solo en los primeros 10 minutos. 4. Sea claro y organizado en sus respuestas para mayor comprensión.

2. La interpretación forma parte de la evaluación, por tanto, NO SE RESPONDEN 5. Apague su teléfono celular o póngalo en modo vibrador para no interrumpir a sus

PREGUNTAS DE PROCEDIMIENTO. compañeros. No se permite el intercambio de información ni materiales durante el

examen.

1. (3 PUNTOS) El circuito de un sistema de alarma de una c) (0.7) Dibuje el circuito completo (todas las entradas y

vivienda consta de un sensor en la puerta (C) y dos sensores salidas) con compuertas lógicas de 2 entradas.

A y B en las ventanas. Los sensores entregan un 1 cuando

están abiertas las ventanas o puertas y un 0 en caso Puede manipular las expresiones simplificadas de cada

contrario. El sistema se activa con un interruptor P que ha salida para reducir el número de compuertas o

de estar activado (1) para que la alarma sonora (S) reutilizar alguna combinación que esté incluida varias

funcione. salidas. (calificación máxima si se implementa con 6

compuertas lógicas)

Cuando la alarma está conectada (P=1), las luces L1 y L2

estarán siempre apagadas (0) y la apertura de la puerta o 2. (2 PUNTOS) Diseñe un circuito combinacional con tres

de alguna de las ventanas ha de activar una alarma sonora entradas, x, y y z, y tres salidas, A, B y C. Cuando la entrada

(S). Cuando la alarma está apagada (P=0) se encenderá un binaria es 0, 1, 2 o 3, la salida binaria es uno más que la

LED (L1=1) informando que alguna de las ventanas está entrada. Si la entrada binaria es 4, 5, 6 o 7, la salida binaria

abierta; y otro LED (L2=1) si la puerta está abierta. es uno menos que la entrada.

a) (0.8) Escriba la tabla de verdad correspondiente al a) (0.7) Escriba la tabla de verdad correspondiente. Se

diseño solicitado. Se sugiere usar el siguiente orden: sugiere usar el siguiente orden:

Entradas Salidas Número Entradas Salidas Número

P A B C S L1 L2 x y z A B C

0 0 0 0 0 0 0

0 0 0 1 Ejemplo: 1 0 0 1 0 1 0 1+1= 2

0 0 1 0 0 1 0

0 0 1 1 0 1 1

0 1 0 0 1 0 0

0 1 0 1 1 0 1

0 1 1 0 1 1 0

0 1 1 1 1 1 1

1 0 0 0

1 0 0 1 a) (0.6) Debe hallar las expresiones más simplificadas

1 0 1 0 posibles usando mapas de Karnaugh. Debe usar

1 0 1 1 compuertas exclusivas XOR si es posible.

1 1 0 0

1 1 0 1 b) (0.6) Dibuje el circuito completo (todas las entradas y

1 1 1 0 salidas) con compuertas lógicas de 2 entradas.

1 1 1 1

(calificación máxima si se implementa con 7

Recuerde son tres salidas diferentes que actúan de compuertas lógicas de 2 entradas)

acuerdo al enunciado.

b) (1.5) Obtener la expresión más simplificada del sistema

(Salidas S, L1 y L2) a partir del método de mapas de

Karnaugh.

También podría gustarte

- 2do Exámen SD-2022-1 +1Documento1 página2do Exámen SD-2022-1 +1Marcos SuarezAún no hay calificaciones

- Tarea3 Jairo SanjuanDocumento5 páginasTarea3 Jairo SanjuansebastianAún no hay calificaciones

- Práctica 3 NUEVADocumento11 páginasPráctica 3 NUEVAAle Ran ArgüelloAún no hay calificaciones

- Cuestionario Previo 2Documento12 páginasCuestionario Previo 2ROBERTO GASPAR ESCOBEDO CONTRERASAún no hay calificaciones

- Reporte de Práctica 3 Castrejón Alfaro VíctorDocumento7 páginasReporte de Práctica 3 Castrejón Alfaro VíctorVíctor CastrejonAún no hay calificaciones

- Unidad I - Algebra de BooleDocumento15 páginasUnidad I - Algebra de BooleCarlos OrtegaAún no hay calificaciones

- Tarea de Sistemas DigitalesDocumento8 páginasTarea de Sistemas DigitalesFABIOLA BRIGITTE CUENCA ERREYESAún no hay calificaciones

- Lógica Combinacional y Álgebra BooleanaDocumento6 páginasLógica Combinacional y Álgebra BooleanaEduardo HidalgoAún no hay calificaciones

- ACTIVIDAD 2 Taller Sobre Los Sistemas NuméricosDocumento4 páginasACTIVIDAD 2 Taller Sobre Los Sistemas NuméricosAlexander PerezAún no hay calificaciones

- BOLETÍN 2. Puertas LógicasDocumento5 páginasBOLETÍN 2. Puertas LógicasyofegoAún no hay calificaciones

- Trabajo Práctico #6 FINALDocumento34 páginasTrabajo Práctico #6 FINALANTHONY VALENCIA ZUTAAún no hay calificaciones

- Informe de Laboratorio 4 Aplicacion de CompuertasDocumento8 páginasInforme de Laboratorio 4 Aplicacion de CompuertasMilagros Chavarria TorrezAún no hay calificaciones

- Informe Previo 3Documento10 páginasInforme Previo 3RENZO JOEL PUMACALLAO ROLDANAún no hay calificaciones

- Practica1 Diseño Digital ModernoDocumento10 páginasPractica1 Diseño Digital ModernoJuanVazquezAún no hay calificaciones

- Trabajo Práctico N°1 Circuitos DigitalesDocumento42 páginasTrabajo Práctico N°1 Circuitos DigitalesALEXANDER LENIN VILLANUEVA BARRETOAún no hay calificaciones

- Informe Ii Circuitos DigitalesDocumento10 páginasInforme Ii Circuitos DigitalesJuan David OrtizAún no hay calificaciones

- Cuestionario Previo 8Documento12 páginasCuestionario Previo 8ROBERTO GASPAR ESCOBEDO CONTRERASAún no hay calificaciones

- PROYECTO 3 ReconfigDocumento11 páginasPROYECTO 3 ReconfigAiraAún no hay calificaciones

- Previo 2Documento13 páginasPrevio 2Johan Romero LimaAún no hay calificaciones

- Ecl TP6 2019Documento2 páginasEcl TP6 2019Juan FigueroaAún no hay calificaciones

- Informe de Practica Del Ejemplo 1Documento4 páginasInforme de Practica Del Ejemplo 1santiago martinez rodriguez :DAún no hay calificaciones

- Sec. 03 2021-4 FED Examen ParcialDocumento7 páginasSec. 03 2021-4 FED Examen ParcialGian SusanaAún no hay calificaciones

- Lab 6 - Micro Nano Sistemas ElectrónicosDocumento25 páginasLab 6 - Micro Nano Sistemas ElectrónicosGabriel Hostiliano CoblentzAún no hay calificaciones

- Práctica #7 - Circuitos LógicosDocumento6 páginasPráctica #7 - Circuitos LógicosAlvaro CerveraAún no hay calificaciones

- 08 Logica Matematica Digital PDFDocumento20 páginas08 Logica Matematica Digital PDFFranciscoAún no hay calificaciones

- Tarea 1 Yael Montero Toma 2 ODCDocumento4 páginasTarea 1 Yael Montero Toma 2 ODCYael MonteroAún no hay calificaciones

- Práctica 5. Lógica Combinacional - FAMBDocumento14 páginasPráctica 5. Lógica Combinacional - FAMBKarla RMAún no hay calificaciones

- Informe 6 Vicente AlvarezDocumento17 páginasInforme 6 Vicente AlvarezVicente AlvarezAún no hay calificaciones

- Informe 2 (C.dig I)Documento22 páginasInforme 2 (C.dig I)kateryneAún no hay calificaciones

- PRACTICA Nº4 DigiDocumento10 páginasPRACTICA Nº4 DigiAntonio Arispe MamaniAún no hay calificaciones

- Algebra de Boole 2Documento80 páginasAlgebra de Boole 2Carlos Arturo Rosales OrdoñezAún no hay calificaciones

- Workshop 2001 M01Documento8 páginasWorkshop 2001 M01anderson penagosAún no hay calificaciones

- Act.7Compuertas L GicasDocumento6 páginasAct.7Compuertas L Gicasangel basilioAún no hay calificaciones

- Informe #2 Sistemas Digitales 1Documento5 páginasInforme #2 Sistemas Digitales 1Juan Sebastian Chicangana MontoyaAún no hay calificaciones

- Laboratorio 6 DigitalesDocumento17 páginasLaboratorio 6 DigitalesDavid Del ValleAún no hay calificaciones

- T 1 S 5 Jacquelin Neville GasDocumento6 páginasT 1 S 5 Jacquelin Neville GasJacqueline Villegas GonzalezAún no hay calificaciones

- Práctica No. 4 Mapas de KarnaughDocumento10 páginasPráctica No. 4 Mapas de KarnaughOscar MonroyAún no hay calificaciones

- Informe Previo 2 - Circuitos Digitales I FIEE-UNMSMDocumento7 páginasInforme Previo 2 - Circuitos Digitales I FIEE-UNMSMJames Lizonde PeredoAún no hay calificaciones

- Multiplex OresDocumento2 páginasMultiplex OresJuan Pablo Flores MenachoAún no hay calificaciones

- Sistemas de Lógica Secuencial y Comvinatoria - Actividad 8Documento18 páginasSistemas de Lógica Secuencial y Comvinatoria - Actividad 8Kazutonardo HanemiyaAún no hay calificaciones

- 2.-Diseño de Circuitos Combinacionales - 21 - 1Documento10 páginas2.-Diseño de Circuitos Combinacionales - 21 - 1YOT0YCHIDOAún no hay calificaciones

- Latorre Jhonny 2121 Lab. 5 EadDocumento29 páginasLatorre Jhonny 2121 Lab. 5 EadMNBVGCFRSTERBAún no hay calificaciones

- Reporte PracticaDocumento9 páginasReporte PracticaXavier Cruz HernándezAún no hay calificaciones

- Informe GuiaDocumento15 páginasInforme GuiaSantiago LaraAún no hay calificaciones

- Ejercicios LabDocumento5 páginasEjercicios LabVictor BadellAún no hay calificaciones

- 04 Lab04Documento8 páginas04 Lab04tareas tecnologiaAún no hay calificaciones

- Clic 02Documento9 páginasClic 02Jharol TordoyaAún no hay calificaciones

- Hernandez Perez Diego-Problemas AdicionalesDocumento4 páginasHernandez Perez Diego-Problemas AdicionalesDiego Fernando Hernández PérezAún no hay calificaciones

- Practica 3 Circuitos LogicosDocumento9 páginasPractica 3 Circuitos LogicosVelasco Álvarez José LuisAún no hay calificaciones

- Laboratorio Virtual 5 Compuertas LógicasDocumento4 páginasLaboratorio Virtual 5 Compuertas LógicasFabricio Jimenez ArtolaAún no hay calificaciones

- Informe Tecnicas DigitalesDocumento3 páginasInforme Tecnicas Digitalesjulian casallasAún no hay calificaciones

- PEC FDS Gabriel Díez TejedorDocumento5 páginasPEC FDS Gabriel Díez TejedorHarryYNGAún no hay calificaciones

- Practica ED5 - Reyes, Salinas, Jaramillo C., Jaramillo ADocumento6 páginasPractica ED5 - Reyes, Salinas, Jaramillo C., Jaramillo ARAFAEL REYESAún no hay calificaciones

- Informe de Laboratorio n.-6Documento3 páginasInforme de Laboratorio n.-6alexisAún no hay calificaciones

- Ejercicio Del Circuito LogicoDocumento2 páginasEjercicio Del Circuito LogicoPHES INVERSIONESAún no hay calificaciones

- Practica de CircuitosDocumento9 páginasPractica de CircuitosHanniaGarciaAún no hay calificaciones

- Curso básico de teoría de númerosDe EverandCurso básico de teoría de númerosCalificación: 5 de 5 estrellas5/5 (2)

- Taller TI - Ley de GaussDocumento3 páginasTaller TI - Ley de GaussMarcos SuarezAún no hay calificaciones

- Taller Mapas KanaughDocumento4 páginasTaller Mapas KanaughMarcos SuarezAún no hay calificaciones

- TallerPrimerCorte ED1 2022 1Documento3 páginasTallerPrimerCorte ED1 2022 1Boy NiggaAún no hay calificaciones

- Ejercicios para Puntos Positivos Electrónica IDocumento1 páginaEjercicios para Puntos Positivos Electrónica IMarcos SuarezAún no hay calificaciones

- 1er Exámen ED-Apellidos A-LDocumento1 página1er Exámen ED-Apellidos A-LMarcos SuarezAún no hay calificaciones

- Taller Clase - Ley de Gauss - Pag 1Documento1 páginaTaller Clase - Ley de Gauss - Pag 1Marcos SuarezAún no hay calificaciones

- Septima y Octava ClaseDocumento8 páginasSeptima y Octava ClaseMarcos SuarezAún no hay calificaciones

- Sexta ClaseDocumento12 páginasSexta ClaseMarcos SuarezAún no hay calificaciones

- Taller - CapacitanciaDocumento2 páginasTaller - CapacitanciaMarcos SuarezAún no hay calificaciones

- Taller Clase - Ley de GaussDocumento3 páginasTaller Clase - Ley de GaussMarcos SuarezAún no hay calificaciones

- Quiz - Ley de Gauss - SoluciónDocumento2 páginasQuiz - Ley de Gauss - SoluciónMarcos SuarezAún no hay calificaciones

- Recopilador de Estadísticas FlexsimDocumento81 páginasRecopilador de Estadísticas FlexsimYanelis ChiariAún no hay calificaciones

- Memoria de Calculo ComsaDocumento7 páginasMemoria de Calculo ComsaLuis GyAún no hay calificaciones

- Plantilla para La Presentación Del Articulo CientificoDocumento11 páginasPlantilla para La Presentación Del Articulo CientificoJairo MojicaAún no hay calificaciones

- Material de Factorización de PolinomiosDocumento9 páginasMaterial de Factorización de PolinomiosEnrique Montero100% (1)

- Formato C7Documento36 páginasFormato C7Cristian Del AguilaAún no hay calificaciones

- Escala para Evaluación de LibroDocumento1 páginaEscala para Evaluación de LibroGuadalupe HenriquezAún no hay calificaciones

- Qué Es Scribd y Cómo FuncionaDocumento1 páginaQué Es Scribd y Cómo FuncionalisandroAún no hay calificaciones

- Control Velocidad Motor DCDocumento20 páginasControl Velocidad Motor DCHg RosmeriAún no hay calificaciones

- AA2 Bases de Datos ALEJANDRO RIOSDocumento6 páginasAA2 Bases de Datos ALEJANDRO RIOSHaydem RiosAún no hay calificaciones

- Sensores de Fondo. Geolis 2Documento8 páginasSensores de Fondo. Geolis 2Susan Alexandra LealAún no hay calificaciones

- Formulari de Reclamació EsDocumento6 páginasFormulari de Reclamació Esjulio pedroAún no hay calificaciones

- Protocolo Analisis de Las Dinamicas de Los Tambios de La Tierra CAN PDFDocumento72 páginasProtocolo Analisis de Las Dinamicas de Los Tambios de La Tierra CAN PDFhsicllaAún no hay calificaciones

- Manual Media System Seat Leon 2017Documento108 páginasManual Media System Seat Leon 2017elsenderista.galicia100% (1)

- Dibujo de Serrano PDFDocumento398 páginasDibujo de Serrano PDFClau BM50% (2)

- Manual de Funciones y Competencias Laborales-Suboficial TICSDocumento2 páginasManual de Funciones y Competencias Laborales-Suboficial TICSRichard DelgadoAún no hay calificaciones

- Calculo de Numero de ChorrosDocumento5 páginasCalculo de Numero de ChorrosEduardo Arribasplata CernaAún no hay calificaciones

- Modulación Analogica de PulsosDocumento7 páginasModulación Analogica de PulsosFernando MartinezAún no hay calificaciones

- Unidades de Estudio - MonografiaDocumento46 páginasUnidades de Estudio - MonografiaIsabel Chiriboga SánchezAún no hay calificaciones

- SAI (Sistema de Alimentación Ininterrumpida) o También Llamado UPS (Uninterruptable Power Supply)Documento13 páginasSAI (Sistema de Alimentación Ininterrumpida) o También Llamado UPS (Uninterruptable Power Supply)ricardo campsAún no hay calificaciones

- Bitacora 8 OxfordDocumento1 páginaBitacora 8 Oxforddori gamer 007Aún no hay calificaciones

- Camus Albert - El MalentendidoDocumento76 páginasCamus Albert - El Malentendidoaxel machadoAún no hay calificaciones

- Gjiogm 9876 FJBDFBDocumento4 páginasGjiogm 9876 FJBDFBJorgeLuisGuevaraMartinezAún no hay calificaciones

- Aprueban Manual de Administración de Almacenes para El Sector Público NacionalDocumento18 páginasAprueban Manual de Administración de Almacenes para El Sector Público NacionalalexjhoelAún no hay calificaciones

- U1 A3 Presentacion SigsDocumento9 páginasU1 A3 Presentacion SigsTeresa RamirezAún no hay calificaciones

- Caso KodakDocumento14 páginasCaso KodakjimmyfisiAún no hay calificaciones

- Estereotipo SuposicionesDocumento2 páginasEstereotipo Suposicionesluis VillafañaAún no hay calificaciones

- Datos Tecnicos My08Documento9 páginasDatos Tecnicos My08Juan Manuel AcebedoAún no hay calificaciones

- MAPA MENTAL Administración de OperacionesDocumento1 páginaMAPA MENTAL Administración de OperacionesDash DashAún no hay calificaciones

- MuestreoDocumento20 páginasMuestreoJuanaAún no hay calificaciones

- Contactos Gays Masaje Tantrico en MadridDocumento4 páginasContactos Gays Masaje Tantrico en MadridEroticoAún no hay calificaciones