Documentos de Académico

Documentos de Profesional

Documentos de Cultura

TP 10 2020 TP Resuelto

Cargado por

Lucas MossatoTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

TP 10 2020 TP Resuelto

Cargado por

Lucas MossatoCopyright:

Formatos disponibles

lOMoARcPSD|9317128

TP - 10 - 2020 - Tp resuelto

Técnicas Digitales I (Universidad Tecnológica Nacional)

StuDocu is not sponsored or endorsed by any college or university

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

UNIVERSIDAD TECNOLOGICA NACIONAL

FACULTAD REGIONAL AVELLANEDA

DEPARTAMENTO DE ELECTRÓNICA

ASIGNATURA: Técnicas Digitales I

Curso: 2º R 15 Año: 2020

Docente: Ing.

Ayte.T.P.: Ing.

TRABAJO PRÁCTICO Nº 10

Contadores y Registros

GRUPO Nº 3

INTEGRANTES

Responsable del Informe:

1ª Entrega 1ª Devoluc 2ª Entrega 2ª Devoluc 3ª Entrega 3ª Devoluc

Fecha Aprobación_______ Firma

1) Se desea diseñar un contador BCD Exc 3 sincrónico de un digito.

a) Efectuar el diseño utilizando Flip-Flop T.

Diagrama de Estados y Transiciones

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

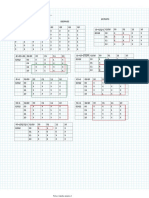

Tabla de Verdad

D C B A 𝐷∗ 𝐶∗ 𝐵∗ 𝐴∗ Z 𝑇𝐷 𝑇𝐶 𝑇𝐵 𝑇𝐴

0 0 0 0 0 X X X X X X X X X

1 0 0 0 1 X X X X X X X X X Tabla de excitación F-F T

2 0 0 1 0 X X X X X X X X X

Q 𝑄∗ T

3 0 0 1 1 0 1 0 0 0 0 1 1 1

0 0 0

4 0 1 0 0 0 1 0 1 0 0 0 0 1

0 1 1

5 0 1 0 1 0 1 1 0 0 0 0 1 1

1 0 1

6 0 1 1 0 0 1 1 1 0 0 0 0 1

1 1 0

7 0 1 1 1 1 0 0 0 0 1 1 1 1

8 1 0 0 0 1 0 0 1 0 0 0 0 1 𝑄𝑇∗ = 𝑇 ⊕ 𝑄

9 1 0 0 1 1 0 1 0 0 0 0 1 1

10 1 0 1 0 1 0 1 1 0 0 0 0 1

11 1 0 1 1 1 1 0 0 0 0 1 1 1

12 1 1 0 0 0 0 1 1 1 1 1 1 1

13 1 1 0 1 X X X X X X X X X

14 1 1 1 0 X X X X X X X X X

15 1 1 1 1 X X X X X X X X X

TD TC TB

BA 00 01 11 10 BA 00 01 11 10 BA 00 01 11 10

DC DC DC

00 X X 0 X 00 X X 1 X 00 X X 1 X

01 0 0 1 0 01 0 0 1 0 01 0 1 1 0

11 1 X X X 11 1 X X X 11 1 X X X

10 0 0 0 0 10 0 0 1 0 10 0 1 1 0

Ecuaciones

TA = 1

TB = D. C + A

TC = D. C + B. A

TD = D. C + C. B. A

̅. A

Z = D. C. B ̅

Circuito

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 1

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

b) Completar el diseño agregándole las señales de habilitación ET y EP, y la salida de cuenta

terminal TC.

- ET = 0 (se detiene cuenta)

- ET = 1 (habilita cuenta)

- EP = 0 (deshabilitado paralelo)

- EP = 1 (habilitado paralelo)

ET y EP se usa para expansión.

c) Modificar el diseño del punto b), agregándole para emplear Flip-Flop tipo D.

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 2

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

d) Completar el diseño del punto C, agregándole los elementos circuitales necesarios para dotarlo

de carga paralela sincrónica y Reset sincrónico.

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 3

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

SR = 0 resetea sincrónicamente

PE = 1 Carga paralela sincrónica

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 4

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

2) Diseñar un contador binario sincrónico módulo 1193 a partir de los contadores integrados 74HC163.

Necesito 3 contadores 74HC163. El contador va a contar de 0 a 1192 estados.

𝑀𝑂𝐷𝑇𝑜𝑡 = 𝑀𝑜𝑑𝐴 . 𝑀𝑜𝑑𝐵 . 𝑀𝑜𝑑𝐶

𝑀𝑂𝐷𝑇𝑜𝑑 = 16.16.16 = 4096

La entrada ̅̅̅̅̅̅

𝐶𝐿𝑅 (activa baja) Resetea Sincronicamente

en la version 162-163.

ENT (enable T) = Habilitacion para el conteo.

ENP (enable P) = Habilitacion de conteo paralelo.

̅̅̅̅̅̅) = Carga paralelo sincr. (activa baja)

̅̅̅̅̅̅̅̅̅̅ (𝑙𝑜𝑎𝑑

𝐶𝑎𝑟𝑔𝑎𝑟

D,C,B,A (Data in) = Entrada de datos sincr.

QD,QC,QB,QA (Outputs) = Salida de estados del contador.

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 5

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

1192 = 0100 1010 1000

3) Se desea simular la operación de un dado girando. Con este fin, se pide:

a) Diseñar un contador binario módulo 6 que cuente del 1 al 6 a partir de un contador binario

74HC163 aprovechando sus entradas de carga paralelo sincrónicas.

T.V

Estados C B A a b c d e f g

0 0 0 0 X X X X X X X

1 0 0 1 1 1 1 1 1 1 0

2 0 1 0 1 1 0 0 1 1 1

3 0 1 1 1 1 0 0 1 1 0

4 1 0 0 0 1 0 0 1 0 1

5 1 0 1 0 1 0 0 1 0 0

6 1 1 0 0 0 0 0 0 0 1

7 1 1 1 X X X X X X X

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 6

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

Reordeno la T.V

Estados C B A a b c d e f g Número del dado

0 0 0 0 1 1 1 1 1 1 0 1

1 0 0 1 1 1 0 0 1 1 1 2

2 0 1 0 1 1 0 0 1 1 0 3

3 0 1 1 0 1 0 0 1 0 1 4

4 1 0 0 0 1 0 0 1 0 0 5

5 1 0 1 0 0 0 0 0 0 1 6

6 1 1 0 X X X X X X X -

7 1 1 1 X X X X X X X -

Como son Leds se enciende con “0”.

Mapa de Karnaught

a b c

BA 00 01 11 10 BA 00 01 11 10 BA 00 01 11 10

C C C

0 1 1 0 1 0 1 1 1 1 0 1 0 0 0

1 0 0 X X 1 1 0 X X 1 0 0 X X

d e f

BA 00 01 11 10 BA 00 01 11 10 BA 00 01 11 10

C C C

0 1 0 0 0 0 1 1 1 1 0 1 1 0 1

1 0 0 X X 1 1 0 X X 1 0 0 X X

g

BA 00 01 11 10

C

0 0 1 1 0

1 0 1 X X

𝑎 = 𝐶̅ . 𝐵̅ + 𝐶̅ . 𝐴̅

𝑏 = 𝐶̅ + 𝐴̅ 𝑎=𝑓

𝑐 = 𝐶̅ . 𝐵̅. 𝐴̅ 𝑏=𝑒

𝑑 = 𝐶̅ . 𝐵̅ . 𝐴̅ 𝑐=𝑑

𝑒 = 𝐶̅ + 𝐵̅

𝑓 = 𝐶̅ . 𝐵̅ + 𝐶̅ . 𝐴̅

𝑔=𝐴

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 7

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

Circuito

El “1”

El “6”

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 8

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

b) Completar el diseño agregando lo necesario para que mientras se esté presionando manualmente

un pulsador, dicho contador este contando pulsos entregados por un astable de 100KHz de frecuencia

(que no se pise diseñar) de manera que al liberar el pulsador el contador exhiba un número del 1 al 6 que

será prácticamente al azar.

Modo astable 555:

𝑡

𝐶𝑇 = 𝑇2 ∗ 100 Ciclo de trabajo

CT aprox al 50 % (en alto y bajo) 𝑅2 ≥ 𝑅1

Lo que recomienda el fabricante:

𝑅1 ≥ 1𝐾𝑜ℎ𝑚

𝑅1 + 𝑅2 ≥ 6,6 𝑀𝑜ℎ𝑚

𝐶 ≥ 500 𝑝 𝐹

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 9

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

4) Un fabricante desea producir comercialmente un registro de desplazamiento de 4 bits con cuatro modos de

operación sincrónicos: desplazar a derecha, desplazar a izquierda, retener y cargar en paralelo. Tendrá además

salida paralelo y entradas serie para desplazamiento a derecha e izquierda. Se pide:

a) Proponer un circuito para ello.

Circuito:

MODOS 00 : retener

(M1 M0) 01 : desplazar a derecha

10 : desplazar a izquierda

11 : Carga paralela

Registro PIPO

Registro SISO

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 10

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

Registro SISO

Retener

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 11

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

b) Comparar el circuito propuesto con el circuito interno de 74LS194.

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 12

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

Circuito interno

Comparación

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 13

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

4 bits, 4 F-F D, sincrónico, 2 entradas de modo (S1,S2), desplazar de izquierda a derecha o de derecha a izquierda

̅̅̅̅̅ (entrada de fuerza), no depende de la señal de CLK, L.C(compuertas),

(SR - SL), 4 entradas paralelo y 4 salidas, 𝑀𝑅

y salidas con buffer.

c) Indicar como pueden conectarse tres de estos registros para formar un registro similar pero de 12 bits.

MODOS 00 : retener

(M1 M0) 01 : desplazar a derecha

10 : desplazar a izquierda

11 : Carga paralela

5) Se desea diseñar un circuito secuencial que genere en su unica salida una repeticion de la siguiente secuencia de

12 bits: 000110111001. El diseño debe asegurar que, si al encender el circuito este se encuentra en algun estado

fuera de secuencia, ingrese a la misma en la menor cantidad de pulsos de reloj posible. Se pide realizar el diseño de

dos formas distintas:

a) Usando un contador sincronico binario de modulo 16 con reset sincronico.

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 14

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 15

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

b) Usando un registro de desplazamiento de 4 bits con salida paralelo empleando el esquema de la figura

siguiente.

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 16

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

Secuencia

000110111001 Estado inicial, se da por única vez Adelantamos la secuencia 3 pulsos

T.V

REG 4 bits

Orden Q3 Q2 Q1 Q0 SI Binario

0 0 0 0 0 1 0

1 0 0 0 1 1 1

2 0 0 1 1 0 3

3 0 1 1 0 1 6

4 1 1 0 1 1 13

5 1 0 1 1 1 11

6 0 1 1 1 0 7

7 1 1 1 0 0 14

8 1 1 0 0 1 12

9 1 0 0 1 0 9

10 0 0 1 0 0 2

11 0 1 0 0 0 4

0 1 0 0 0 1 8

1 0 0 0 1 1 1

2 0 0 1 1 0 3

3 0 1 1 0 1 6

4 1 1 0 1 1 13

5 1 0 1 1 1 11

6 0 1 1 1 0 7

7 1 1 1 0 0 14

8 1 1 0 0 1 12

9 1 0 0 1 0 9

10 0 0 1 0 0 2

11 0 1 0 0 0 4

Reordeno la T.V

Q3 Q2 Q1 Q0 SI

0 0 0 0 1

0 0 0 1 1

0 0 1 0 0

0 0 1 1 0

0 1 0 0 0

0 1 0 1 1

0 1 1 0 1

0 1 1 1 0

1 0 0 0 1

1 0 0 1 0

1 0 1 0 0

1 0 1 1 1

1 1 0 0 1 Le agrego “1” o un “0” porque la palabra se desplaza hacia la izquierda

1 1 0 1 1 (los 3 bits – Q2 Q1 Q0 -) y el bit siguiente que entraría está dentro de la

1 1 1 0 0 secuencia, y con eso nos ahorramos un pulso de CLK en incorporarse a

1 1 1 1 0 la secuencia.

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 17

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

Mapa de Karnaught

Q1 Q0 00 01 11 10

Q3 Q2

00 1 1 0 0

01 0 1 0 1

11 1 1 0 0

10 1 0 1 0

SI = ̅̅̅̅

Q3. ̅̅̅̅

Q2. ̅̅̅̅

Q1 + Q3. ̅̅̅̅

Q1. ̅̅̅̅

Q0 + Q2. ̅̅̅̅

Q1. Q0 + ̅̅̅̅

Q3. Q2. Q1. ̅̅̅̅

Q0 + Q3. ̅̅̅̅

Q2. Q1. Q0

Circuito:

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 18

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

6) Usando como base un registro de desplazamiento, se pide:

a) Diseñar un circuito que reciba en su entrada X y en forma sincrónica con el reloj, una serie de

bits, y que entregue en su salida Z un 1 si el bit que ingresa en ese momento es un 0 precedido por tres 1

consecutivos.

Circuito:

b) Rediseñar para el caso que la salida valga 1 cuando en el anterior periodo del reloj la entrada

fue un 0, y fue precedida por tres 1 consecutivos.

Circuito:

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 19

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

7) Indicar si los contadores Johnson de modulo par:

a) Son contadores asincrónicos o sincrónicos.

b) Cuentan en un condigo cíclico.

c) Repetir ambos pasos para el caso de modulo impar.

Los contadores de modulo par son contadores sincrónicos, cuentan en un condigo cíclico.

Los contadores de modulo impar son contadores sincrónicos, no cuentan en un código cíclico.

8) Diseñar un circuito que cada vez que se presione manualmente un pulsador, genere una ráfaga de 10

pulsos a la salida con una frecuencia de 1 KHz. Suponer que no se pulsara nuevamente hasta que finalice

la ráfaga de pulsos producida por el disparo anterior.

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 20

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

9)a) Implementar un contador Johnson sincrónico módulo 10, para ello dispone de un solo contador

MC14516 y la lógica adicional necesaria (preferentemente MSI). El contador sincrónico es manejado por

una señal de reloj (𝑇𝐶𝐿𝐾 ) de 10 KHz. Tener en cuenta que el ciclo de cuenta se repite indefinidamente. EL

MC14516 es un contador módulo 16 ascendente- descendente, cuya tabla de verdad y esquema se da

más abajo.

Tabla de verdad:

𝑄3 𝑄2 𝑄1 𝑄0 𝐴4 𝐴3 𝐴2 𝐴1 𝐴0

0 0 0 0 0 0 0 0 0 0

1 0 0 0 1 0 0 0 0 1

2 0 0 1 0 0 0 0 1 1

3 0 0 1 1 0 0 1 1 1

4 0 1 0 0 0 1 1 1 1

5 0 1 0 1 1 1 1 1 1

6 0 1 1 0 1 1 1 1 0

7 0 1 1 1 1 1 1 0 0

8 1 0 0 0 1 1 0 0 0

9 1 0 0 1 1 0 0 0 0

10 1 0 1 0 X X X X X

11 1 0 1 1 X X X X X

12 1 1 0 0 X X X X X

13 1 1 0 1 X X X X X

14 1 1 1 0 X X X X X

15 1 1 1 1 X X X X X

Circuito:

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 21

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

Hoja de Datos: “Uso el 74HC190 – No está el MC14516 en Proteus”

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 22

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

b) Indicar cada cuanto tiempo cambia de estado el contador.

1 1

𝑇= = = 0,1 𝑚𝑠𝑒𝑔

𝐹 10𝐾𝐻𝑧

𝑇 0,1 𝑚𝑠𝑒𝑔

𝑇𝑐𝑎𝑑𝑎 𝑒𝑠𝑡𝑎𝑑𝑜 = = = 0,01 𝑚𝑠𝑒𝑔

10 10

c) Indicar cuál es la duración de un ciclo de cuenta completo.

1 1

𝑇= = = 0,1 𝑚𝑠𝑒𝑔

𝐹 10𝐾𝐻𝑧

𝐶𝑖𝑐𝑙𝑜 = 10 ∗ 𝑇 = 10 ∗ 0,1 𝑚𝑠𝑒𝑔 = 1 𝑚𝑠𝑒𝑔

Señales que no figuran en la TV:

Reset: Reset asincrónico (pata 9)

PE (Preset enable): Carga Paralelo

PO,P1,P2,P3: Dato a Cargar

Carry Out (N): Salida de cuenta terminal (TC)

Carry In (N): Ver Tabla

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 23

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

10) a) Diseñar el circuito de generador de caracteres binarios paralelos en hexadecimal. Los caracteres

hexadecimales que deben entregar el circuito a diseñar son F 0 A 3 C 6 y se repiten indefinidamente cada

24 ms. Tenga en cuenta, para el diseño, que cada uno de los caracteres sale en paralelo del circuito.

F0A3C6 tarda en salir 24 mseg.

Cada carácter Hexadecimal (son de 4 bits), son 6 caracteres entonces serán 6 estados 1 por cada

carácter. El módulo de mi contador secuencia sincrónico (CSS) será módulo 6.

Usamos el 74HC160 (CSS) es módulo 10, MR asincrónico y un reloj (CLK) activa alta.

Usamos el comparador 74LS85.

La lógica combinacional la implementamos de dos formas con compuertas básicas y con una PAL

4H4 C.

Diagrama de estados y transiciones

Circuito

Con el comparador de 4 bits llevamos al contador 74HC160 módulo 10 a un módulo 6, donde el

contador va a contar del estado 000 a 101.

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 24

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

Tabla de verdad (para la L.C)

C B A 𝐴3 𝐴2 𝐴1 𝐴0 (Out)Hexadecimal

0 0 0 1 1 1 1 F

1 0 1 0 0 0 0 0

0 1 0 1 0 1 0 A

1 1 1 0 0 1 1 3

0 0 0 1 1 0 0 C

1 0 1 0 1 1 0 6

0 1 0 X X X X -

1 1 1 X X X X -

Mapa de Karnaught

𝐴2 𝐴1 𝐴0

BA 00 01 11 10 BA 00 01 11 10 BA 00 01 11 10

C C C

0 1 0 0 0 0 1 0 1 1 0 1 0 1 0

1 1 1 X X 1 0 1 X X 1 0 0 X X

𝐴3 =A̅

𝐴2 = C+B ̅. A

̅

𝐴1 ̅. A

= C ̅ + C. A + B

𝐴0 ̅ . B̅ . A

= C ̅ + B. A

Opción 1 (con L.C)

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 25

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

Opción 2 (PAL 4H4C)

b) Indicar cuál es la frecuencia del reloj.

𝑇𝑜𝑢𝑡 = 24 𝑚𝑠 (para los 6 caracteres)

𝑇 24 𝑚𝑠

1𝑐𝑎𝑟𝑎𝑐𝑡𝑒𝑟 = = = 4 𝑚𝑠

6 6

1 1

𝐹= = = 250 𝐻𝑧

𝑇1 𝑐𝑐𝑎𝑟𝑎𝑐𝑡𝑒𝑟 4 𝑚𝑠

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 26

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

11) Diseñar un con contador binario ascendente, sincrónico módulo 100, con salida de cuenta terminal e

indicador de números impares, el mismo debe funcionar en un circuito de ABS en un automóvil. Para

este fin dispone de varios contadores sincrónicos módulo 8 con entrada de ̅̅̅̅̅ 𝑀𝑅 (asincrónica), PE (carga

paralelo sincrónica) y entrada de datos (𝐷0−2 ) y se debe agregar la lógica adicional necesario.

Cuenta de 0 a 99 – 0000 0000 a 0110 0011

Circuito:

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 27

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 28

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

lOMoARcPSD|9317128

Trabajo Practico Nº10 Comisión:

Contadores y Registros Grupo Nº

UNIVERSIDAD TECNOLOGICA NACIONAL Página | 29

Facultad Regional Avellaneda

Downloaded by Ailin Agustina Vega (ailinagustinav@gmail.com)

También podría gustarte

- Práctica de Laboratorio 1Documento7 páginasPráctica de Laboratorio 1Jhosep JcbAún no hay calificaciones

- Práctica #6Documento13 páginasPráctica #6Eliecer AyalaAún no hay calificaciones

- Circuitos Aritmeticos y Logicos para El Manejo de Datos Utilizando Compuertas Open Colector y TriDocumento16 páginasCircuitos Aritmeticos y Logicos para El Manejo de Datos Utilizando Compuertas Open Colector y Tricarlos de la cruzAún no hay calificaciones

- Contador BCDDocumento6 páginasContador BCDFernando PMAún no hay calificaciones

- Practica 5Documento8 páginasPractica 5Jhonatan Rios LedezmaAún no hay calificaciones

- Actividad 3 PDFDocumento9 páginasActividad 3 PDFjorgeAún no hay calificaciones

- Maquinas de Estado ClaseDocumento9 páginasMaquinas de Estado ClaseLimberth LcvAún no hay calificaciones

- DisplayDocumento16 páginasDisplayGianpierre RetoAún no hay calificaciones

- Ejercicio 4 Contadores Relacion ProblemasDocumento2 páginasEjercicio 4 Contadores Relacion Problemasabbadiassaad304Aún no hay calificaciones

- Parcial Sis Digi Kevin LopezDocumento6 páginasParcial Sis Digi Kevin LopezKevin LópezAún no hay calificaciones

- Reloj Con Flip-Flop JKDocumento6 páginasReloj Con Flip-Flop JKjessicajulissaAún no hay calificaciones

- Tarea 4-VN21007 SDUDocumento8 páginasTarea 4-VN21007 SDUrikelmy aldubiAún no hay calificaciones

- Laboratorio 2 de Sistemas Digitales 1 UNIDocumento5 páginasLaboratorio 2 de Sistemas Digitales 1 UNIDaniel Zavala100% (1)

- Diseño de circuito de memoria finita para controlar motor paso a pasoDocumento8 páginasDiseño de circuito de memoria finita para controlar motor paso a pasojuan jose peñaloza cabelloAún no hay calificaciones

- Practica 5 Diseño DiseñoDocumento4 páginasPractica 5 Diseño DiseñoAnonymous xQzIwQDpcYAún no hay calificaciones

- Tarea 3 - Ejercicio 2Documento9 páginasTarea 3 - Ejercicio 2George MoreloAún no hay calificaciones

- Problemas Con Mapas de Karnaugh Condiciones IndiferentesDocumento28 páginasProblemas Con Mapas de Karnaugh Condiciones Indiferentesjayrosuarez2004Aún no hay calificaciones

- Informe Final 9Documento24 páginasInforme Final 9Alvaro SegoviaAún no hay calificaciones

- Fco Primera Prueba 29 11 2010Documento8 páginasFco Primera Prueba 29 11 2010Adri SsAún no hay calificaciones

- Informe6-C DigitalesDocumento14 páginasInforme6-C DigitalesFrank PerezAún no hay calificaciones

- Solución Puntos 3 y 4 Tercer Parcial VirtualDocumento6 páginasSolución Puntos 3 y 4 Tercer Parcial VirtualGIANINA GARRIDO SILVAAún no hay calificaciones

- Lab Vega Diego 9952Documento12 páginasLab Vega Diego 9952Diego Sebastian Vega CastilloAún no hay calificaciones

- Problemas 2Documento6 páginasProblemas 2Angel VargasAún no hay calificaciones

- Circuitos digitales practica 3Documento6 páginasCircuitos digitales practica 3Carlos SynisterAún no hay calificaciones

- Ejercicios 2da FaseDocumento16 páginasEjercicios 2da FaseRenato Beltran CaceresAún no hay calificaciones

- Álgebra de Boole y decodificador BCD-7 segmentosDocumento18 páginasÁlgebra de Boole y decodificador BCD-7 segmentosjheimy13Aún no hay calificaciones

- Practica 7 - ComparadorDocumento7 páginasPractica 7 - ComparadorAlma PartidaAún no hay calificaciones

- Taller de simplificación de expresiones lógicas y diseño de circuitos digitalesDocumento7 páginasTaller de simplificación de expresiones lógicas y diseño de circuitos digitalespuntoexactoAún no hay calificaciones

- Circuitos secuenciales digitalesDocumento4 páginasCircuitos secuenciales digitalesPiero Alexander Diaz Yecler100% (1)

- Clase 14 Ejemplos de Diseño de Circuitos SecuencialesDocumento8 páginasClase 14 Ejemplos de Diseño de Circuitos SecuencialesPeoto VallelinAún no hay calificaciones

- Electrónica Digital: Display de 7 Segmentos Con Compuertas LógicasDocumento15 páginasElectrónica Digital: Display de 7 Segmentos Con Compuertas Lógicassantiago pablo alberto100% (2)

- Diseño de circuito divisor expandible binarioDocumento8 páginasDiseño de circuito divisor expandible binarioMario CcoyoriAún no hay calificaciones

- Sistema de empastado de libros con flip flops JKDocumento6 páginasSistema de empastado de libros con flip flops JKJuan Hinostroza PalianAún no hay calificaciones

- Hoja de Datos 8Documento3 páginasHoja de Datos 8Diego ChitupantaAún no hay calificaciones

- Manejo Del Wincupl para Diseñar Circuitos Combinacionales Con ArreglosDocumento10 páginasManejo Del Wincupl para Diseñar Circuitos Combinacionales Con ArreglosJAIME FERNANDO TOAQUIZA BALDERRAMOAún no hay calificaciones

- Examen3 SolDocumento5 páginasExamen3 Soljose tellezAún no hay calificaciones

- Flip Flop ContadorDocumento4 páginasFlip Flop ContadorBrayan EcheniqueAún no hay calificaciones

- Practica 3 CorregidaDocumento8 páginasPractica 3 CorregidaKARLA IVETTE ORTIZ PUENTESAún no hay calificaciones

- Sumador de Dos Números Binarios de 2 BitsDocumento6 páginasSumador de Dos Números Binarios de 2 BitsAfir MinayaAún no hay calificaciones

- Sumador de Dos Números Binarios de 2 BitsDocumento6 páginasSumador de Dos Números Binarios de 2 BitsAfir MinayaAún no hay calificaciones

- Act4 Ed1Documento4 páginasAct4 Ed1KillSt4rtusAún no hay calificaciones

- IPN-ESII-Azcapotzalco-Proyecto-temporizador-motorDocumento7 páginasIPN-ESII-Azcapotzalco-Proyecto-temporizador-motorUziel HernandezAún no hay calificaciones

- Flipflop Tipo TDocumento5 páginasFlipflop Tipo TCarlos PerezAún no hay calificaciones

- Informe Sesión 07Documento11 páginasInforme Sesión 07JuanCarlosSanchezPeñaAún no hay calificaciones

- Lab 3Documento16 páginasLab 3mauroAún no hay calificaciones

- Digitales Fip FlopDocumento7 páginasDigitales Fip FlopEnderson Mayorca CasasAún no hay calificaciones

- Laboratorio 4 (E. Digital)Documento7 páginasLaboratorio 4 (E. Digital)NiltonRamírezAún no hay calificaciones

- Taller Mapa de KARNAUGH PDFDocumento22 páginasTaller Mapa de KARNAUGH PDFST.DANIEL PAEZAún no hay calificaciones

- Arquitectura y Organización de Computadores Pauta Certamen #1, 01/2022 Santiago, 14.05.2022Documento7 páginasArquitectura y Organización de Computadores Pauta Certamen #1, 01/2022 Santiago, 14.05.2022SecretoAún no hay calificaciones

- Informe de 5 - David Acuña - Lourdes VillamilDocumento12 páginasInforme de 5 - David Acuña - Lourdes VillamilDavid AcuñaAún no hay calificaciones

- Practica 2 Segundo ParcialDocumento5 páginasPractica 2 Segundo ParcialJoss RodriguezAún no hay calificaciones

- Cuestionario Previo 4 PDFDocumento13 páginasCuestionario Previo 4 PDFROBERTO GASPAR ESCOBEDO CONTRERASAún no hay calificaciones

- Sistemas Digitales Episunsa PDFDocumento7 páginasSistemas Digitales Episunsa PDFHugo WongAún no hay calificaciones

- Alarma de Incendios 2Documento7 páginasAlarma de Incendios 2Juan Pablo Escobar NaranjoAún no hay calificaciones

- Sistema de alarma de incendios digital basado en KarnaughDocumento7 páginasSistema de alarma de incendios digital basado en KarnaughJuan Pablo Díaz VélezAún no hay calificaciones

- Tarea 1Documento16 páginasTarea 1Mauricio Glez.Aún no hay calificaciones

- Diseño de circuito lógico para control de visualizador de vocales y máquina expendedoraDocumento6 páginasDiseño de circuito lógico para control de visualizador de vocales y máquina expendedoraNEM100% (1)

- Cálculo y diseño de estructuras de materiales compuestos de fibra de vidrioDe EverandCálculo y diseño de estructuras de materiales compuestos de fibra de vidrioAún no hay calificaciones

- Ensayo de La Pelicula AlphaDocumento3 páginasEnsayo de La Pelicula AlphaRubi Reyna0% (1)

- G23-Objetivos, Enfoques y Elementos Del CurriculumDocumento9 páginasG23-Objetivos, Enfoques y Elementos Del CurriculumJonathan ZuñigaAún no hay calificaciones

- HeinekenDocumento13 páginasHeinekenSERGIO LUÍS ARRIETA GONZALEZ ESTUDIANTEAún no hay calificaciones

- 2020 Parametros Reproductivos EficienciaDocumento20 páginas2020 Parametros Reproductivos EficienciaRey Benjamín Álvarez HernándezAún no hay calificaciones

- TRABAJO CONCLUIDO SEXTA EDICION HpoyDocumento109 páginasTRABAJO CONCLUIDO SEXTA EDICION HpoyRoberth Eisten Flores LauraAún no hay calificaciones

- VIH: Origen, Transmisión, Detección y TratamientoDocumento15 páginasVIH: Origen, Transmisión, Detección y TratamientoEkaterina Andrea Rodríguez VilchesAún no hay calificaciones

- Analizador de GasesDocumento28 páginasAnalizador de GasesKlau AleAún no hay calificaciones

- Plan Casero Fonoaudiología Conciencia Fonologica y ArticulaciónDocumento3 páginasPlan Casero Fonoaudiología Conciencia Fonologica y ArticulaciónOlga Patricia Porras AlbarracinAún no hay calificaciones

- Historia de La Educación A Distancia-1-7Documento7 páginasHistoria de La Educación A Distancia-1-7Liliana González DelgadoAún no hay calificaciones

- Taller 7 Estadística IIDocumento4 páginasTaller 7 Estadística IISalomé EstradaAún no hay calificaciones

- ECA421 Taller de InvestigacionDocumento11 páginasECA421 Taller de InvestigacionJuan De pazAún no hay calificaciones

- Semana 7 - Diseño y Medición de IndicadoresDocumento23 páginasSemana 7 - Diseño y Medición de IndicadoresErnesto Mueras QuevedoAún no hay calificaciones

- Mamani Cuyo Cesar AugustoDocumento60 páginasMamani Cuyo Cesar AugustoJosueChalloAún no hay calificaciones

- Tuvo María más hijos además de JesúsDocumento13 páginasTuvo María más hijos además de Jesússabino oAún no hay calificaciones

- Seleccion y Almacenamiento de TCRDocumento11 páginasSeleccion y Almacenamiento de TCRElisa Maria Vaquero BarahonaAún no hay calificaciones

- Seres vivos y su clasificaciónDocumento5 páginasSeres vivos y su clasificaciónjuan carreñoAún no hay calificaciones

- Proceso EstrellaDocumento2 páginasProceso EstrellaJaro VillarrealAún no hay calificaciones

- La Metodología de AudienciaDocumento3 páginasLa Metodología de Audienciajose luis garcia cruzAún no hay calificaciones

- Mantak Chia - Despierta La Energia Curativa Atraves Del TaoDocumento259 páginasMantak Chia - Despierta La Energia Curativa Atraves Del Taobarciga90% (29)

- Laboratorio de Física N - 05 UnmsmDocumento14 páginasLaboratorio de Física N - 05 UnmsmAgustinBruno0% (1)

- TPCC Ing 2023 1Documento6 páginasTPCC Ing 2023 1Adelmaro Aldair Ramos YupanquiAún no hay calificaciones

- FERRERO DIEZ CANSECO, A., Las Formas Especiales de Sociedad Anónima en La Nueva LGSDocumento17 páginasFERRERO DIEZ CANSECO, A., Las Formas Especiales de Sociedad Anónima en La Nueva LGSYakelyn SussanAún no hay calificaciones

- Cronograma-Escolar 2022 2023Documento4 páginasCronograma-Escolar 2022 2023Guillermo Gustavo Vallejo VillacísAún no hay calificaciones

- Estructura CapitalDocumento2 páginasEstructura CapitalfanyAún no hay calificaciones

- Nefropata 1600 SNGDocumento2 páginasNefropata 1600 SNGMiriam Flores ArredondoAún no hay calificaciones

- Ensayo Agricultura Tradicionla y ConvencionalDocumento4 páginasEnsayo Agricultura Tradicionla y Convencionalsimon pabonAún no hay calificaciones

- Metodo de Los 20 Dias Tomo 1Documento54 páginasMetodo de Los 20 Dias Tomo 1Yuni AlMon100% (3)

- Panfleto #01 - El Cielo Abierto - Jose Bates 1846Documento29 páginasPanfleto #01 - El Cielo Abierto - Jose Bates 1846Jose Estuardo Ventura GutierrezAún no hay calificaciones

- Ficha Tecnica (Soldadora)Documento3 páginasFicha Tecnica (Soldadora)Jonathan Teran Ruiz100% (1)

- C9 Avon Minifolleto Especial Higienicos PDFDocumento49 páginasC9 Avon Minifolleto Especial Higienicos PDFHéctor HernándezAún no hay calificaciones