Documentos de Académico

Documentos de Profesional

Documentos de Cultura

UIS - 2022 - 1 - Sistemas Digitales I - Parcial 3 - Sistemas Secuenciales

UIS - 2022 - 1 - Sistemas Digitales I - Parcial 3 - Sistemas Secuenciales

Cargado por

Kevin Farith Garcia ChaparroDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

UIS - 2022 - 1 - Sistemas Digitales I - Parcial 3 - Sistemas Secuenciales

UIS - 2022 - 1 - Sistemas Digitales I - Parcial 3 - Sistemas Secuenciales

Cargado por

Kevin Farith Garcia ChaparroCopyright:

Formatos disponibles

Escuela de Ingeniería Eléctrica, Electrónica y de Telecomunicaciones

Sistemas Digitales I

Parcial No. 3

NOMBRE:______________________________________ CÓDIGO:________

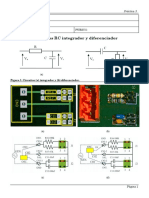

Punto 1: [2.0 unidades] Linea de tiempo con FF y Latch Reset asinc

Considere el circuito de la figura. Asuma que el valor inicial de todos los

registros es cero y complete una línea de tiempo de 20 ciclos de reloj con

las señales A, B, C, D, X, Z y Y..

Punto 2: [3.0 unidades]

Considere el circuito de la figura, el cual tiene una FSM cuyo diagrama de

estados también se presenta a continuación:

Puede asumir que el registro PIPO tiene valor inicial 0000 y que la FSM comienza en el “estado 1”. Para este circuito

cumpla con los siguientes requerimientos:

a. Complete una línea de tiempo hasta el ciclo de reloj 30 con las señales Z, X, Y, S y T.

b. Codifique los estados planteados en el diagrama de estados. ¿Cuántos bits tiene el registro de estado (Estado

presente) en su diseño?

c. Determine la tabla de verdad de la lógica del estado siguiente de la máquina de estados

d. Simplifique el circuito y presente solo la ecuación lógica que requiera el menor número de compuertas lógicas

(Opcional: si quiere chicanear con el profe, realice el diagrama esquemático).

e. Determine la tabla de verdad de la lógica de salida (incluyendo todas las salidas) de la máquina de estados.

f. Simplifique el circuito y presente solo la ecuación lógica que requiera el menor número de compuertas lógicas

de la señal de salida Y. (Opcional: si quiere chicanear con el profe, simplifique las otras salidas).

2022 - 1 - Parcial Nº3 1 Docente: W. Salamanca

También podría gustarte

- Métodos Matriciales para ingenieros con MATLABDe EverandMétodos Matriciales para ingenieros con MATLABCalificación: 5 de 5 estrellas5/5 (1)

- Sumador de 8bitsDocumento22 páginasSumador de 8bitsposkonono12591100% (8)

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208De EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208Aún no hay calificaciones

- TareaDocumento5 páginasTareaSantiago GuallichicoAún no hay calificaciones

- Puertas LogicasDocumento13 páginasPuertas LogicasturinatecnologiaAún no hay calificaciones

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Practica 3 ElectronicaDocumento24 páginasPractica 3 ElectronicaXimena J LanderosAún no hay calificaciones

- Examenes Etc IDocumento97 páginasExamenes Etc IJose RamirezAún no hay calificaciones

- PARCIAL IV Circuitos DigitalesDocumento6 páginasPARCIAL IV Circuitos DigitalesNubia DorantesAún no hay calificaciones

- EdC Conv3 Dic20 v2Documento3 páginasEdC Conv3 Dic20 v2Ashley ConejoAún no hay calificaciones

- PRACTICA #5 - Sumador de 2 BitsDocumento6 páginasPRACTICA #5 - Sumador de 2 BitsNathaly Murcia SepulvedaAún no hay calificaciones

- Laboratorio 1 Modelado y SimulacionDocumento8 páginasLaboratorio 1 Modelado y SimulacionMireya NacevillaAún no hay calificaciones

- Laboratorio 1 Modelado y Simulacion 4278 y 4281Documento7 páginasLaboratorio 1 Modelado y Simulacion 4278 y 4281Cesar BautistaAún no hay calificaciones

- Capitulo 3 Libro Shaum Circuitos DigitalesDocumento62 páginasCapitulo 3 Libro Shaum Circuitos DigitalesKatherine María Zambrano CasasAún no hay calificaciones

- 2007-08 Ejercicios SeptDocumento18 páginas2007-08 Ejercicios SeptJulian PerezAún no hay calificaciones

- ElectrotecniaDocumento11 páginasElectrotecniaMiguel Alejandro SoméAún no hay calificaciones

- Guía 5-Sistemas DigitalesDocumento9 páginasGuía 5-Sistemas DigitalesVictor MelaraAún no hay calificaciones

- Lab 1Documento7 páginasLab 1Iván Darío Yaber ManotasAún no hay calificaciones

- Examen Parcial Sistemas 2020-0Documento13 páginasExamen Parcial Sistemas 2020-0YAIR ROBERTO MALASQUEZ VILCHEZAún no hay calificaciones

- Problem As Circuit Os Secuencia Les 0405Documento4 páginasProblem As Circuit Os Secuencia Les 0405MaríaAmarantoAún no hay calificaciones

- Preparatorio 2Documento6 páginasPreparatorio 2Jorge Chalco MHAún no hay calificaciones

- Problema 1 - 5 Puntos) : Electrónica Digital Grados en Ingeniería Tecnologías de TelecomunicaciónDocumento4 páginasProblema 1 - 5 Puntos) : Electrónica Digital Grados en Ingeniería Tecnologías de TelecomunicaciónelenaAún no hay calificaciones

- Problem Ass DigDocumento107 páginasProblem Ass DigYani Ivanov ManovAún no hay calificaciones

- Informe 1 - Grupo 04 - ViernesDocumento11 páginasInforme 1 - Grupo 04 - ViernesSergio Andres Bernal TorresAún no hay calificaciones

- Practica3 2019Documento25 páginasPractica3 2019rc7pablorAún no hay calificaciones

- TP2 Simplificación-2024Documento5 páginasTP2 Simplificación-2024Magali GutierrezAún no hay calificaciones

- Labo 2Documento4 páginasLabo 2Ayrton Abanto GuerreroAún no hay calificaciones

- LABORATORIO 05 - 2 Contadores AsincronosDocumento5 páginasLABORATORIO 05 - 2 Contadores AsincronosDarwin YoverdAún no hay calificaciones

- 02 Lab02Documento4 páginas02 Lab02Jorge ElguetaAún no hay calificaciones

- Coleccion Problem As CA 3Documento134 páginasColeccion Problem As CA 3Ronny RamírezAún no hay calificaciones

- IDL2020 Pca2Documento7 páginasIDL2020 Pca2Electro MotiveAún no hay calificaciones

- Laboratorio Circuitos CombinatoriosDocumento11 páginasLaboratorio Circuitos CombinatoriosHeyner Marmol VerbelAún no hay calificaciones

- Diseño de Sistemas Controladores Combinacionales 4Documento8 páginasDiseño de Sistemas Controladores Combinacionales 4Gadiel Armijos VAún no hay calificaciones

- Lab10 Dispos Mendoza Rosales C15 4 CDocumento11 páginasLab10 Dispos Mendoza Rosales C15 4 CJairo Hans Cardenas MauricioAún no hay calificaciones

- 2021 1S Cit2109 Lab 3Documento2 páginas2021 1S Cit2109 Lab 3xdadaAún no hay calificaciones

- Reloj DigitalDocumento6 páginasReloj DigitalJosé Alberto GarcíaAún no hay calificaciones

- Lab09 Máquinas de EstadoDocumento5 páginasLab09 Máquinas de EstadoFelix Vidal De La Cruz Mauricio0% (1)

- Practica 2 Electrónica Equipo 14Documento23 páginasPractica 2 Electrónica Equipo 14Ximena J LanderosAún no hay calificaciones

- Practica 3Documento5 páginasPractica 3ALFREDO SANTILLANAún no hay calificaciones

- Ejemplo ExamenDocumento3 páginasEjemplo ExamenSixto Manrique MirandaAún no hay calificaciones

- Laboratorio - Informe - 5 Sumador y Restador CompletosDocumento3 páginasLaboratorio - Informe - 5 Sumador y Restador CompletosBryan RodriguezAún no hay calificaciones

- SumadoresDocumento5 páginasSumadoresLenin Oñate100% (1)

- LABORATORIO 11 Contadores AsincronosDocumento5 páginasLABORATORIO 11 Contadores AsincronosJimm AyllónAún no hay calificaciones

- Tema 6bDocumento33 páginasTema 6bSilvio CondoriAún no hay calificaciones

- Automata FinitoDocumento8 páginasAutomata Finitoiceman2305Aún no hay calificaciones

- Feb 05Documento10 páginasFeb 05Sasuke BacusAún no hay calificaciones

- Automata FinitoDocumento9 páginasAutomata FinitoMCTLVAún no hay calificaciones

- Estudio 1Documento7 páginasEstudio 1Danilo FernandezAún no hay calificaciones

- Ejercicios U2 Circuitos DigitalesDocumento7 páginasEjercicios U2 Circuitos Digitalesvaleria castañonAún no hay calificaciones

- Guion p3Documento5 páginasGuion p3estelaAún no hay calificaciones

- LABORATORIO 09 (Máquinas de Estado)Documento15 páginasLABORATORIO 09 (Máquinas de Estado)julio enriqueAún no hay calificaciones

- Laboratorio 5 Electronica III V2Documento8 páginasLaboratorio 5 Electronica III V2CRISTIAN CAMILO MORALES SOLISAún no hay calificaciones

- EDigital - Actividad - Semana 13Documento5 páginasEDigital - Actividad - Semana 13ulisesAún no hay calificaciones

- Informe Previo FINALDocumento21 páginasInforme Previo FINALYury Rojas CarbajalAún no hay calificaciones

- Electrónica II, Grupo IDocumento19 páginasElectrónica II, Grupo IMoises VillarroelAún no hay calificaciones

- LAB 12 - MultivibradoresDocumento13 páginasLAB 12 - MultivibradoresDiego ClavijoAún no hay calificaciones

- Lab#1 Introducción Al Circuit MakerDocumento17 páginasLab#1 Introducción Al Circuit Makerلويس أنتوني نونيزAún no hay calificaciones

- Practica 2 - Circuitos CombinacionalesDocumento14 páginasPractica 2 - Circuitos CombinacionalesMario Poveda NavaroAún no hay calificaciones

- Diseño de Sistemas Controladores CombinacionalesDocumento10 páginasDiseño de Sistemas Controladores CombinacionalesGadiel Armijos VAún no hay calificaciones

- Laboratorio 2 Elt3890-2-2020Documento6 páginasLaboratorio 2 Elt3890-2-2020Joel CahuanaAún no hay calificaciones