Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Parc1 Grupo1

Cargado por

Jose San Felipe SanchezTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Parc1 Grupo1

Cargado por

Jose San Felipe SanchezCopyright:

Formatos disponibles

1º parcial – Sistemas Digitales basados en Microprocesador

2º curso de grado en Ingeniería de Telecomunicaciones

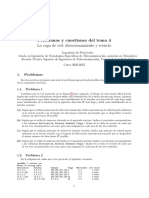

En la figura aparece la unidad operativa de un circuito generador del bit de paridad. Consta básicamente de un

registro de desplazamiento de 4 celdas (a la derecha) y un registro de 1 celda donde se almacena el bit de paridad

generado por el circuito.

Partiendo de un estado de espera, en el que todos los controles se encuentran inactivos, tras la activación del

inicializador X a 1, el circuito almacena en paralelo la palabra de 4 bits (A3 A2 A1 A0) en el registro de desplazamiento.

Genera el bit de paridad (bit de paridad a 1 si el número de 1’s de la palabra A es impar) y lo almacena en el registro

de 1 celda. Por último, el número A convertido en un número de 6 bits (los 4 originales + el bit paridad + 1 bit de

parada (0)) se transmite en serie por la salida DATA_OUT. Una salida adicional BUSY a 1 indicará que los 6 bits se

están transmitiendo. El sistema también consta de un contador con indicador de estado 000 (Z) para llevar cuenta

de los bits que se van transmitiendo.

A3 A2 A1 A0

Entrada_paralelo

0 I0 LOAD

MUX IN OUT entrada_serie DATA_OUT

I1 SHIFT salida_serie

Salida_paralelo

LOADQ

SEL

101

3

INIT

CONTADOR Z

DEC

Se pide:

Estructura interna del registro de desplazamiento y del registro de un bit teniendo en cuenta que todas las

operaciones son síncronas utilizando flip-flops D y las puertas lógicas necesarias.

Diagrama ASM del controlador del circuito implementado como autómata de Moore.

También podría gustarte

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208De EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208Aún no hay calificaciones

- Compuertas LógicasDocumento16 páginasCompuertas LógicasOskary SosaAún no hay calificaciones

- Manual Del Laboratorio de Electrónica Digital IDocumento211 páginasManual Del Laboratorio de Electrónica Digital IMadeline ReynosoAún no hay calificaciones

- Automatas ProgramablesDocumento9 páginasAutomatas ProgramablesGonzalo Todd Peñafiel CaballeroAún no hay calificaciones

- Introducción A Los Controladores Logicos ProgramablesDocumento38 páginasIntroducción A Los Controladores Logicos ProgramablesGeorge LizarragaAún no hay calificaciones

- 1era Asignacion Grupo 2. Norma Isa S-5.2 Diagramas LogicosDocumento5 páginas1era Asignacion Grupo 2. Norma Isa S-5.2 Diagramas LogicosChristian E. Betancourt AguileraAún no hay calificaciones

- Práctica 3 VHDLDocumento8 páginasPráctica 3 VHDLHoracio Fernández JiménezAún no hay calificaciones

- Alu Controlada Por Registro PipoDocumento20 páginasAlu Controlada Por Registro PipoStiva DarcyAún no hay calificaciones

- Certamen 2 Digitales Automotriz Forma A 2022Documento8 páginasCertamen 2 Digitales Automotriz Forma A 2022Segundo GarcesAún no hay calificaciones

- Circuitos CombinacionalesDocumento18 páginasCircuitos CombinacionalesAratz17Aún no hay calificaciones

- Circuitos DigitalesDocumento40 páginasCircuitos DigitalestadekotardeAún no hay calificaciones

- Convertidor B-H P4Documento17 páginasConvertidor B-H P4Jorge Alberto Ortiz GalloAún no hay calificaciones

- Compuertas LogicasDocumento8 páginasCompuertas LogicasAlejandro SierraAún no hay calificaciones

- Pre Informe 3Documento13 páginasPre Informe 3Quicaño PradoAún no hay calificaciones

- Practica #1 Alarma de BancoDocumento3 páginasPractica #1 Alarma de BancoDaniel GonzalezAún no hay calificaciones

- Ejemplo Contador Del 0 Al 99Documento16 páginasEjemplo Contador Del 0 Al 99George MoreloAún no hay calificaciones

- Informe Previo 1Documento27 páginasInforme Previo 1Luis Alva FuertesAún no hay calificaciones

- Redes (Practica) - Javier PDFDocumento9 páginasRedes (Practica) - Javier PDFJavier PinalesAún no hay calificaciones

- Orgasmall DatasheetDocumento8 páginasOrgasmall Datasheetcarlos menemAún no hay calificaciones

- Lengueje de Transf de RegDocumento62 páginasLengueje de Transf de RegluisAún no hay calificaciones

- Clase #11 - Circuitos Combinacionales - Parte 1Documento38 páginasClase #11 - Circuitos Combinacionales - Parte 1jjcorderoAún no hay calificaciones

- Circuito Ascensor Mux y DemuxDocumento9 páginasCircuito Ascensor Mux y DemuxTonny Richard100% (2)

- Arquitectura ALUDocumento20 páginasArquitectura ALUZachary Higgins0% (1)

- Preinforme5 V2 EdisonAbadoAnccoDocumento4 páginasPreinforme5 V2 EdisonAbadoAnccoEdison Abado AnccoAún no hay calificaciones

- Controladores IDocumento9 páginasControladores IjosegabriellopezaponteAún no hay calificaciones

- Practica 15Documento8 páginasPractica 15Jesuup HazAún no hay calificaciones

- Circuito LógicoDocumento26 páginasCircuito LógicotjsuniagaAún no hay calificaciones

- Laboratorio Digitales IDocumento8 páginasLaboratorio Digitales IOmarsinho10Aún no hay calificaciones

- Informe 4 en ProcesoDocumento22 páginasInforme 4 en ProcesobassAún no hay calificaciones

- Sumador Restador BCDDocumento46 páginasSumador Restador BCDLuis Fernando BravoAún no hay calificaciones

- Compuertas LogicasDocumento7 páginasCompuertas LogicasreloxAún no hay calificaciones

- Que Significa TTL y CMOS PDFDocumento5 páginasQue Significa TTL y CMOS PDFgtranAún no hay calificaciones

- RegistroDocumento15 páginasRegistroRafael RamoscordovaAún no hay calificaciones

- Información Que Me Dió Mi EsposaDocumento27 páginasInformación Que Me Dió Mi EsposaSantiago DazaAún no hay calificaciones

- Diagrama Asm 1Documento6 páginasDiagrama Asm 1Jhozy CuevaAún no hay calificaciones

- 10 - Redes de Dos PuertosDocumento15 páginas10 - Redes de Dos Puertosjuan piñerosAún no hay calificaciones

- 1 Sistemas DigitalesDocumento9 páginas1 Sistemas DigitalesArturo LobatónAún no hay calificaciones

- Consulta de Tablas de Verdad de Los Conpuestos Logicos NotDocumento3 páginasConsulta de Tablas de Verdad de Los Conpuestos Logicos NotSanti SarangoAún no hay calificaciones

- Capacidad de Carga de La Familia TTL - Presentacion - Digital - Grupo - 3Documento16 páginasCapacidad de Carga de La Familia TTL - Presentacion - Digital - Grupo - 3rxaviervaAún no hay calificaciones

- Informe 4 Circuitos Digitales PDFDocumento7 páginasInforme 4 Circuitos Digitales PDFJorge AntonioAún no hay calificaciones

- 1 Introducción: 3. Trabajo ExperimentalDocumento4 páginas1 Introducción: 3. Trabajo ExperimentalcarlosAún no hay calificaciones

- Pre Laboratorio IIIDocumento14 páginasPre Laboratorio IIIGuillermo garciaAún no hay calificaciones

- Proyecto FinalDocumento21 páginasProyecto FinalIsrael SimoneAún no hay calificaciones

- TAREA 3-Edgar Perdomo PorrasDocumento13 páginasTAREA 3-Edgar Perdomo PorrasedgarAún no hay calificaciones

- Diseño Sumador RestdorDocumento10 páginasDiseño Sumador RestdorRamiro David MAún no hay calificaciones

- MSI2Documento5 páginasMSI2Juan Diego OchoaAún no hay calificaciones

- Circuitos DigitalesDocumento11 páginasCircuitos DigitalesKristian AlmanzarAún no hay calificaciones

- Programacion PLCDocumento10 páginasProgramacion PLCRosa SofíaAún no hay calificaciones

- Práctica 1Documento8 páginasPráctica 1Memoo PachecoAún no hay calificaciones

- Informe Compuertas LógicasDocumento5 páginasInforme Compuertas LógicasAlvaro MenaAún no hay calificaciones

- Digitales 1 Era semana-UNACDocumento13 páginasDigitales 1 Era semana-UNACLUIS PERCYAún no hay calificaciones

- Compuertas InformeDocumento6 páginasCompuertas Informedavid saldarriagaAún no hay calificaciones

- Texto ComplementarioDocumento7 páginasTexto ComplementarioVICTOR HUGO CHOQUE CRUZAún no hay calificaciones

- Electronica Digital-U2Documento14 páginasElectronica Digital-U2Mario PinedaAún no hay calificaciones

- Pa Que Estudien Los PibesDocumento4 páginasPa Que Estudien Los PibesLautaro PazAún no hay calificaciones

- UNIVERSIDAD DE COLIMA Act3 Compuertas LogicasDocumento13 páginasUNIVERSIDAD DE COLIMA Act3 Compuertas LogicasLOPEZ SANCHEZ ROBERTOAún no hay calificaciones

- Compuertas LógicasDocumento15 páginasCompuertas LógicasDGladysVilchezCAún no hay calificaciones

- Tablas de VRDDocumento8 páginasTablas de VRDJuan Alberto Izquierdo FiscalAún no hay calificaciones

- 8085 Cas18Documento50 páginas8085 Cas18Carlos Javier BarriosAún no hay calificaciones

- LAB1 InformeDocumento8 páginasLAB1 InformeHector Polanco AlvarezAún no hay calificaciones

- Solucion Parcial 21 22Documento3 páginasSolucion Parcial 21 22Jose San Felipe SanchezAún no hay calificaciones

- Parc1 16-17Documento2 páginasParc1 16-17Jose San Felipe SanchezAún no hay calificaciones

- Parc1 13-14Documento2 páginasParc1 13-14Jose San Felipe SanchezAún no hay calificaciones

- Practica 2Documento3 páginasPractica 2Jose San Felipe SanchezAún no hay calificaciones

- Enunciados-Tema 2Documento2 páginasEnunciados-Tema 2Jose San Felipe SanchezAún no hay calificaciones

- Ejercicios Basicos Curso2017-2018Documento20 páginasEjercicios Basicos Curso2017-2018Jose San Felipe SanchezAún no hay calificaciones

- Campos Escalares y VectorialesDocumento3 páginasCampos Escalares y VectorialesJose San Felipe SanchezAún no hay calificaciones

- PlandetrabajoDocumento1 páginaPlandetrabajoJose San Felipe SanchezAún no hay calificaciones

- Ejercicios FisicaDocumento3 páginasEjercicios FisicaJose San Felipe SanchezAún no hay calificaciones

- Notas Tema3Documento3 páginasNotas Tema3Jose San Felipe SanchezAún no hay calificaciones

- Problemas Tema 4Documento15 páginasProblemas Tema 4Jose San Felipe SanchezAún no hay calificaciones