Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Mapa 3 TK

Cargado por

Mario LazoTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Mapa 3 TK

Cargado por

Mario LazoCopyright:

Formatos disponibles

Nuevos dispositivos para la lógica:

Tal y como escribimos, se conocen varios principios físicos distintos por los que un conmutador

controlado por tensión (es decir, un dispositivo similar a un transistor) podría evitar el límite de

escalado de tensión del FET convencional.8,16 Por ejemplo, algunos de estos principios de

funcionamiento invocan un mecanismo físico que rompe el vínculo directo entre la tensión de

funcionamiento aplicada externamente y el potencial interno que abre el flujo de corriente. Por

supuesto, el simple hecho de cambiar la física del dispositivo para incorporar uno de estos

principios de funcionamiento no garantiza un interruptor digital de bajo voltaje más eficiente

desde el punto de vista energético. Para cada concepto de dispositivo propuesto, las

características de conmutación y otros atributos importantes del dispositivo dependerán

fundamentalmente de las propiedades alcanzables de los materiales y de los detalles de la

estructura del dispositivo.

Todos los conceptos de dispositivos de bajo voltaje propuestos actualmente se encuentran todavía

en la fase inicial de investigación. Los prototipos de laboratorio aún no presentan características

que justifiquen el desarrollo de un producto comercial. Sin embargo, muchos de estos conceptos

de dispositivos están evolucionando rápidamente a medida que los investigadores descubren y

comprenden los problemas e inventan soluciones. Por tanto, parece probable que se inventen más

dispositivos de bajo voltaje. Si en los próximos años aparece un dispositivo de bajo voltaje de alto

rendimiento, podría reducir en gran medida las restricciones de generación de energía y calor que

actualmente limitan la computación.

Nuevos dispositivos de memoria:

Varias fuerzas impulsan la exploración de nuevos dispositivos de memoria. Ya hemos mencionado

la creciente dificultad para miniaturizar aún más los dispositivos de memoria establecidos, es

decir, SRAM, DRAM y flash. Los nuevos dispositivos de memoria podrían ser más fáciles de escalar

a tamaños más pequeños. Una segunda fuerza impulsora es la cambiante carga de trabajo

informático. La jerarquía de memoria empleada hoy en día se ha optimizado para aplicaciones con

localización de datos, pero una fracción cada vez mayor de las cargas de trabajo habituales

implican datos poco estructurados y requieren un acceso frecuente a la memoria a través de un

gran espacio de direcciones. Este movimiento de datos es costoso tanto en latencia como en

consumo de energía, especialmente cuando los datos tienen que venir de la memoria fuera del

chip a través de un bus de datos con un ancho de banda limitado.17 El acceso a la memoria fuera

del chip puede suponer hasta el 90 por ciento de la energía y el tiempo de ejecución

correspondiente en los sistemas informáticos actuales que ejecutan algoritmos de uso intensivo

de datos.17 Por último, y quizás lo más importante, algunos dispositivos de memoria emergentes

pueden permitir una integración más rentable de grandes cantidades de memoria con la lógica. De

las tecnologías de memoria dominantes en la actualidad, sólo la SRAM puede integrarse

fácilmente con la lógica CMOS de alto rendimiento. Integrar la DRAM y la flash en el mismo chip

con los núcleos del procesador es difícil y a menudo no resulta rentable. Por ello, se están

explorando muchas opciones de dispositivos de memoria nuevos,18,19 como la RAM magnética

de par de transferencia de espín (STT-MRAM), la RAM ferroeléctrica (FERAM), la RAM de puente

conductor (CBRAM), la RAM resistiva (RRAM) y la memoria de cambio de fase (PCM). Todas estas

memorias comparten algunos atributos muy deseables: son no volátiles, cada célula de la matriz

de memoria puede leerse aleatoriamente sin destruir la información almacenada y escribirse sin

borrar primero el bit almacenado, cubren una amplia gama de características de lectura/escritura

que abarcan toda la jerarquía de la memoria, y se fabrican utilizando temperaturas inferiores a las

utilizadas para fabricar las interconexiones (los cables que conectan los transistores).

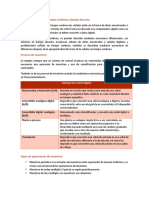

Figura 3. Energía de programación frente al área de la celda de memoria a partir de datos

publicados para las principales tecnologías de memoria no volátil emergentes: memoria magnética

de acceso aleatorio por transferencia de espín (STT-MRAM), memoria de cambio de fase (PCM),

memoria de acceso aleatorio por puente conductor (CBRAM) y memoria de acceso aleatorio

resistiva (RRAM). Tanto la STT-MRAM como la PCM requieren una densidad de corriente crítica

para cambiar el estado de la memoria, por lo que la energía de programación es proporcional

(líneas discontinuas moradas y verdes) al área de la célula de memoria. La conducción en la

CBRAM y la RRAM es filamentosa, por lo que la energía de programación es independiente del

área de la célula de memoria.

Los tres primeros atributos abren amplias oportunidades para replantear el diseño de la jerarquía

de memoria con el fin de optimizar la disipación de energía y el rendimiento para diversas cargas

de trabajo de las aplicaciones. El último atributo permite incorporar los dispositivos de memoria

por encima de los bloques de lógica CMOS y, por tanto, permite una integración perfecta y

detallada de la memoria y la lógica. Aunque comparten atributos comunes deseables, cada una de

estas tecnologías emergentes difiere de las demás y las complementa en función de atributos

clave: velocidad de lectura/escritura, potencia y consumo energético de lectura/escritura,

propiedades de retención y resistencia, y densidad del dispositivo (área de la célula de memoria).

Por ejemplo, la figura 3 muestra los datos publicados20 sobre la energía de escritura en relación

con el área de la célula de memoria. Las compensaciones varían mucho entre los distintos tipos de

memoria. La física de la conmutación magnética hace que la STT-MRAM sea singularmente rápida

y, por tanto, muy adecuada para colocarla cerca de los núcleos del procesador. Sin embargo, una

de sus limitaciones actuales es la elevada energía de escritura y el consiguiente consumo de

energía. La energía de escritura de la STT-MRAM (y también de la PCM) es proporcional al área de

la celda de memoria, ya que se requiere una determinada densidad de corriente para conmutar la

resistencia de la celda. En cambio, la energía de escritura de la RRAM y la CBRAM no depende del

área de la celda de memoria debido a la naturaleza filamentosa y a la pequeña sección transversal

de la vía de conducción. La miniaturización continua debería reducir el consumo de energía de la

STTMRAM y la PCM a niveles aceptables. Los continuos avances en los materiales y la física de los

dispositivos podrían reducir aún más el consumo de energía de estas memorias.

Nuevos dispositivos que combinan las funciones de la memoria y la lógica:

El magnetismo ha sido durante mucho tiempo la base de los dispositivos de almacenamiento de

información, como la unidad de disco duro y la STT-MRAM. Cuando un imán se hace más pequeño,

se necesita menos energía para cambiar su polarización. Además, los físicos y los científicos de

materiales han descubierto en los últimos años nuevos mecanismos de conmutación de bajo

consumo. Por ello, los investigadores están empezando a explorar y explotar la nueva física del

nanomagnetismo en dispositivos para la lógica digital. Los primeros conceptos de dispositivos para

la lógica magnética adolecían del inconveniente de que no había una forma sencilla y directa de

que el estado magnético de un dispositivo conmutara el estado magnético de otro dispositivo. (Un

diseñador de circuitos señalaría que los dispositivos no se concatenan.) Así, la lógica All-Spin, una

familia de dispositivos y circuitos nanomagnéticos que resuelve este problema,21 generó un gran

interés cuando se propuso. Otra dirección de investigación apasionante es el magnetismo

controlado por voltaje.22 En comparación con un mecanismo de conmutación controlado por

corriente como el empleado en la STTMRAM, los dispositivos magnéticos controlados por voltaje

deberían ser más rápidos y más eficientes energéticamente. Gran parte del interés por la lógica

nanomagnética reside en la promesa de combinar las funciones de lógica y memoria en un único

dispositivo. Estos dispositivos podrían eliminar la necesidad de guardar el estado de un cálculo en

la memoria antes de apagar la alimentación. Esta capacidad tendría un valor inmediato en los

sistemas con escasez de energía que dependen de fuentes de energía intermitentes y, a largo

plazo, podría cambiar profundamente la arquitectura de los ordenadores.

Nuevos procesos de integración:

La realización de una lógica y una memoria multicapa integradas monolíticamente sería una

revolución, y esa revolución podría estar ya gestándose. La memoria flash multicapa, con 48 capas,

ya se está produciendo y representa una de las primeras tecnologías de dispositivos en adoptar

realmente la integración monolítica en 3D como vía de avance tecnológico. La mezcla de lógica y

memoria en pilas 3D monolíticas es mucho más fácil si se pueden evitar las altas temperaturas que

suelen ser necesarias para la síntesis de capas sucesivas de materiales electrónicos en el proceso

de integración de dispositivos a baja temperatura. Además, las capas del dispositivo deben ser

muy finas para que los agujeros para las conexiones eléctricas entre las capas puedan tener una

baja relación de aspecto. Por lo tanto, es deseable sintetizar material de alta calidad para una capa

de dispositivo a alta temperatura, adelgazar la capa y transferirla posteriormente a la pila. En el

caso del silicio, este concepto de transferencia de capas tiene una larga historia23,24 con un

historial probado como proceso de fabricación.25 Los materiales electrónicos emergentes, como

los nanotubos de carbono26 y los cristales atómicos 2D27, son prometedores como futuros

materiales de canal de FET porque sus estructuras cristalinas naturales son atómicamente

delgadas debido a la configuración especial de enlace de los átomos constituyentes, y su

transporte de portadores no se ve afectado por las imperfecciones de las superficies. Estos

materiales, que se sintetizan y luego se transfieren a un sustrato de destino para su integración en

3D, están avanzando rápidamente hacia el cumplimiento de los objetivos de rendimiento futuros.

Muchas de las nuevas memorias descritas anteriormente ya utilizan materiales depositados a baja

temperatura y, por tanto, son acordes con las tecnologías de integración monolítica en 3D.

Aunque cada capa adicional supone una cierta pérdida de rendimiento, un chip 2D convencional

con una superficie equivalente sufriría una pérdida de rendimiento similar sin la ventaja de unas

interconexiones 3D mucho más cortas y sin la posibilidad de optimizar los procesos de fabricación

de cada capa del dispositivo. Así, dentro de no muchos años, un sistema informático podría tener

archivos de registro y SRAM como caché rápida de primer nivel. La caché de segundo nivel podría

utilizar STT-MRAM de alta resistencia y acceso rápido o una variante. Una memoria más lenta, no

volátil y de muy alta densidad en la jerarquía de memoria podría utilizar PCM, RRAM o CBRAM,

integradas monolíticamente con los núcleos del procesador. La RRAM y la CBRAM ya han

demostrado su capacidad de lectura/escritura a aproximadamente 1 V a una velocidad de 10 ns,

con más de mil millones de ciclos de resistencia y una buena eficiencia energética. Ya se han

demostrado las arquitecturas de dispositivos para una RRAM 3D que utiliza un enfoque rentable

que no requiere un paso de litografía para cada capa adicional. Con un tamaño de patrón futuro

de 5 nm de medio paso y 128 capas de estructura 3D, podrían residir 64 Tbits de memoria no

volátil relativamente rápida en un solo chip de microprocesador.

También podría gustarte

- Actividades Tema 1Documento16 páginasActividades Tema 1inf11 inf11Aún no hay calificaciones

- Memoria DramDocumento3 páginasMemoria DramCARLOS DAVID SIERRA RODRIGUEZAún no hay calificaciones

- DramDocumento9 páginasDramnumber1oneAún no hay calificaciones

- MulticoreDocumento25 páginasMulticoreMario EnriqueAún no hay calificaciones

- Imprimir Ya... !Documento2 páginasImprimir Ya... !Cristian Andres Fuentes CarbajalAún no hay calificaciones

- Tarea2 44653894SDocumento2 páginasTarea2 44653894SJ8IgnacioAún no hay calificaciones

- Memoria InternaDocumento6 páginasMemoria InternaSerolf HtrebehAún no hay calificaciones

- IngProyecto MemristoresDocumento0 páginasIngProyecto MemristoresJose RodriguezAún no hay calificaciones

- Guía No. 3 - Memoria InternaDocumento18 páginasGuía No. 3 - Memoria InternaJainer OlivoAún no hay calificaciones

- Tarea Memorias DigitalDocumento9 páginasTarea Memorias Digitalfraidi mena machadoAún no hay calificaciones

- VRAMDocumento54 páginasVRAMJairo Márquez100% (1)

- Trabajo de CircuitosDocumento50 páginasTrabajo de Circuitosanon-791282100% (2)

- Historia Del CPUDocumento8 páginasHistoria Del CPULuis RiveraAún no hay calificaciones

- Memorias: Tipos Y Funcionamiento: 1º Montaje Y Mtto de EquiposDocumento25 páginasMemorias: Tipos Y Funcionamiento: 1º Montaje Y Mtto de Equiposluis - peligroAún no hay calificaciones

- Trabajo Final CMOS y TTLDocumento11 páginasTrabajo Final CMOS y TTLMarcos LinaresAún no hay calificaciones

- Memoria RAMDocumento3 páginasMemoria RAMLuz Karina Ticona ChaconAún no hay calificaciones

- Grupo # 4 - Daniel, Jeycob y Josue - Cap # 5 - Memoria InternaDocumento3 páginasGrupo # 4 - Daniel, Jeycob y Josue - Cap # 5 - Memoria InternarebeAún no hay calificaciones

- EpromDocumento16 páginasEpromEvelin TmtzAún no hay calificaciones

- Ortega Navarro Lariza YexalenDocumento14 páginasOrtega Navarro Lariza Yexalenlariza.ortega5360Aún no hay calificaciones

- Arquitectura de ComputadorDocumento3 páginasArquitectura de ComputadorluisAún no hay calificaciones

- Apunte Memorias DRAMDocumento17 páginasApunte Memorias DRAMMirta VerónAún no hay calificaciones

- Las Memorias Almacenan Datos en Unidades de Memoria de 1 Bits A 8 BitsDocumento3 páginasLas Memorias Almacenan Datos en Unidades de Memoria de 1 Bits A 8 BitsAnderson GarciaAún no hay calificaciones

- Ensayo de Memorias MultiplexacionDocumento6 páginasEnsayo de Memorias MultiplexacionPaul Chkmx GuamanAún no hay calificaciones

- Epiet Ta 5 Sistemas Digitales IIDocumento20 páginasEpiet Ta 5 Sistemas Digitales IIahalonso100% (1)

- Memorias FlashDocumento6 páginasMemorias FlashRuben Alejandro Carmilema TonatoAún no hay calificaciones

- Módulo 03 Sistemas Digitales y EnsambladoresDocumento9 páginasMódulo 03 Sistemas Digitales y EnsambladoresBrayan VargasAún no hay calificaciones

- Optimizacion y Control de La MemoriaDocumento15 páginasOptimizacion y Control de La Memoriadani jamAún no hay calificaciones

- Tipos de ComputadorasDocumento12 páginasTipos de Computadorasfernanda velasquezAún no hay calificaciones

- Semiconductores de PotenciaDocumento5 páginasSemiconductores de PotenciaRafael Santos PérezAún no hay calificaciones

- El Manual de Microprocesador IIDocumento15 páginasEl Manual de Microprocesador IIOliver PangoAún no hay calificaciones

- Monografia RamDocumento58 páginasMonografia RamNilton Cesar Arana GálvezAún no hay calificaciones

- Modulo 05 Docencia en Computación e InformáticaDocumento41 páginasModulo 05 Docencia en Computación e Informáticakevin salasAún no hay calificaciones

- Evolución de La Memoria RAMDocumento16 páginasEvolución de La Memoria RAMMatías Daniel Gaona RiquelmeAún no hay calificaciones

- Generaciones de Las Computadoras (s2-1)Documento5 páginasGeneraciones de Las Computadoras (s2-1)Kevin alexander nuñez paulinoAún no hay calificaciones

- ResumenDocumento6 páginasResumenLupita BarbosaAún no hay calificaciones

- Hardware y SoftwareDocumento15 páginasHardware y SoftwareJAVIER RAMIREZ HUARCAYAAún no hay calificaciones

- Manual de Especificacines de Los Pic de La Familia 16fDocumento65 páginasManual de Especificacines de Los Pic de La Familia 16fBlen TamayoAún no hay calificaciones

- Memoria InternaDocumento14 páginasMemoria InternaOmar Yire MendozaAún no hay calificaciones

- Monografia CmosDocumento7 páginasMonografia CmosAnonymous JtjuKiHXAún no hay calificaciones

- Informe Proyecto MemoriasDocumento7 páginasInforme Proyecto MemoriasHiroshi Matsushita SalasAún no hay calificaciones

- Circuitos DigitalesDocumento40 páginasCircuitos Digitalesapi-3771560100% (1)

- Tema3 MemoriaRAM PDFDocumento13 páginasTema3 MemoriaRAM PDFAlberto VelazquezAún no hay calificaciones

- MemoriasDocumento11 páginasMemoriasMalenie VelaAún no hay calificaciones

- Evolucion de Las MemoriasDocumento15 páginasEvolucion de Las Memoriasjefferson1483% (6)

- 26 Los Dispositivos de Procesamiento y MemoriaDocumento6 páginas26 Los Dispositivos de Procesamiento y MemoriaJonathan Martinez RamirezAún no hay calificaciones

- FAMILIAS LÓGICAS Cmos y EclDocumento39 páginasFAMILIAS LÓGICAS Cmos y EclGabriela_MorilloAún no hay calificaciones

- Sistemas de Almacenamiento Externo. Tipos. Características y FuncionamientoDocumento10 páginasSistemas de Almacenamiento Externo. Tipos. Características y FuncionamientosirdegAún no hay calificaciones

- TEMA 1 - INTRODUCCION A LOS EQUIPOS MICROINFORMATICOS (OSCAR RODRIGUEZ) .OdtDocumento18 páginasTEMA 1 - INTRODUCCION A LOS EQUIPOS MICROINFORMATICOS (OSCAR RODRIGUEZ) .OdtPepe VallsAún no hay calificaciones

- Tecnologías de Programación en Las FpgaDocumento7 páginasTecnologías de Programación en Las FpgaOmatsito YanchaAún no hay calificaciones

- Reporte 3 - 1851170 - TSdeCDocumento6 páginasReporte 3 - 1851170 - TSdeCcarlosw martinezAún no hay calificaciones

- Memoria Flash 2013Documento14 páginasMemoria Flash 2013Carlos CBAún no hay calificaciones

- EE03804CDocumento56 páginasEE03804CCasa SoleAún no hay calificaciones

- Memoria RAM Es Un Sistema de Almacenamiento de DatosDocumento23 páginasMemoria RAM Es Un Sistema de Almacenamiento de DatosMänüel ÊëhëvërriiAún no hay calificaciones

- Micromouse - Elección de MaterialesDocumento4 páginasMicromouse - Elección de MaterialesErick MartinezAún no hay calificaciones

- Practica Calificada 1Documento6 páginasPractica Calificada 1Mayckol Hernandez LojaAún no hay calificaciones

- Custionario Hardware 2Documento2 páginasCustionario Hardware 2Roberto Sebastián Carvajal100% (3)

- 1.2.2.2 Memoria PrincipalDocumento22 páginas1.2.2.2 Memoria PrincipalkarenAún no hay calificaciones

- MEMS para Teléfonos InteligentesDocumento15 páginasMEMS para Teléfonos InteligentesJavier Alonso YncaAún no hay calificaciones

- 04 Almacenamiento MagnéticoDocumento44 páginas04 Almacenamiento MagnéticopaulAún no hay calificaciones

- 100 Circuitos de Shields para MotoresDe Everand100 Circuitos de Shields para MotoresCalificación: 4.5 de 5 estrellas4.5/5 (4)

- Curso moderno de máquinas eléctricas rotativas: Las máquinas eléctricas en régimen dinámicoDe EverandCurso moderno de máquinas eléctricas rotativas: Las máquinas eléctricas en régimen dinámicoAún no hay calificaciones

- Actualizacion Del Contrato de Adm.Documento2 páginasActualizacion Del Contrato de Adm.joseAún no hay calificaciones

- Temario MicrocontroladoresDocumento2 páginasTemario MicrocontroladoresArchival RangelAún no hay calificaciones

- Acta de Registro Vehicular NCPPDocumento3 páginasActa de Registro Vehicular NCPPWilly Molina100% (1)

- Especialidad Conquistadores - Computacion IDocumento7 páginasEspecialidad Conquistadores - Computacion IMatías CartesAún no hay calificaciones

- Informe Inventario Equipos de BajaDocumento1 páginaInforme Inventario Equipos de BajaJonatan AraratAún no hay calificaciones

- Modulo 3 Manejo Dinamico de Memoria (Conceptos Y Clase Nodo Simple) IntroducciónDocumento8 páginasModulo 3 Manejo Dinamico de Memoria (Conceptos Y Clase Nodo Simple) Introducciónpatricia isazaAún no hay calificaciones

- 8.01 Evaluación de RiesgosDocumento7 páginas8.01 Evaluación de RiesgosmapazazelAún no hay calificaciones

- Tarea 1 - Judith Galvez GarciaDocumento3 páginasTarea 1 - Judith Galvez GarciaMe yoAún no hay calificaciones

- In-Mkc-005 Manual de Usuario Datascope-V2-OkDocumento36 páginasIn-Mkc-005 Manual de Usuario Datascope-V2-OkmaikolAún no hay calificaciones

- Procedimientolicenciapersonaltecnicoaeronauticodgac Nov 13.mexDocumento43 páginasProcedimientolicenciapersonaltecnicoaeronauticodgac Nov 13.mexfelix magdalenoAún no hay calificaciones

- 2.05 Especificaciones Técnicas Del Equipo Médico ... - ParsaludDocumento209 páginas2.05 Especificaciones Técnicas Del Equipo Médico ... - ParsaludZulma QuispeAún no hay calificaciones

- Artículo Docente Temporización Mediante SysTick ARM Cortex-MDocumento7 páginasArtículo Docente Temporización Mediante SysTick ARM Cortex-Mmax51sAún no hay calificaciones

- FTTXDocumento8 páginasFTTXRANCEL WALDEIR GUARNIZO CRUZAún no hay calificaciones

- 3.-Normas APADocumento16 páginas3.-Normas APATareas Online MaracayAún no hay calificaciones

- Autenticacion en MD5 OSPFDocumento11 páginasAutenticacion en MD5 OSPFCarlos Jesus Koo LabrinAún no hay calificaciones

- PROYECTO DE INVESTIGACION Cuidado de Las TicsDocumento78 páginasPROYECTO DE INVESTIGACION Cuidado de Las TicsWendy Jaclinz Zambrano YbanaAún no hay calificaciones

- Informe # - Adquisicion de Nivel de Ingeniero Automatico.Documento4 páginasInforme # - Adquisicion de Nivel de Ingeniero Automatico.Amilcar mamani anahuaAún no hay calificaciones

- Practico 1 InformaticaDocumento17 páginasPractico 1 InformaticaKevin FrancoAún no hay calificaciones

- Ejercicios Direccionamiento VSLM PDFDocumento2 páginasEjercicios Direccionamiento VSLM PDFMarcelo Alejandro Ramírez GonzálezAún no hay calificaciones

- PlantillaDocumento10 páginasPlantillamilenaAún no hay calificaciones

- 2.2.2.4 Packet Tracer - Configuring IPv4 Static and Default Routes Instructions PDFDocumento4 páginas2.2.2.4 Packet Tracer - Configuring IPv4 Static and Default Routes Instructions PDFIPCC UIOAún no hay calificaciones

- Lina Gutierrez Entregable 3Documento17 páginasLina Gutierrez Entregable 3Lina G25% (4)

- Módulo 3 - Instalador de Fibra OpticaDocumento45 páginasMódulo 3 - Instalador de Fibra OpticaGUILLE LOBOAún no hay calificaciones

- 3.3 Guia Basica Del Programa Mecanet AccesibleDocumento8 páginas3.3 Guia Basica Del Programa Mecanet AccesibleluzAún no hay calificaciones

- Cuarta Generación de ComputadorasDocumento3 páginasCuarta Generación de ComputadorasGerman Linares OlánAún no hay calificaciones

- Capacitacion GpsDocumento8 páginasCapacitacion GpsING Nestor ValeroAún no hay calificaciones

- Exposición de ContabilidadDocumento13 páginasExposición de Contabilidadsantos armendaAún no hay calificaciones

- Informe de La Entidad Ejecutora Producto Nº1: Ing. Yendrhit Estefany Pinto LotoreDocumento4 páginasInforme de La Entidad Ejecutora Producto Nº1: Ing. Yendrhit Estefany Pinto LotoreDorman JordanAún no hay calificaciones

- Actividad Sistemas 2Documento1 páginaActividad Sistemas 2Dejan-ZpardeAún no hay calificaciones