Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Ramirez Brandon SD Prep P6 GR7-2

Cargado por

brandon ramirezDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Ramirez Brandon SD Prep P6 GR7-2

Cargado por

brandon ramirezCopyright:

Formatos disponibles

Preparatorio Practica N°7: DISEÑO

COMBINACIONAL

(Enero de 2021)

1st Brandon Josue Ramirez Lema

Ingeniería Eléctrica y Electrónica, Escuela Politécnica Nacional

Sistemas Digitales

Quito, Ecuador

brandon.ramirez@epn.edu.ec

Resumen – El presente documento contiene información sobre

algunos diseños combinacionales mediante el uso de circuitos

integrados y compuertas lógicas and, or, not (A-O-N).

Índice de Términos – Circuito, Compuertas, Integrado, Tabla de Ilustración 1: Proceso de diseño lógico

verdad.

II. METODOLOGÍA

I. INTRODUCCIÓN

Para la elaboración del presente preparatorio de hará uso de hoja

guía de laboratorio de sistemas digitales practica 7, donde se

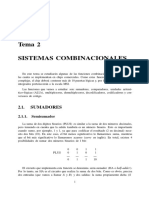

E n el proceso general de diseño de un sistema lógico se detallará cada pregunta planteada, mediante la investigación y

simulación de circuitos integrados mediante el software de

pueden identificar las siguientes fases: simulación de circuitos Proteus 8.

Fase 1 (Especificación): Aquí es donde comienzas. contiene

una descripción del comportamiento Lógica requerida en

III. DESARROLLO DE CONTENIDO

lenguaje natural. Si el problema a resolver no está claramente

planteado, puede que no sea posible Resoluble, de lo contrario 3.1 Consultar las características, tablas de función y

el resultado no será el esperado. Problema especificado distribución de pines de los circuitos integrados:

incorrectamente Cuando ningún proceso de diseño defectuoso − 7480

da como resultado resultados diferentes a los esperados. Este circuito integrado es un sumador binario completo de 1 bit,

Fase 2 (Modelado): Es un proceso de formalización que permite con compuertas complementarias a la entrada, suma

construir una representación formal del comportamiento En complementaria a la salida y Carry invertido a la salida. Está

algún lenguaje formal apropiado, forme un modelo de sistema. diseñado para media y alta velocidad. El circuito es enteramente

hay diferentes tipos Un modelo de comportamiento del sistema. compatible con las familias lógicas DTL y TTl.

En correspondencia con esto también hay varios Metodología

de diseño.

Fase 3 (Optimización (opcional)): Por lo general, las metas se

basan en algún tipo de criterio (costo, velocidad, fiabilidad,

etc.). De esta forma, se puede obtener un modelo optimizado

según el criterio usar. De hecho, la optimización no es

independiente de la tecnología que se empleará implementar.

Por ejemplo, si el sistema es combinatorio y se implementará

mediante puertas Se aplica la lógica y el criterio de Karnaugh,

el modelo de optimización será la expresión algebraica más Ilustración 2: Circuito Integrado 7480

pequeña por ese estándar. Por otro lado, si será implementado − 7482

por un multiplexor, los criterios pueden ser Para reducir el El circuito integrado 7482, es un sumador completo. Se

número de canales requeridos, la optimización del modelo caracteriza por que realiza la suma de dos números binarios de

puede ser una Mapa de Karnaugh relacionado con la tabla de 2 bits cada uno. Las salidas muestran la suma de cada bit,

verdad, vea cómo es conveniente usarlo Multiplexor, ya que además consta de un carry que se obtiene del segundo bit.

para este tipo de implementación no se utilizan expresiones

algebraicas.

Fase 4 (Síntesis): en esta etapa se realiza la implementación

física del modelo optimizado. [1]

LABORATORIO DE SISTEMAS DIGITALES, Preparatorio 7

Ilustración 6: Circuito Integrado 74283

3.2 Consultar las características, tabla de función y

distribución de pines de los circuitos integrados

− 74181

Este circuito integrado es una unidad lógica aritmética de 4 bits

(ALU). El cual permite 16 operaciones aritméticas, y 16

operaciones lógicas de dos variables como: AND, NAND, OR,

Ilustración 3: Circuito Integrado 7482 NOR.

− 7483

Es un sumador completo. Se caracteriza por que realiza la suma

de dos números binarios de 4 bits cada uno. Las salidas

muestran la suma de cada bit, además consta de un carry que se

obtiene del segundo bit. Esta funciona con lógica positiva o

negativa.

Ilustración 4: Circuito Integrado 7483

− 74183

Este circuito integrado es un sumador completo que tiene salida

de Carry individual, lo que le permite usar entradas múltiples.

Estos circuitos utilizan lógica de transistor a transistor de alta

velocidad. Las series 74 y 74LS están hechas para operar en

temperaturas desde los 0 a 70 C.

Ilustración 7: Circuito Integrado 74181

− 74381/ 74382

Ambos circuitos integrados son Schottky de baja potencia y

unidades lógicas aritméticas (ALU), ejecuta 8 operaciones

aritméticas/lógicas binarias en dos entradas de 4 bits. Una de

sus características mas destacadas es que las variables lógicas

XOR, AND y OR de dos variables booleanas son

proporcionadas sin circuitería externa.

Ilustración 5: Circuito Integrado 74183

− 74283

Su funcionamiento es casi similar al anterior, cada salida de la

suma va acompañada de su carry. El sumador lógico esta

implementado en forma verdadera, lo que significa que el carry

final puede ser realizado sin la necesidad de invertir la lógica.

LABORATORIO DE SISTEMAS DIGITALES, Preparatorio 7

y de los displays hexadecimales TIL. Compare estos dos tipos

de displays, presentar ventajas y desventajas

− Display 7 segmentos

Es un elemento utilizado en dispositivos electrónicos para

mostrar números y letras, cada segmento está hecho de material

luminoso, la organización o designación de estos segmentos se

muestra en la siguiente figura.

Ilustración 11: Caracteres

Ilustración 8: Integrado 74381/74382 Existen dos tipos de displays de 7 segmentos, la principal

diferencia entre ellos es la conexión de los pines asociados a los

segmentos, estos dos tipos se denominan ánodo común y cátodo

común.

Pantalla de cátodo común: Una pantalla de cátodo común es

aquella en la que el pin común está conectado al polo negativo

del LED (cátodo). Esto significa que este tipo de pantalla se

"acciona" con un "1" lógico o un voltaje positivo.

Ilustración 9: Distribución de pines

Ilustración 12: Cátodo Común

Pantalla de ánodo común: Una pantalla de ánodo común es

aquella cuyos ánodos están conectados al mismo punto. Este

tipo de visualización está controlada por cero (0). [3]

Ilustración 13: Ánodo Común

− Display hexadecimales TIL

El circuito integrado TIL 311 es un Display hexadecimal que

contiene 4 líneas de entradas de datos binarios, un circuito

lógico combinacional que convierte un código binario a

hexadecimal.

Ilustración 10: Tabla de la función

3.3 Consulte el funcionamiento y distribución de pines de

los displays de 7 segmentos (tanto ánodo como cátodo común)

LABORATORIO DE SISTEMAS DIGITALES, Preparatorio 7

10 0 1 0 1 0 1

11 0 1 0 1 1 1

12 0 1 1 0 0 1

13 0 1 1 0 1 1

14 0 1 1 1 0 1

15 0 1 1 1 1 1

16 1 0 0 0 0 1

17 1 0 0 0 1 1

18 1 0 0 1 0 1

19 1 0 0 1 1 X

Ilustración 14: Distribución de pines TIL 311 20 1 0 1 0 0 X

21 1 0 1 0 1 X

Display Ventajas Desventajas

22 1 0 1 1 0 X

7 segmentos Cuenta con dos No representa de 23 1 0 1 1 1 X

tipos de entradas una manera 24 1 1 0 0 0 X

cátodo común y optima los 25 1 1 0 0 1 X

ánodo común, lo valores superiores 26 1 1 0 1 0 X

que nos permite al 9. 27 1 1 0 1 1 X

trabajar tanto en 28 1 1 1 0 0 X

alto como en 29 1 1 1 0 1 X

bajo. 30 1 1 1 1 0 X

Hexadecimal Se puede usar Al manejar 31 1 1 1 1 1 X

TIL tanto como un caracteres Tabla 1: EJ 3.4

convertidor de hexadecimales, Usando mapa de Karnaugh tenemos:

binario a este no es muy AB\CDE 000 001 011 010 110 111 101 100

hexadecimal. común para 00 0 0 0 0 0 0 0 0

Al ser aquellos que 01 0 0 1 1 1 1 1 1

hexadecimal la recién aprendan 11 X X X X X X X X

lectura llega a ser binario. 10 1 1 X 1 X X X X

mas amigable Tabla 2: Mapa Karnaugh EJ 3.4

AB\CDE 000 001 011 010 110 111 101 100

3.4 Usando Sumadores Binarios de Cuatro Bits y los 00 0 0 0 0 0 0 0 0

01 0 0 1 1 1 1 1 1

módulos que se consideren necesarios, diseñe un sumador de

11 X X X X X X X X

dígitos decimales en código BCD. Este sumador acepta como 10 1 1 X 1 X X X X

entrada nueve bits que representa dos dígitos BCD más un Tabla 3: Agrupación

acarreo de la etapa anterior. El sumador generará como salida AB\CDE 000 001 011 010 110 111 101 100

dos dígitos BCD (decenas y unidades) los cuales serán 00 0 0 0 0 0 0 0 0

representados utilizando displays de 7 segmentos. Utilice el 01 0 0 1 1 1 1 1 1

circuito 7483 consultado en el numeral 3.1. 11 X X X X X X X X

10 1 1 X 1 X X X X

Para el diseño usando el circuito integrado 74181, primero Tabla 4: Agrupación II

conocemos los valores que este nos brindará, arrojando un AB\CDE 000 001 011 010 110 111 101 100

00 0 0 0 0 0 0 0 0

numero binario sumado de 5 bits donde uno de ellos

01 0 0 1 1 1 1 1 1

representará el acarreo, ahora bien, con esto podemos plantear 11 X X X X X X X X

la siguiente tabla de verdad, considerando que el número 10 1 1 X 1 X X X X

máximo representado en bcd en conjunto con su acarreo será el Tabla 5: Agrupación III

18, ya que a partir del 9 este tendrá que sumar 6 para reiniciar Donde podemos obtener:

el numero de bits. 𝑌0 = 𝐵𝐷 + 𝐵𝐶 + 𝐴

ENTRADA SALIDA

m C4 A B C D Y0

0 0 0 0 0 0 0

1 0 0 0 0 1 0

2 0 0 0 1 0 0

3 0 0 0 1 1 0

4 0 0 1 0 0 0 Ilustración 15: Circuito Implementado

5 0 0 1 0 1 0

6 0 0 1 1 0 0 3.5 Diseñar un circuito sumador-restador de dos números

7 0 0 1 1 1 0

de cuatro bits en complemento A-2. El circuito debe utilizar un

8 0 1 0 0 0 0

9 0 1 0 0 1 0 único integrado 74181 y la función del circuito cambiará

LABORATORIO DE SISTEMAS DIGITALES, Preparatorio 7

dependiendo del bit de entrada X. Si X=1 el circuito será el integrado 74LS85 el cual, mediante su comportamiento,

sumador y si X=0 el circuito será restador. comparar las dos entradas y arrojara 1 cuando la entrada

sea verdadera en su comparación, a parte se usara un

Para el diseño del circuito, usaremos el integrado 74LS181, multiplexor 4019 el cual ingresa 2 entradas de 4 bits, dos

donde este necesitara de dos entradas de cuatro bits, y entradas selectoras y arrojara el bit que cumpla con la

dependiendo de su configuración actuara en distinta manera por función a seleccionar, el cual ingresaremos al Display 7

lo que si observamos la tabla de funciones que este permite Segmentos.

ocuparemos:

− Restador

Para poder configurar el circuito restador usaremos un

integrado 74LS181 el cual mediante su configuración igual

al anterior circuito actuara como un restador, el cual de

acuerdo al caso arrojara el resultado con signo + o signo –

el que será visto por un led, recordando que cuando el

numero resultante sea negativo arrojara el numero en

complemento 2, el cual si negamos y sumamos uno

tendremos el valor convertido en positivo antepuesto por

signo, de igual manera que en el circuito comparador

usaremos un multiplexor 4019 el que arrojara la salida que

cumpla con la condición del carry que contenga 0.

Ilustración 16: Tabla de funciones 74LS181

− Sumador

Para que este actúe como sumador necesitamos que Cn=H,

las entradas S3, S2, S1 y S0 sean H, L, L, H

respectivamente.

− Restador

Para que este actúe como sumador necesitamos que Cn=L,

las entradas S3, S2, S1 y S0 sean L, H, H, L

respectivamente.

Ilustración 18: Circuito Implementado

Ilustración 17: Circuito Implementado

3.6 Diseñar un circuito lógico que disponga de dos entradas

(A, B) cada una de las cuales recibe un número de un digito

codificado en BCD, y una entrada de selección (S), de manera Ilustración 19: Circuito Implementado

que cuando la entrada S=0 en la salida (Y) aparezca el número

mayor entre A y B, y que cuando S=1, en la salida (Y) se REFERENCIAS

muestre el resultado de A–B, el signo del resultado debe [1] Universidad Nacional de Rosario, "DISEÑO COMBINACIONAL",

mostrarse por medio de un led, el resultado debe aparecer en DISEÑO COMBINACIONAL, Rosario, Argentina. Accedido el 15 de

displays. enero de 2022. [En línea]. Disponible:

https://www.dsi.fceia.unr.edu.ar/downloads/digital_I/DiseñoCombinacio

nal_24-03-11.pdf

Para poder realizar el diseño del circuito separaremos en dos [2] Alldatasheet.com. "ALLDATASHEET.COM - Datasheet search site for

partes y analizaremos su funcionamiento. Electronic Components and Semiconductors and other semiconductors".

− Comparador ALLDATASHEET.COM - Datasheet search site for Electronic

Components and Semiconductors and other semiconductors.

Para que el circuito actúe como un comparador usaremos https://www.alldatasheet.com (acedido el 16 de enero de 2022).

LABORATORIO DE SISTEMAS DIGITALES, Preparatorio 7

[3] "Conectar display 7 segmentos | CodigoElectronica". Inicio |

CódigoElectrónica. http://codigoelectronica.com/blog/conectar-display-

7-segmentos (accedido el 16 de enero de 2022).

[4] S. Azuero, "Construcción de un tablero electrónico para demostración de

circuitos digitales combinacionales y secuenciales", Proyecto previo a la

obtención del título, ESCUELA POLITECNICA NACIONAL, Quito,

2010. [En línea]. Disponible:

https://bibdigital.epn.edu.ec/bitstream/15000/2287/1/CD-2997.pdf

LABORATORIO DE SISTEMAS DIGITALES, Preparatorio 7

También podría gustarte

- Jesica Santibañez Control5Documento8 páginasJesica Santibañez Control5Jesica Santibañez100% (1)

- Proyecto Tic Tac ToeDocumento2 páginasProyecto Tic Tac ToeBryanAún no hay calificaciones

- Practica 5Documento10 páginasPractica 5Diana ObandoAún no hay calificaciones

- Operaciones Aritmeticas BinariasDocumento8 páginasOperaciones Aritmeticas BinariasAndres Vega100% (1)

- A e 1 098 Fernando Pita AlbiacDocumento29 páginasA e 1 098 Fernando Pita AlbiacbenedictAún no hay calificaciones

- Ramirez Brandon Lagos Andrew SD Inf P6 GR7-2Documento5 páginasRamirez Brandon Lagos Andrew SD Inf P6 GR7-2brandon ramirezAún no hay calificaciones

- Informe 5Documento2 páginasInforme 5patuchinmhAún no hay calificaciones

- Informe 2Documento2 páginasInforme 2HECTOR JULIAN SANTACRUZ GUTIERREZAún no hay calificaciones

- Laboratorio Numeros BinariosDocumento12 páginasLaboratorio Numeros BinariosFrancisco GonzalezAún no hay calificaciones

- Laboratorio 2 PDFDocumento1 páginaLaboratorio 2 PDFAndrés RoseroAún no hay calificaciones

- Comparador de 4 BitsDocumento9 páginasComparador de 4 BitsJames Alexander Lara BetancourtAún no hay calificaciones

- Preparatorio 6Documento14 páginasPreparatorio 6Luis LoayzaAún no hay calificaciones

- Lab CD PRACTICA4Documento10 páginasLab CD PRACTICA4Faviola de SadaAún no hay calificaciones

- Informe de Laboratorio Electronica DigitalDocumento7 páginasInforme de Laboratorio Electronica Digitalsebastian bustamanteAún no hay calificaciones

- SumadorDocumento5 páginasSumadorMago RuAún no hay calificaciones

- Prácticas de Laboratorio p5Documento6 páginasPrácticas de Laboratorio p5Guillo YeroviAún no hay calificaciones

- Informe Final ALU Laboratorio Circuitos Digitales IDocumento31 páginasInforme Final ALU Laboratorio Circuitos Digitales ICarlosVillavicencioGAún no hay calificaciones

- Práctica 4 Circuitos DigitalesDocumento5 páginasPráctica 4 Circuitos DigitalesEfrén Alessandro Cremonini CasadiegoAún no hay calificaciones

- DECODIFICADORDocumento5 páginasDECODIFICADORAlejandro GonzalezAún no hay calificaciones

- Practica 4 - EDDocumento10 páginasPractica 4 - EDValeria_13Aún no hay calificaciones

- Lab 3. Decodificadores, Sumadores y Reloj DigitalDocumento8 páginasLab 3. Decodificadores, Sumadores y Reloj DigitalSOFIA ARAGON JURADOAún no hay calificaciones

- MultisimDocumento13 páginasMultisimjosersAún no hay calificaciones

- Lab Algebra de BooleDocumento6 páginasLab Algebra de BooleElias LadinoAún no hay calificaciones

- Informe 2 Digitales Desktop t3kqcmnDocumento18 páginasInforme 2 Digitales Desktop t3kqcmnROGER STEVEEN ARMAS SIMBA�AAún no hay calificaciones

- Inf - Lab. - 5 Circuitos MSIDocumento7 páginasInf - Lab. - 5 Circuitos MSILazaro BaldiviezoAún no hay calificaciones

- SD GR12 Cueva Prieto Informe 8Documento5 páginasSD GR12 Cueva Prieto Informe 8Jose CuevaAún no hay calificaciones

- Diseño de Circuitos Lógicos CombinacionalesDocumento6 páginasDiseño de Circuitos Lógicos CombinacionalesPEDRO DAVID PESANTEZ PESANTEZAún no hay calificaciones

- Practica #5 SistemasDocumento17 páginasPractica #5 SistemasIlse Cortés LunaAún no hay calificaciones

- ED Practica 1 Electrónica DigitalDocumento15 páginasED Practica 1 Electrónica DigitalAlexandre Pérez ReinaAún no hay calificaciones

- INFORME4511Documento2 páginasINFORME4511JOSE MANUEL BENAVIDES GUTIERREZAún no hay calificaciones

- Análisis Combinatorio de Circuitos DigitalesDocumento13 páginasAnálisis Combinatorio de Circuitos DigitalesSebas R.Aún no hay calificaciones

- Preparatorio 9 Sistemas DigitalesDocumento11 páginasPreparatorio 9 Sistemas DigitalesJuanCarlos JCAún no hay calificaciones

- Informe 1 Electronica DigitalDocumento13 páginasInforme 1 Electronica DigitalFelipe BeltranAún no hay calificaciones

- Laboratorio 2Documento2 páginasLaboratorio 2Andres TasconAún no hay calificaciones

- Tarea3 ParteColaborativa MaritzaPaola MurciaPulidoDocumento3 páginasTarea3 ParteColaborativa MaritzaPaola MurciaPulidoWilliam GilAún no hay calificaciones

- I1reporte Del DisplayDocumento15 páginasI1reporte Del DisplayLol KelAún no hay calificaciones

- ETD - Práctica 3 - 22 - 23Documento7 páginasETD - Práctica 3 - 22 - 23Mati RomeroAún no hay calificaciones

- Laboratorio #4Documento5 páginasLaboratorio #4A jugar yaAún no hay calificaciones

- LM555Documento7 páginasLM555Steven JosueAún no hay calificaciones

- Zair Simon ReyesDocumento10 páginasZair Simon ReyesPedro Landa ZamoraAún no hay calificaciones

- Lab3 Compuertas LoÌ GicasDocumento7 páginasLab3 Compuertas LoÌ GicasRomeo AriasAún no hay calificaciones

- FGL029 Guia No 2 Arquitecturas VHDLDocumento13 páginasFGL029 Guia No 2 Arquitecturas VHDLAlbeiroFernandezSanchezAún no hay calificaciones

- Informe 6Documento12 páginasInforme 6Daniel WilliamsAún no hay calificaciones

- Informe 1 de Laboratorio - Compuertas LogicasDocumento48 páginasInforme 1 de Laboratorio - Compuertas LogicasJhon Ramiro MuñozAún no hay calificaciones

- Practica 6Documento5 páginasPractica 6JokerTHAún no hay calificaciones

- Manual de SistemasDocumento46 páginasManual de SistemasvictorAún no hay calificaciones

- Informe 3 Circuitos LogicosDocumento6 páginasInforme 3 Circuitos LogicosSofia PinoAún no hay calificaciones

- Programacion de Circuitos Combinacionales Con HDLDocumento19 páginasProgramacion de Circuitos Combinacionales Con HDLTaz Hernandez DeAún no hay calificaciones

- Sumador-Restador DigitalDocumento4 páginasSumador-Restador DigitalFULVIO ANDRES PEDRAZA CAMONAAún no hay calificaciones

- Practica 3Documento8 páginasPractica 3Sebastian MayorgaAún no hay calificaciones

- CalculadoraDocumento6 páginasCalculadorajuanAún no hay calificaciones

- Semaforo BinarioDocumento10 páginasSemaforo BinarioSUAREZ TORRES ANDREA ALEJANDRAAún no hay calificaciones

- Electronica DigitalDocumento7 páginasElectronica DigitalGilson Daniel MaloAún no hay calificaciones

- Guía de Práctica-Semana2Documento6 páginasGuía de Práctica-Semana2CRISTIAN JHONATAN ZARATE YAURIAún no hay calificaciones

- Lab N°3 Microelectrónica (1161481-1161167)Documento11 páginasLab N°3 Microelectrónica (1161481-1161167)Julian MolinaAún no hay calificaciones

- CIdigitales Sabatino DanielFDocumento9 páginasCIdigitales Sabatino DanielFDavid FernandezAún no hay calificaciones

- Prepar A To Rio 7 Digital EsDocumento12 páginasPrepar A To Rio 7 Digital EsDanilo CalvachiAún no hay calificaciones

- 4 Proyecto Final (Borrador)Documento12 páginas4 Proyecto Final (Borrador)Wilmer SosaAún no hay calificaciones

- INFORME2Documento9 páginasINFORME2Ricardo RomeroAún no hay calificaciones

- Electronica Digital Pre Tarea (Fase 0 - Actividad de Presaberes)Documento11 páginasElectronica Digital Pre Tarea (Fase 0 - Actividad de Presaberes)Top Games X100% (1)

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208De EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208Aún no hay calificaciones

- Reparación de instalaciones automatizadas. ELEE0109De EverandReparación de instalaciones automatizadas. ELEE0109Aún no hay calificaciones

- Ramirez Brandon Lagos Andrew SD Inf P5 GR7-2Documento4 páginasRamirez Brandon Lagos Andrew SD Inf P5 GR7-2brandon ramirezAún no hay calificaciones

- Ramirez Brandon SD Prep P5 GR7-2Documento9 páginasRamirez Brandon SD Prep P5 GR7-2brandon ramirezAún no hay calificaciones

- Ramirez Brandon SD Inf P4 GR7-2Documento4 páginasRamirez Brandon SD Inf P4 GR7-2brandon ramirezAún no hay calificaciones

- Ramirez Brandon SD Prep P4 GR7-2Documento5 páginasRamirez Brandon SD Prep P4 GR7-2brandon ramirezAún no hay calificaciones

- Ramirez SD Inf P3 GR7-2Documento5 páginasRamirez SD Inf P3 GR7-2brandon ramirezAún no hay calificaciones

- Ramirez SD Prep P3 GR7-2Documento3 páginasRamirez SD Prep P3 GR7-2brandon ramirezAún no hay calificaciones

- Ramirez SD Inf P2 GR7-2Documento5 páginasRamirez SD Inf P2 GR7-2brandon ramirezAún no hay calificaciones

- Ramirez SD Prep P2 GR7-2Documento2 páginasRamirez SD Prep P2 GR7-2brandon ramirezAún no hay calificaciones

- Ramirez SD Prep P1 GR7-2Documento2 páginasRamirez SD Prep P1 GR7-2brandon ramirezAún no hay calificaciones

- Ramirez SD Inf P1 GR7-2Documento3 páginasRamirez SD Inf P1 GR7-2brandon ramirezAún no hay calificaciones

- Circuitos Aritméticos 5Documento14 páginasCircuitos Aritméticos 5John QueralesAún no hay calificaciones

- Arquitectura de Microprocesadores - CalculadoraDocumento21 páginasArquitectura de Microprocesadores - CalculadoraalAún no hay calificaciones

- Lab AluDocumento45 páginasLab AluRaymond BautistaAún no hay calificaciones

- Alu 74181Documento8 páginasAlu 74181Edna Rosario Puente MartinezAún no hay calificaciones

- Practica ALUDocumento9 páginasPractica ALUJosué Ríos SilvaAún no hay calificaciones

- Alu 74181Documento10 páginasAlu 74181Carlos AlbertoAún no hay calificaciones

- Alu 74181Documento9 páginasAlu 74181Franck JonhsonAún no hay calificaciones

- Diseño de Circuitos Combinacionales en VHDLDocumento6 páginasDiseño de Circuitos Combinacionales en VHDLPablo PulacheAún no hay calificaciones

- Preparatorio 6bienDocumento12 páginasPreparatorio 6bienAlejandro CentenoAún no hay calificaciones

- Alu 74181Documento2 páginasAlu 74181Jonatan GomezAún no hay calificaciones

- Tema 2 - Sistemas CombinacionalesDocumento31 páginasTema 2 - Sistemas CombinacionalesAlvaro VerduguezAún no hay calificaciones

- 04.implementacion de Un Sumador CompletoDocumento11 páginas04.implementacion de Un Sumador Completojesus antonioAún no hay calificaciones

- Informe 2 Digital LLDocumento6 páginasInforme 2 Digital LLDavid CortezAún no hay calificaciones

- Alu 74LS181Documento3 páginasAlu 74LS181jonat09Aún no hay calificaciones

- Prepa 6Documento9 páginasPrepa 6Daniel OrbeAún no hay calificaciones