Documentos de Académico

Documentos de Profesional

Documentos de Cultura

APCap 16

APCap 16

Cargado por

Nicolau ManuelTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

APCap 16

APCap 16

Cargado por

Nicolau ManuelCopyright:

Formatos disponibles

Ins. Ind. Luis A.

Huergo

Departamento de Telecomunicaciones

Codificadores 16

introduccion

Los codificadores son los dispositivos encargados de la codificación. El concepto

de codificación, tal y como se exploró en la sección de Códigos, está vinculado a la

“traducción” de un código a otro.

Los codificadores pueden implementarse a partir de la aplicación de diagramas de

Karnaugh comparando las tablas de verdad. También existen codificadores inte-

grados de diferentes características.

Tienen dos tipos de entradas: de control y de datos. La Ilustración 16.1 muestra un

diagrama de un codificador. Las entradas de datos son las que componen el código

a “traducir”. Las entradas de control por su parte pueden ser de selección, las cuales

se emplean en la codificación, y de habilitación, que existen en muchos tipos de

integrados, y se encargan de permitir o no el proceso de trabajo.

Codificador

Datos Datos

Control

SelecciónH abilitación

Ilustración 16.1: Diagrama de un codificador genérico

Aplicación a teclados alfanuméricos.

Un teclado alfanumérico se caracteriza, en términos de lógica de circuitos, por ge-

nerar un código Johnson de tantos bits como teclas existan, y convertirlos en una

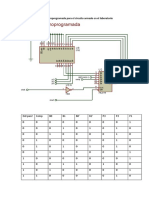

salida binaria. Los codificadores comerciales muestran una tabla de verdad con el

código de prioridad y las respectivas salidas binarias. La relación entradas – salidas

es: para N salidas binarias, existen 2N entradas. En la Ilustración 16.2, se muestra la

tabla de verdad de un codificador CMOS de 8 Bits comercial.

Input Output

Ei D7 D6 D5 D4 D3 D2 D1 D0 GS Q2 Q1 Q0 Eo

0 × × × × × × × × 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0 0 0 0 1

1 1 × × × × × × × 1 1 1 1 0

1 0 1 × × × × × × 1 1 1 0 0

1 0 0 1 × × × × × 1 1 0 1 0

1 0 0 0 1 × × × × 1 1 0 0 0

1 0 0 0 0 1 × × × 1 0 1 1 0

1 0 0 0 0 0 1 × × 1 0 1 0 0

1 0 0 0 0 0 0 1 × 1 0 0 1 0

1 0 0 0 0 0 0 0 1 1 0 0 0 0

PINOUT D7 Q2

priority encoder Q1

selector Q0

1 16

D0

Eo

2 15

3 14

Ei GS

4532

4 13

5 12

6 11

Ilustración 16.2: CD4532B Diagrama en bloques, y Tabla de verdad. (Fuente: Texas Instruments).

7 10

8 9

Las entradas D7 a D0 pueden corresponder a los botones del teclado. Cuando se de-

1-D4 16-Vdd

sea multiplicar la cantidad de botones pueden conectarse codificadores en cascada

2-D5 15-E0

respetando la relación entradas – salidas (Ilustración 16.3).

3-D6 14-Gs

4-D7 13-D3

Ei´

5-Ei 12-D2

6-Q2 11-D1 5 Ei GS 14

4 d7

7-Q1 10-D0 D15

3 Q2 6

Q3´

2 7

8-Vss 9-Q0 Q1

4532

1 4071

13 Q0 9

12

10 Do Eo 15 Qs´

D8

Q2´

5 Ei GS 14

4d 7 6 Q1´

D7 Q2

3

2 Q1 7

4532

1

13 Q0 9 Q0´

12

10 Do Eo 15

D0 Eo´

Ilustración 16.3: CD4532B Conexión en cascada. (Fuente: Texas Instruments).

Las salidas Q son normalmente conectadas a un microcontrolador que interpreta

el valor alfanumérico, o enviadas a un codificador paralelo – serie para ser trans-

mitido como dato a alguna terminal.

Ins. Ind. Luis A. Huergo

Departamento de Telecomunicaciones

Codificador paralelo – serie.

Cuando se envían datos a un módulo de transmisión (Tx) (por ejemplo, un opto-

transistor, o un módulo de radiofrecuencia) se lo hace a través de un único cable

que contiene toda la información. Por esto, la información en paralelo que se

construye al sintetizar un teclado, debe nuevamente codificarse para poder ser

transmitida.

Los codificadores paralelo – serie, están constituidos por varias etapas. Básica-

mente, un oscilador, un contador, un sincronizador, y lógicas de habilitación.

Existen formas sencillas de implementarlos a través del uso de Flip Flops mediante

registros de desplazamientos. También existen codificadores integrados como

los que se muestran en la Ilustración 16.4. Este tipo de integrados suele contener,

adicionalmente, entradas de direccionamiento que permiten construir diferentes

dispositivos y controlarlos con uno único. En otras palabras, con un único módulo

codificador, puedo controlar muchos módulos decodificadores.

Vdd

Transmitter Circuit

Vdd

1 A0 Vdd 18

8050

2 A1 Dout 17 1 A0 Vdd 18

3 A2 ×1 16 2 A1 Dout 17

100pF Rosc

3 A2 osc1 16

455Kh

4 A3 ×2 15 100pF 4 A3 osc2 15

5 A4 L/MB 14 5 A4 TE 14

6 A5 D11 13 6 A5 AD11 13

7 A6 D10 12 7 A6 AD10 12

8 A7 D9 11 8 A7 AD9 11

9 Vss D8 10 9 Vss AD8 10

HT12A HT12E

Ilustración 16.4: HT12A/E PINOUT y Diagrama de conexión. (Fuente: Holtek).

El decodificador, no es otra cosa, que otro codificador. Si se trata de convertidores

paralelo – serie, el decodificador propio será un convertidor serie – paralelo.

Existen ciertos cuidados que hay que tener a la hora de implementar un sistema

codificador/decodificador. Los principales problemas aparecen en la sincroni-

zación de las frecuencias de reloj que de no estar correctamente establecidas, la

“traducción” no podrá realizarse correctamente. Otro inconveniente suele aparecer

en los niveles de tensión: Las normas propias de la familia lógica deben ser respe-

tadas pudiendo ocasionar, en caso contrario, la falta de interpretación del decodifi-

cador o la destrucción del mismo.

En la Ilustración 16.5, se muestra un decodificador comercial complementario a los

de la Ilustración 16.4.

Receiver Circuit

Vdd

1 A0 Vdd 18

2 A1 VT 17

3 A2 16 Rosc

osc1

4 A3 osc2 15

5 A4 Din 14

6 A5 D11 13

7 A6 D10 12

8 A7 D9 11

9 Vss D8 10

HT12D

Ilustración 16.5: HT12D PINOUT y Diagrama de conexión. (Fuente: Holtek).

Aplicación a control remoto.

Con los conceptos brevemente resumidos puede fácilmente extrapolarse la confi-

guración necesaria para la construcción de un control remoto o control a distancia.

En la Ilustración 16.6, puede verse un diagrama en bloques de un control remoto y

un módulo controlado por el mismo.

Periférico de Codificador TX RX Periférico de Codificador

entrada paralelo serie entrada salida

Ilustración 16.6: Diagrama en bloques de un sistema controlado a distancia.

En la sección de Protocolos, podrán verse ejemplos de sistemas de control a distan-

cia que requieren un sincronismo especial, sin el cual, la comunicación se pier-

de. Asimismo, se verán formas de implementar módulos de comunicación en la

sección Recepción y Transmisión de Datos, y detalles de fabricación en la sección

“Nociones de diseño”.

También podría gustarte

- Problemas resueltos de Hidráulica de CanalesDe EverandProblemas resueltos de Hidráulica de CanalesCalificación: 4.5 de 5 estrellas4.5/5 (7)

- Evaluación Unidad 3Documento7 páginasEvaluación Unidad 3Keissy Rolon riveraAún no hay calificaciones

- Laboratorio y Enfermedad Casos Clinicos Volumen 4Documento400 páginasLaboratorio y Enfermedad Casos Clinicos Volumen 4lobwho480% (5)

- Practica 8 Multiplicador Binario PDFDocumento8 páginasPractica 8 Multiplicador Binario PDFJacob CisnerosAún no hay calificaciones

- Escarabajo o de OroDocumento4 páginasEscarabajo o de OroJose Luis Seclen NiñoAún no hay calificaciones

- Planificacion Estrategica SituacionalDocumento22 páginasPlanificacion Estrategica SituacionalPaola Masa100% (1)

- El Estudio de La MarchaDocumento17 páginasEl Estudio de La Marchaneftaliciouzzz100% (3)

- Tarea 4Documento11 páginasTarea 4yuri100% (2)

- SRNICEK - Capitalismo de PlataformasDocumento62 páginasSRNICEK - Capitalismo de Plataformasnlf2205100% (1)

- Feria de Ciencias Sistema SolarDocumento3 páginasFeria de Ciencias Sistema SolarYesica PedrozoAún no hay calificaciones

- Examen Parcial DigitalesDocumento4 páginasExamen Parcial DigitalesJose luisAún no hay calificaciones

- Guia-Introductoria - TinKerCad 2-2023Documento13 páginasGuia-Introductoria - TinKerCad 2-2023Gabriela Lourdes Rodríguez ParadaAún no hay calificaciones

- Bloques CombinacionalesDocumento5 páginasBloques CombinacionalesfedogonzalezAún no hay calificaciones

- Doble Conversor de Codigo-Canchis y Valverde (Autoguardado)Documento3 páginasDoble Conversor de Codigo-Canchis y Valverde (Autoguardado)Peoto VallelinAún no hay calificaciones

- Guia 2Documento19 páginasGuia 2Carlos del CampoAún no hay calificaciones

- Lab 3 Digital EsDocumento18 páginasLab 3 Digital EsEduardo GuevaraAún no hay calificaciones

- Lab Vega Diego 9952Documento12 páginasLab Vega Diego 9952Diego Sebastian Vega CastilloAún no hay calificaciones

- Regleta SixteenlineDocumento6 páginasRegleta SixteenlineLuis OrtegaAún no hay calificaciones

- Preinforme 2Documento6 páginasPreinforme 2HECTOR JULIAN SANTACRUZ GUTIERREZ100% (1)

- Guia 1 - PHA0Documento18 páginasGuia 1 - PHA0Pedro LeivaAún no hay calificaciones

- FCO Ene 2014 T1-5-SOLUCIONDocumento7 páginasFCO Ene 2014 T1-5-SOLUCIONAdri SsAún no hay calificaciones

- Circuitos Combinacionales (MSI)Documento34 páginasCircuitos Combinacionales (MSI)Nestor QuijadaAún no hay calificaciones

- AluDocumento12 páginasAluJuan David LeguizamonAún no hay calificaciones

- Lab2.2 Vega Diego 9952Documento14 páginasLab2.2 Vega Diego 9952Diego Sebastian Vega CastilloAún no hay calificaciones

- FlipflopsDocumento8 páginasFlipflopsDavid AckermanAún no hay calificaciones

- Informe PREVIO N°6 Sistemas DigitalesDocumento16 páginasInforme PREVIO N°6 Sistemas DigitalesDanielAún no hay calificaciones

- Examen CEDG Sept 2010Documento14 páginasExamen CEDG Sept 2010K-rim CuéllarAún no hay calificaciones

- Pre Examen Del Examen 2Documento6 páginasPre Examen Del Examen 2OrlandoAún no hay calificaciones

- Codif Deco Mux DemuxDocumento46 páginasCodif Deco Mux DemuxCarlos J. Yarleque RomeroAún no hay calificaciones

- Actividad 7Documento9 páginasActividad 7pruebaAún no hay calificaciones

- Resultado de Aprendizaje 2 PDFDocumento12 páginasResultado de Aprendizaje 2 PDFJordan Sosa VillegasAún no hay calificaciones

- Informe Previo Digitales 5Documento20 páginasInforme Previo Digitales 5Luis ReyesAún no hay calificaciones

- Informe - Diseño de Circuitos Digitales CombinacionalesDocumento5 páginasInforme - Diseño de Circuitos Digitales CombinacionalesRoberto Carlos Jacinto VelizAún no hay calificaciones

- Informe Practica 4 SDIIDocumento6 páginasInforme Practica 4 SDIIJuan Sebastian Mosquera BarahonaAún no hay calificaciones

- HT ED Semana 09 Grupo06Documento4 páginasHT ED Semana 09 Grupo06renzo romero valverdeAún no hay calificaciones

- Decodificador Binario A BCDDocumento5 páginasDecodificador Binario A BCDCarlos Daniell ValenciaAún no hay calificaciones

- MultiplexorDocumento14 páginasMultiplexorRicardo NeriAún no hay calificaciones

- Diceño de Funciones Combinacionales y Simulacion Con ProteusDocumento5 páginasDiceño de Funciones Combinacionales y Simulacion Con Proteusraul quispeAún no hay calificaciones

- Practica 8 Diseño DigitalDocumento7 páginasPractica 8 Diseño DigitalPandaAún no hay calificaciones

- Practica 1Documento9 páginasPractica 1narakuec_21@hotmail.com100% (1)

- Codificadores y DecodificadoresDocumento16 páginasCodificadores y DecodificadoresLucas MachucaAún no hay calificaciones

- Act6 Ed1Documento4 páginasAct6 Ed1KillSt4rtusAún no hay calificaciones

- Microprogramacion RomDocumento2 páginasMicroprogramacion RomEdilson Laura MercadoAún no hay calificaciones

- Solucionario Del Examen Parcial II de Electronic A DigitalDocumento5 páginasSolucionario Del Examen Parcial II de Electronic A Digitalsuperminded50% (2)

- RegistrosDocumento10 páginasRegistrosperuchoAún no hay calificaciones

- Comparto - CODIFICADOR DECODIFICADOR 16092021 - Con UstedDocumento20 páginasComparto - CODIFICADOR DECODIFICADOR 16092021 - Con UstedAdalid elaprendizAún no hay calificaciones

- MultiplexoresDocumento5 páginasMultiplexoresRodrigo Huaranca MoralesAún no hay calificaciones

- 6-Algoritmos MinimiDocumento33 páginas6-Algoritmos MinimiAlejandro Reyes SoquiAún no hay calificaciones

- Decodificadores y Demultiplexores Informe Circuitos DigitalesDocumento6 páginasDecodificadores y Demultiplexores Informe Circuitos DigitalesCarlos Silva EspinozaAún no hay calificaciones

- Codificadores Decodificadores Multiplexores DemultiplexoresDocumento32 páginasCodificadores Decodificadores Multiplexores DemultiplexoresPepeAún no hay calificaciones

- Actividad 2 Decodificador Binario A Hexadecimal Proyecto Parte2Documento12 páginasActividad 2 Decodificador Binario A Hexadecimal Proyecto Parte2Anthonyy CreativityAún no hay calificaciones

- CD1 Practica 4 Equipo 5Documento16 páginasCD1 Practica 4 Equipo 5Fernando EscobarAún no hay calificaciones

- MicrocontroladoresDocumento4 páginasMicrocontroladoresJC RTAún no hay calificaciones

- Dodificador y DecodificadorDocumento9 páginasDodificador y Decodificadorfreddy chuquimiaAún no hay calificaciones

- Grupo102016 141 Tarea1-PLE, ModelosDeTransporteyAsignaciónDocumento26 páginasGrupo102016 141 Tarea1-PLE, ModelosDeTransporteyAsignaciónCamilo GilAún no hay calificaciones

- Laboratorio 2 DecoderDocumento6 páginasLaboratorio 2 DecoderSergio AguilarAún no hay calificaciones

- Practica ED5 - Reyes, Salinas, Jaramillo C., Jaramillo ADocumento6 páginasPractica ED5 - Reyes, Salinas, Jaramillo C., Jaramillo ARAFAEL REYESAún no hay calificaciones

- Examen de RecuperacionDocumento3 páginasExamen de RecuperacionLuis AngelAún no hay calificaciones

- 3.clase N3-Elt2680Documento4 páginas3.clase N3-Elt2680Daniel Josè Montaño MonroyAún no hay calificaciones

- Sumador 4 BitsDocumento6 páginasSumador 4 BitsLuis Alejandro Conejo100% (1)

- P4SU Jowar y JeancarDocumento10 páginasP4SU Jowar y JeancarjowarAún no hay calificaciones

- Ejemp 3Documento4 páginasEjemp 3Moreno Reyes Eduardo MartinAún no hay calificaciones

- MODULO III Introduccion A Los Circuitos Integrados Andres Perdomo CI 28164082Documento23 páginasMODULO III Introduccion A Los Circuitos Integrados Andres Perdomo CI 28164082Julio PerdomoAún no hay calificaciones

- Trabajo Práctico N°6 Circuitos DigitalesDocumento20 páginasTrabajo Práctico N°6 Circuitos DigitalesALEXANDER LENIN VILLANUEVA BARRETOAún no hay calificaciones

- Unidad 4 2023Documento27 páginasUnidad 4 2023Leonardo Benavides RodasAún no hay calificaciones

- Módulos Combinacionales Básicos. Tema 7Documento27 páginasMódulos Combinacionales Básicos. Tema 7Julio Arpon MartinezAún no hay calificaciones

- Práctica #3 - Etn606Documento1 páginaPráctica #3 - Etn606juanAún no hay calificaciones

- Etn-606 Tarea N 2Documento12 páginasEtn-606 Tarea N 2juanAún no hay calificaciones

- Cajero PDFDocumento2 páginasCajero PDFjuanAún no hay calificaciones

- Maestria Marketing (LPZ)Documento6 páginasMaestria Marketing (LPZ)juanAún no hay calificaciones

- Diagnostico y Tratamiento de ArtrosisDocumento6 páginasDiagnostico y Tratamiento de ArtrosisMiguel FigueroaAún no hay calificaciones

- Ups ST003882Documento88 páginasUps ST003882Alfonso CevallosAún no hay calificaciones

- Informes de Practicas 1,2,4Documento49 páginasInformes de Practicas 1,2,4Luis Armando Bancayán SalazarAún no hay calificaciones

- ÁFRICA WordDocumento6 páginasÁFRICA WordRosember Cruz100% (1)

- Guion Teatral BachueDocumento4 páginasGuion Teatral BachueJessica Benavides50% (4)

- Acta Constitutiva Santa BarbaraDocumento12 páginasActa Constitutiva Santa BarbaraNuris AriasAún no hay calificaciones

- Estadisticas de Resultados de Saber 11 2011 Por Institucion y PruebaDocumento1296 páginasEstadisticas de Resultados de Saber 11 2011 Por Institucion y Pruebajulio david casseresAún no hay calificaciones

- Ensayo EstadisticaDocumento6 páginasEnsayo EstadisticaGerald VelasquezAún no hay calificaciones

- Sub1-A4 Naturaleza Del ConocimientoDocumento4 páginasSub1-A4 Naturaleza Del ConocimientoLuis CabreraAún no hay calificaciones

- Informe Wisc de Evaluación Psicológica J LDocumento5 páginasInforme Wisc de Evaluación Psicológica J LVianney MorontaAún no hay calificaciones

- Monólogo ProfesoraDocumento2 páginasMonólogo ProfesoraJavier Ricardo Rodríguez PinoAún no hay calificaciones

- Fanzine Anarquia I AlcoholDocumento12 páginasFanzine Anarquia I AlcoholEva Ruiz RubioAún no hay calificaciones

- Resumen 5 CuartillasDocumento6 páginasResumen 5 CuartillasJonathan Gallegos de la CruzAún no hay calificaciones

- ARTISTICADocumento41 páginasARTISTICAASENCIO100% (1)

- Evaluaciones de Enfermedades Tropicales y Parasitología Clínica 1 Al 8 UchDocumento49 páginasEvaluaciones de Enfermedades Tropicales y Parasitología Clínica 1 Al 8 UchJosé Manuel Llamoca ChuquityapeAún no hay calificaciones

- Perfil Ocupacional - Manual A - ZondekDocumento4 páginasPerfil Ocupacional - Manual A - ZondekrocioAún no hay calificaciones

- 2da Sesión - Aproximación A La Vanguardia - "Poema Del Manicomio" de Carlos Oquendo de AmatDocumento4 páginas2da Sesión - Aproximación A La Vanguardia - "Poema Del Manicomio" de Carlos Oquendo de AmatFernando Marcelo DelgadoAún no hay calificaciones

- Dialnet ElSagradoArteDeDespedirse 3179406 PDFDocumento20 páginasDialnet ElSagradoArteDeDespedirse 3179406 PDFweloAún no hay calificaciones

- Escuela Sabatica Leccion 12 1er Trimester 2022Documento7 páginasEscuela Sabatica Leccion 12 1er Trimester 2022Boris BaranovAún no hay calificaciones

- PeroxisomasDocumento8 páginasPeroxisomasSandraJustinoAún no hay calificaciones

- Jerome LejeuneDocumento7 páginasJerome LejeuneXianny BlancoAún no hay calificaciones