Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Referencia VHDL

Cargado por

Rafael Ruiz Cabrera0 calificaciones0% encontró este documento útil (0 votos)

12 vistas2 páginasReferencia VHDL

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoReferencia VHDL

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

12 vistas2 páginasReferencia VHDL

Cargado por

Rafael Ruiz CabreraReferencia VHDL

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 2

Apuntes de VHDL FOR/GENERATE 2.

Tipos de dato, señales y atributos

Rodolfo E. Escobar Uribe, página 1 of 2 <e t i q u e t a >: FOR < i d e n t i f i c a d o r > IN <rango> GENERATE Tipos de dato

<d e c l a r a c i o n concurrente > NOTA: Los tipos integer, signed y unsigned se encuentran

1. Fundamentos del lenguaje END GENERATE ; en el paquete ieee.numeric_std.all.

Nociones básicas IF/GENERATE Tipo Valores sintetizables

El siguiente diagrama muestra la estructura básica de un Una forma no secuancial de IF esta permitida con el incon-

programa en VHDL: veniente de no poder utilizar el modo ELSE: bit,bit_vector ’0’,’1’

std_logic,std_logic_vector ’0’,’1’,’Z’,’X’

boolean True,False

Librerías <e t i q u e t a >: IF <condicion > GENERATE

integer de −231 a 231 − 1

<d e c l a r a c i o n concurrente >

END GENERATE ; signed de −231 a 231 − 1

Entidad

Diseño secuencial unsigned de 0 a 232 − 1

Arquitectura VHDL es inerentemente concurrente. Sin embargo los

únicos segmentos de cádigo que se ejecutan de forma ’0’ Cero lógico sintetizable

secuencial son: PROCESS, FUNCTION y PROCEDURE. El

El siguiente ejemplo es un código que describe la función código secuecial es llamado código behavioral. ’1’ Uno lógico sintetizable

booleana Y = AB + C: ’X’ Desconocido sintetizable

PROCESS

−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−

library ieee ; [ e t i q u e t a : ] PROCESS (< l i s t a de s e n s i b i l i d a d >) ’Z’ Alta impedancia (buffer tri-estado)

use i e e e . s t d _ l o g i c _ 1 1 6 4 . a l l ; [ VARIABLE nombre t i p o [ rango ] [ : = v a l o r _ i n i c a l ; ] ]

use i e e e . numeric_std . a l l ; BEGIN ’-’ Don’t Care

−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−− <codigo s e c u e n c i a l >

entity circuito is END PROCESS [ e t i q u e t a ] ; Señales

p o r t (A : i n s t d _ l o g i c ; Las señales deben declaradas en la arquitectura antes del

B : in s t d _ l o g i c ; Lista de sensibilidad: señales que al cambiar hacen que se begin [sección declarativa]. No es necesario establecer si

C : in s t d _ l o g i c ; ejecute el proceso.

son entradas o salidas.

Y : out s t d _ l o g i c ) ; IF/ELSE

end e n t i t y ; IF <condicion > THEN STD_LOGIC,STD_LOGIC_VECTOR

−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−− <a s i g a n c i o n e s >

a r c h i t e c t u r e arq o f c i r c u i t o i s ELSIF <condicion > THNE s i g n a l <nombre >: STD_LOGIC [ : = <v a l o r i n i c i a l > ] ;

begin <s i g n a c i o n e s > s i g n a l <nombre >: STD_LOGIC_VECTOR <tamano> ;

Y <= (A and not ( B ) ) or C ; ELSE

end a r c h i t e c t u r e ; <a s i g n a c i o n e s > INTEGER,SIGNED, UNSIGNED

−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−− END i f ; s i g n a l <nombre >: INTEGER RANGE <min> t o <max>;

La entidad hace una descripción del circuito entero como CASE Arrays

una caja negra dónde sólo se consideran las entradas y CASE <puerto > I S

salidas. La arquitectura describe el funcionamiento del WHEN <v a l o r > => <a s i g n a c i o n e s >; TYPE <nom_array> I S ARRAY ( tamano / rango ) OF <t i p o >;

sistema. WHEN OTHERS => <a s i g n a c i o n e s >; s i g n a l <nombre >: <nom_array> [ : = <v a l o r e s > ] ;

END CASE ;

Diseño concurrente Atributos

FOR/LOOP Atributos de señal

VHDL no es un lengiaje de programación sino un lenguaje [< e t i q u e t a > : ] FOR < i d e n t i f i c a d o r > IN <rango> LOOP

que describe circuitos electronicos digitales, por lo que su <d e c l a r a c i o n s e c u a n c i a l > s’EVENT Verdadero si un evento ocurre

ejecución es inherentemente concurrente. END LOOP [< e t i q u e t a > ] ;

s’STABLE Verdadero si ningún evento ocurre

WHEN/ELSE WHILE/LOOP

<puerto > <= <val_0 > WHEN <cond_0> ELSE [< e t i q u e t a > : ] WHILE <condicion > LOOP Atributos de dato

<= <val_1 > WHEN <cond_1> ELSE <d e c l a r a c i o n s e c u a n c i a l >

END LOOP [< e t i q u e t a > ] ; d’LOW Retorna índice menor del vector

<= <v a l _ ( n−1)> WHEN <cond_n> ELSE

<= <val_n >; EXIT : usado para salir de un loop d’HIGH Retorna índice mayor del vector

WITH/SELECT/WHEN [< e t i q u e t a >: ] EXIT [< e t i q u e t a >] WHEN <condicion > d’LENGTH Retorna tamaño del vector

WITH <puerto_1 > SELECT

<puerto_2 > <= <val_0 > WHEN <val2_0 >

SKIP: usado para omitir declaración en un loop d’RANGE Retorna rango del vector

<= <val_1 > WHEN <val2_1 > [< e t i q u e t a >: ] SKIP [< e t i q u e t a >] WHEN <condicion >

<= <v a l _ d e f > WHEN OTHERS ; d’REVERSE_RANGE Rango en orden inverso

Apuntes de VHDL 4. Conversión entre tipos 6. Simulación con archivo test bench

Rodolfo E. Escobar Uribe, página 2 of 2 NOTA: Las siguientes funciones de conversión se encuen- La entidad del testbench siempre queda vacía.

tran en el paquete ieee.numeric_std.

3. Operadores Todos los diseños que va an probarse deben ser decla-

Lógicos INTEGER a STD_LOGIC_VECTOR rados como componentes.

•A and B •A nand B •A xnor B signal A : integer ; El proceso de generación del reloj es parte del código

•A or B •A nor B s i g n a l B : s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) ; del testbench.

•not A •A xor B s i g n a l C : s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) ;

Todas las señales asociadas a las entradas deben estar

Aritméticos −− E n t e r o s p o s i t i v o s inicializadas a 0;

NOTA: Los operadores aritméticos sólo pueden usarse B <= s t d _ l o g i c _ v e c t o r ( to_unsigned (A, B ’ l e n g t h ) ) ;

entre elementos de tipos INTEGER,UNSIGNED y SIGNED. −− E n t e r o s p o s i t i v o s o n e g a t i v o s Plantilla de Test Bench

C <= s t d _ l o g i c _ v e c t o r ( t o _ s i g n e d (A, C’ l e n g t h ) ) ; library ieee ;

Operación Descripción Restricción STD_LOGIC_VECTOR a INTEGER use i e e e . s t d _ l o g i c _ 1 1 6 4 . a l l ;

use i e e e . numeric_std . a l l ;

+ Suma s i g n a l A : s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) ;

- Resta signal B : integer ; e n t i t y tb i s

* Multiplicación signal C : integer ; end e n t i t y ;

** Potenciación base y potencia estáticos −− UNSIGNED

/ División sólo potencias de 2 a r c h i t e c t u r e t e s t o f tb i s

B <= t o _ i n t e g e r ( unsigned (A) ) ; −− D e c l a r a c i o n de componente a sim ular

MOD Módulo

−− SIGNED component entidad_elemento i s

REM Residuo p o r t ( x0 : i n s t d _ l o g i c ;

ABS Valor absoluto C <= t o _ i n t e g e r ( si gned (A) ) ;

y0 : out s t d _ l o g i c ) ;

5. Funciones end component ;

NOTA: Las funciones se escriben en la sección declarativa −− D e c l a r a c i o n de s e n a l e s

Desplazamiento de bits de la arquitectura (al igual que las señales) o en el paquete. s i g n a l c l k : out s t d _ l o g i c := 0 ; −− o p c i o n a l

s i g n a l x0 : i n s t d _ l o g i c := 0 ;

Operación Descripción s i g n a l y0 : out s t d _ l o g i c := 0 ;

FUNCTION <nombre> (< argumentos >) RETURN <t i p o > I S −−

<array> sll <n> izquierda lógico <d e c l a r a c i o n e s > −− Constantes

<array> srl <n> derecha lógico BEGIN c o n s t a n t CLK_PERIOD : time := 100 ns ;

<array> sla <n> izquierda aritmético <codigo s e c u e n c i a l > −−

<array> sra <n> derecha aritmético END FUNCTION ; begin −− I n i c i a d e s c r i p c i o n d e l t e s t bench

−− I n s t a n c i a d e l componente

<array> rol <n> rotativo izquierda Los argumentos se declaran de la siguiente manera: dut : entidad_elemento p o r t map(

<array> ror <n> rotativo derecha x0 => x0 ,

( s i g n a l <arg0 >: <t i p o >; s i g n a l <arg1 >: <t i p o > , . . . )

y0 => y0 ) ;

Dentro de una función no es posible declarar señales pero −−

"1100" sll 1 resulta: "1000" si variables que se comportan de la misma manera y son −− Proc eso de r e l o j ( o p c i o n a l )

"1100" srl 2 resulta: "0011" declaradas de la siguiente manera: clk_proc : process

"1100" sla 1 resulta: "1000" begin

Ejemplos: "1100" sra 2 VARIABLE <nombre> : <t i p o > [ : = <v a l o r i n i c i a l >] c l k <= ’ 0 ’ ;

resulta: "1111"

Ejemplo: función de suma de arreglos lógicos. wait f o r CLK_PERIOD/ 2 ;

"1100" rol 1 resulta: "1001" c l k <= ’ 1 ’ ;

"1100" ror 2 resulta: "0011" −−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−− wait f o r CLK_PERIOD/ 2 ;

f u n c t i o n suma ( s i g n a l a , b : s t d _ l o g i c _ v e c t o r ) end p r o c e s s ;

Concatenación return integer i s −−

Operador de concatenación: &. v a r i a b l e a i , b i : i n t e g e r range 0 t o 7 := 0 ; −− Proc eso de e s t i m u l o s

begin stim_proc : p r o c e s s

Ejemplo: a i := t o _ i n t e g e r ( unsigned ( a ) ) ; begin

b i := t o _ i n t e g e r ( unsigned ( b ) ) ; wait f o r 100 ns ;

return a i+bi ; x0 <= ’ 0 ’ ;

s i g n a l A : s t d _ l o g i c _ v e c t o r ( 5 downto 0 ) ;

end f u n c t i o n ; wait f o r 300 ns ;

s i g n a l B , C : s t d _ l o g i c _ v e c t o r ( 2 downto 0 ) ; −−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−

−−− x0 <= ’ 1 ’ ;

−− Ejemplo de llamado : wait ;

B <= ’ 1 ’ & ’ 0 ’ & ’ 1 ’ ;

y i <= suma ( x0 , x1 ) ; end p r o c e s s ;

C <= ’ 0 ’ & ’ 0 ’ & ’ 0 ’ ; −−

A <= B&C ; −− A = "101000" y <= s t d _ l o g i c _ v e c t o r ( to_unsigned ( yi , y ’ l e n g t h ) ) ;

−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−− end a r c h i t e c t u r e ;

También podría gustarte

- VHDL 1.1Documento52 páginasVHDL 1.1azucena castilloAún no hay calificaciones

- VHDL Intro PDFDocumento12 páginasVHDL Intro PDFjessicaAún no hay calificaciones

- Ejercicios Resueltos VHDLDocumento13 páginasEjercicios Resueltos VHDLAnonymous VC5mhPT2GAún no hay calificaciones

- Practica 6Documento12 páginasPractica 6hector blancoAún no hay calificaciones

- Origen VHDLDocumento28 páginasOrigen VHDLJhonatan MartínezAún no hay calificaciones

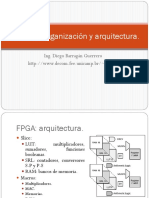

- VHDL Su Organizacion y ArquitecturaDocumento20 páginasVHDL Su Organizacion y ArquitecturaTonaspiuckAún no hay calificaciones

- Práctica 2 - Compuertas Lógicas - Medina Oscar 4-A MAADocumento9 páginasPráctica 2 - Compuertas Lógicas - Medina Oscar 4-A MAAOSCAR ADRIAN MEDINA DURANAún no hay calificaciones

- Cerradura ElectrónicaDocumento7 páginasCerradura ElectrónicaOscar de la HozAún no hay calificaciones

- VHDL Exposición Secuenciales 2018Documento52 páginasVHDL Exposición Secuenciales 2018Alvaro HuanccoAún no hay calificaciones

- VHDLDocumento23 páginasVHDLHolamundoAún no hay calificaciones

- Ejemplos Basicos VHDLDocumento19 páginasEjemplos Basicos VHDLmaylee25Aún no hay calificaciones

- ConversionesDocumento10 páginasConversionesAdolfo LladorAún no hay calificaciones

- Conceptos Basicos de VHDL PDFDocumento15 páginasConceptos Basicos de VHDL PDFHeidyLópzAún no hay calificaciones

- 4-VHDL - Tipos de DatosDocumento19 páginas4-VHDL - Tipos de DatosDaniel ParedesAún no hay calificaciones

- Practica 2.1Documento10 páginasPractica 2.1yoqsan100% (1)

- Practica 1 VHDLDocumento15 páginasPractica 1 VHDLCARLOS MARTINEZ100% (1)

- 1.2.1.3.a Practicas - S.D.L.R IDocumento39 páginas1.2.1.3.a Practicas - S.D.L.R IMaestria en Instrumentación y Control. Facultad de Ingeniería.Aún no hay calificaciones

- Leccion3 ADMIC PDFDocumento34 páginasLeccion3 ADMIC PDFSebastian Gomez VAún no hay calificaciones

- TALLER 1 DIGITALES II - VDocumento8 páginasTALLER 1 DIGITALES II - VJose Elias Perafan LealAún no hay calificaciones

- L4 Bloques Integrados FuncionalesDocumento10 páginasL4 Bloques Integrados FuncionalesEnder Thiago Montoya MendozaAún no hay calificaciones

- Referencia Rápida VHDLDocumento4 páginasReferencia Rápida VHDLerick mondragon quintanaAún no hay calificaciones

- 2 Dispositivos Integrados - Unidad FPGA VHDLDocumento111 páginas2 Dispositivos Integrados - Unidad FPGA VHDLAgustina Gutierrez PariAún no hay calificaciones

- 1.2.1.2.c Antología - SDLR IDocumento180 páginas1.2.1.2.c Antología - SDLR IMaestria en Instrumentación y Control. Facultad de Ingeniería.Aún no hay calificaciones

- Circuitos Combinacionales VHDLDocumento20 páginasCircuitos Combinacionales VHDLNick CohechaAún no hay calificaciones

- Laboratorio N°3 Implementación de Lógica Combinacional Con VHDLDocumento5 páginasLaboratorio N°3 Implementación de Lógica Combinacional Con VHDLANDREA YULIANA TRIANA CAMACHOAún no hay calificaciones

- Programación en VHDLDocumento17 páginasProgramación en VHDLsinchyAún no hay calificaciones

- Conceptos Basicos de VHDLDocumento15 páginasConceptos Basicos de VHDLCatalina Cano NarvaezAún no hay calificaciones

- VHDLDocumento13 páginasVHDLVictor ChuquimiaAún no hay calificaciones

- ¿Qué Es Y para Que Sirve Arduino?Documento36 páginas¿Qué Es Y para Que Sirve Arduino?Manuel GuarnerosAún no hay calificaciones

- VHDL Tipos DescripciónDocumento13 páginasVHDL Tipos Descripciónalejandro delgadoAún no hay calificaciones

- Introducción VHDL sintesis FPGADocumento36 páginasIntroducción VHDL sintesis FPGAJhosep AntonyAún no hay calificaciones

- Practica 02Documento22 páginasPractica 02Jet Ming Adrian Huang SanchezAún no hay calificaciones

- Sentencias en CDocumento40 páginasSentencias en CDARK REASON D'ETREAún no hay calificaciones

- Practica 2 SEDADocumento9 páginasPractica 2 SEDACarlos M del RíoAún no hay calificaciones

- Notas Basicas PLCDocumento3 páginasNotas Basicas PLCAndres4817Aún no hay calificaciones

- Lab FuncionalesDocumento10 páginasLab FuncionalesRonaldo0% (1)

- Practica1 DesarrolloDocumento16 páginasPractica1 DesarrolloDanielEscalonaAún no hay calificaciones

- MICROCONTROLADORESDocumento7 páginasMICROCONTROLADORESCESAR GIOVANNY MORENO RODRIGUEZ100% (1)

- Annotated-Laboratorio20 - DigitalesDocumento47 páginasAnnotated-Laboratorio20 - DigitalesClever Antony Maylle AmbrocioAún no hay calificaciones

- Circuitos CombinacionalesDocumento15 páginasCircuitos CombinacionalesAlejandro Rios CastañedaAún no hay calificaciones

- Microsoft PowerPoint - SistDig-7-2010-14-15 - A (Modo de Compatibilidad) - SistDig-5-17-18 - ADocumento15 páginasMicrosoft PowerPoint - SistDig-7-2010-14-15 - A (Modo de Compatibilidad) - SistDig-5-17-18 - APa BloAún no hay calificaciones

- Manual 04 s2 U2 PCDocumento12 páginasManual 04 s2 U2 PCDannis Omar Campos ZavaletaAún no hay calificaciones

- P1-2 CLO ElectrologicDocumento21 páginasP1-2 CLO Electrologicmiguel recillasAún no hay calificaciones

- Introducción a Verilog y sus estilos de descripciónDocumento42 páginasIntroducción a Verilog y sus estilos de descripciónAndrés M. FernándezAún no hay calificaciones

- Ty SQLDocumento54 páginasTy SQLalexrock4444Aún no hay calificaciones

- Informe Lab1 Sdi1Documento8 páginasInforme Lab1 Sdi1MaticarolinaAún no hay calificaciones

- Monociclo MIPS-VHDL Tercer Entrega Arquitectura de ComputadoresDocumento7 páginasMonociclo MIPS-VHDL Tercer Entrega Arquitectura de ComputadoresJuan Pablo GómezAún no hay calificaciones

- VHDL MatuttiDocumento10 páginasVHDL MatuttiBRIXANY HELEN PONCE HINOSTROZAAún no hay calificaciones

- Sistemas de CalificacionesDocumento14 páginasSistemas de Calificacionesfreddy100% (1)

- 2020.06.15.examen IC3.Aula Virtual de Examen. UNED PDFDocumento2 páginas2020.06.15.examen IC3.Aula Virtual de Examen. UNED PDFDon LimonAún no hay calificaciones

- 2020.06.15.examen IC3.Aula Virtual de Examen. UNEDDocumento2 páginas2020.06.15.examen IC3.Aula Virtual de Examen. UNEDDon LimonAún no hay calificaciones

- ProyectoDocumento17 páginasProyectoGabo FloresAún no hay calificaciones

- Informe Prácticas de LaboratorioDocumento17 páginasInforme Prácticas de LaboratorioMARIA PAULA CABEZAS CHARRYAún no hay calificaciones

- Prepa 4Documento4 páginasPrepa 4Carlos SuarezAún no hay calificaciones

- Introduccion Al Lenguaje VHDLDocumento21 páginasIntroduccion Al Lenguaje VHDLLucho PortuanoAún no hay calificaciones

- LabED1 - MieM5M6 - 6,10 - E5 - P6Documento8 páginasLabED1 - MieM5M6 - 6,10 - E5 - P6n35708lopezAún no hay calificaciones

- Laboratorio N°1 Sistemas DigitalesDocumento8 páginasLaboratorio N°1 Sistemas DigitalesJoel AlvinagortaAún no hay calificaciones

- Practica 5Documento25 páginasPractica 5Renato Beltran CaceresAún no hay calificaciones

- Programación con lenguajes de guión en páginas web. IFCD0110De EverandProgramación con lenguajes de guión en páginas web. IFCD0110Aún no hay calificaciones

- Aprender Arduino, electrónica y programación con 100 ejercicios prácticosDe EverandAprender Arduino, electrónica y programación con 100 ejercicios prácticosCalificación: 4.5 de 5 estrellas4.5/5 (14)

- Bonjour! El Francés A Su Alcance 2Documento122 páginasBonjour! El Francés A Su Alcance 2MariCerra100% (7)

- Libro Tecnico en Electronica - Electronica Del Automovil 2 - (Blog-Jheysonmatta - Blogspot.com) PDFDocumento134 páginasLibro Tecnico en Electronica - Electronica Del Automovil 2 - (Blog-Jheysonmatta - Blogspot.com) PDFPablo Restrepo Ossa86% (14)

- Pasatiempo - Básico (Con Respuestas)Documento78 páginasPasatiempo - Básico (Con Respuestas)sgmAún no hay calificaciones

- Pasatiempo - Básico (Sin Respuestas) PDFDocumento78 páginasPasatiempo - Básico (Sin Respuestas) PDFpablojmirAún no hay calificaciones

- Manual PCMFordDocumento79 páginasManual PCMFordVince Rodriguez95% (141)

- Conceptos de Capas y Herramientas de Adobe PhotoshopDocumento6 páginasConceptos de Capas y Herramientas de Adobe PhotoshopSUSANAAún no hay calificaciones

- ESD115 Grupo1 Tutoria7 Eje2 PDFDocumento4 páginasESD115 Grupo1 Tutoria7 Eje2 PDFKevinAún no hay calificaciones

- 207 - Presentación PickData Completa para Webinar 2020 ESDocumento47 páginas207 - Presentación PickData Completa para Webinar 2020 ESNoccontrol CorpAún no hay calificaciones

- Robot Panda descripción y programación trayectoria letra ODocumento10 páginasRobot Panda descripción y programación trayectoria letra OValentina Vega MahechaAún no hay calificaciones

- Control de ErroresDocumento4 páginasControl de ErroresCarlos Cahuana Castillo100% (1)

- Curso Fortran ActualizadoDocumento88 páginasCurso Fortran ActualizadoyoleidacrAún no hay calificaciones

- Plantilla-Scrum - GRUPO #8Documento22 páginasPlantilla-Scrum - GRUPO #8Cacon EntertainmentAún no hay calificaciones

- Cuáles Son Las Diferencias Entre Programar Del Lado Del Cliente y Lado Del ServidorDocumento2 páginasCuáles Son Las Diferencias Entre Programar Del Lado Del Cliente y Lado Del ServidorSaid Suarez FloresAún no hay calificaciones

- Taller 2 Conceptos Básicos de Mantenimientos de ComputadorasDocumento7 páginasTaller 2 Conceptos Básicos de Mantenimientos de Computadorasgranjas七つの大罪Aún no hay calificaciones

- Informe Datacenter Luis MaldonadoDocumento20 páginasInforme Datacenter Luis MaldonadoJoel GutiérrezAún no hay calificaciones

- Test Lavadora SamsungDocumento61 páginasTest Lavadora SamsungChristian Layton89% (9)

- Electrónica de PotenciaDocumento3 páginasElectrónica de Potenciajesus alberto islas pachecoAún no hay calificaciones

- 1.curriculum Vitae Eddy AmperezDocumento7 páginas1.curriculum Vitae Eddy AmperezSrv mediaAún no hay calificaciones

- Como Entrar Al Bios Y Bootear Un CD-By ThErODocumento5 páginasComo Entrar Al Bios Y Bootear Un CD-By ThErOJuan Pablo Figueroa LetelierAún no hay calificaciones

- Examen Parcial PFD - Teoria (Faustino)Documento7 páginasExamen Parcial PFD - Teoria (Faustino)Waldir Aldair GONZALES CASTILLOAún no hay calificaciones

- Comunicación Entre Raspberry Pi 3B+ y Controladora de Vuelo Pixhawk A Través Del Protocolo MAVLinkDocumento18 páginasComunicación Entre Raspberry Pi 3B+ y Controladora de Vuelo Pixhawk A Través Del Protocolo MAVLinkjimer100% (1)

- Semana 03 - 2 JavaScriptDocumento189 páginasSemana 03 - 2 JavaScriptLuisAún no hay calificaciones

- Amplificadores de 40WDocumento7 páginasAmplificadores de 40WSebas MaldonadoAún no hay calificaciones

- Algoritmo de Ordenamiento (Insert - Bubble)Documento4 páginasAlgoritmo de Ordenamiento (Insert - Bubble)Adrian OrielAún no hay calificaciones

- Los Generadores de Pulsos Son Instrumentos Diseñados para Producir Un Tren Periódico de Pulsos de Igual AmplitudDocumento3 páginasLos Generadores de Pulsos Son Instrumentos Diseñados para Producir Un Tren Periódico de Pulsos de Igual Amplitudjorge alfaroAún no hay calificaciones

- Componentes Internos y Externos de Una ComputadoraDocumento12 páginasComponentes Internos y Externos de Una ComputadoraSanabria Marcani EverAún no hay calificaciones

- ejTC1 0910Documento29 páginasejTC1 0910sugenataAún no hay calificaciones

- Teoría ReactDocumento59 páginasTeoría ReactAlbert Arrieta LozanoAún no hay calificaciones

- MicrocontroladoresDocumento4 páginasMicrocontroladoresmunoz-1994Aún no hay calificaciones

- Fam KenwoodDocumento12 páginasFam KenwoodDaniel Fernando Sotelo Sotelo LagosAún no hay calificaciones

- Taller MantenimientoDocumento6 páginasTaller MantenimientoHASOAún no hay calificaciones

- MANUAL DE SERVICIO Prosound Alpha 7 Vol 1Documento149 páginasMANUAL DE SERVICIO Prosound Alpha 7 Vol 1Faustina2013100% (5)

- Autodesk Inventor Professional 2012 SerialDocumento4 páginasAutodesk Inventor Professional 2012 SerialUlises AgüeroAún no hay calificaciones

- Unidad 1 - Introducción A Snap!Documento11 páginasUnidad 1 - Introducción A Snap!Marìa Josè Duràn DurànAún no hay calificaciones

- Vs 0864 LogDocumento57 páginasVs 0864 Lognope notgonnahappenAún no hay calificaciones