Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Algoritmo de Sumador BCD

Cargado por

hectorDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Algoritmo de Sumador BCD

Cargado por

hectorCopyright:

Formatos disponibles

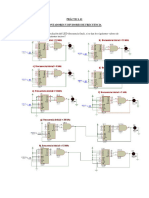

Algoritmo de sumador BCD

1. Se suman dos grupos en BCD un numero A y un numero B para cada posicion de los digitos

utilizados. 2. Para aquellas posiciones donde la suma es menor o igual a 9 la suma se encuentra

en BCD y no nececita hacer la correccion. 3. Cuando la suma de dos sifras es mayor que 9 debe

agregarse la correccion de 6 enbinario (0110) para producir el resultado BCD correcto, esto

producira un acarreo que se sumara a la suguiente posicion.

El primer paso se cumple al utilizar un sumador paralelo de 4 bits tal como el circuito integrado

7483 donde el numero A=A3A2A1A0 y el numero B=B3B2B1B0 si se aplicaun sumador paralelo

de 4 bits. Donde el C4 es el acarreo final de salida. La salida del sumador puede variar de valor

de oooo a 1001 o cuando A y B son iguales a 9.

La circuiteria necesaria de un sumador BCD debe incluir la logica necesaria para detectar

aquellas sumas mayores que 9 de manera que se pueda agregar la correccion de 0110

Se define una variable x como una salida lgica que tomara un valor alto cuando la suma sea

mayor que 9, es decir X=1 en los casos siguientes: 1. Siempre que C4=1 para sumas mayores

que 15 2. Siempre que S3=1 Y S2+S1 en sumas mayores que 9 y menores que 15.

Esto se expresa en una ecuacin lgica como X=C4+C3(S2+S1) de esta forma siempre que X=1

se sumara la correccin de 0110 a la suma original generando un acarreo tal como se muestra

en la figura. 3. El sumador inferior sumara la correccin de 0110 a los bits de la suma binaria

del sumador superior solo cuando x=1 y produciendo una salida final en cdigo BCD.

Un codificador es un circuito combinacional con M lneas de entrada y genera un cdigo de

salida de n bits.

Un decodificador es un circuito que convierte informacin binaria de un cdigo de entrada de

n bits codificados a un mximo de 2n salidas juntas.

Un multiplexor tambin llamado selector de datos es un circuito lgico que capta varias

entradas de datos y permite que solo una de ellas alcance la sala, la direccin deceada de los

datos de entrada hacia la salida es controlada por n lneas de seleccin.

Demultiplexor es un circuito combinacional que realiza la seleccin de datos de una sola

entrada a dos o en 2n lneas de salida de acuerdo a n lneas de seleccin. La seleccin de la

salida es controlada por la combinacin de los bits en las n lneas selectoras.

Los PLDs son circuitos integrados desarrollados para aplicaciones espesificas, reduciendo el

espacio fsico en las aplicaciones son circuitos integrados fabricados y revisados para que se

puedan personalizar desde el exterior mediante las tcnicas de programacin. Estn

construidos por bloques lgicos configurables conectados mediante bloques de interfases con

interconexiones programables. Ventajas: reduccin del numero de elementos necesarios,

menor tiempo de diseo, velocidad de respuesta, inmunidad al ruido, menores costos.

SPLDs(dispositivos lgicos programables simples) CPLDs (complejos) FPGAS (matrices de

puertas programables por campo) DISPOSITIVOS HIBRIDOS (PLDS-FPGAS, I2L-AID-CPLDS) ASIC

(circuitos de aplicacin espesifica) PROMS (memorias de solo lectura programables solo una

vez) PAL (lgica de arreglos programables) PLAS (programables de arreglos lgicos)

Existen cinco tipos de unidades de diseo en VHDL: declaracion de la entidad ( ENTITY), la

arquitectura (Architecture), la configuracin (configuration), declaracin del paquete (pachage

body). Entity y architecture son indispensables.

Entity: declaracin de la entidad que es un envolvente de diseo.

Entity caja_negra is

PORT (entrada A: in std_logic;

entrada B: in std_logic;

salida x: out std_logic);

end caja_negra;

architecture: define el funcionamiento de la entidad. La sentencia library es un llamado al

archivo o directorio que guarda las unidades de diseo previamente compiladas.

Architecture Nombre_Arch of Entidad is

Declaracion de tipos de datos

Declaracion de seales

Declaracin de constantes

Declaracin de funciones

Declaracin de procedimientos

Declaracin de componentes

End Nombre_Arch;

Library IEEE

Use IEEE.std_Logic_1164.ALL

Entity Comp_NOR is

Port (A, B: in std_Logic;

f: out std_Logic);

end Comp_NOR;

Architecture NOR of Comp_NOR is

begin

process (A,B)

begin if (A=0) and (B=0) then f<=1

else f<=0;

end if;

end process;

end NOR;

También podría gustarte

- 04a - Programacion Dinamica DeterministicaDocumento6 páginas04a - Programacion Dinamica DeterministicaKevin Flores AlvarezAún no hay calificaciones

- Lab04 Decodificador Display 7segDocumento5 páginasLab04 Decodificador Display 7segLC LyonAún no hay calificaciones

- Rectificadores y Fuentes de Alimentación - CompletoDocumento50 páginasRectificadores y Fuentes de Alimentación - CompletoJaja LocoAún no hay calificaciones

- Resistencia EléctricaDocumento29 páginasResistencia EléctricaHernan QuishpeAún no hay calificaciones

- Capitulo9 CircuitosLogicosDocumento13 páginasCapitulo9 CircuitosLogicosRonald Requejo SamameAún no hay calificaciones

- Problemas de CodificadoresDocumento21 páginasProblemas de CodificadoresMarcos AlfaroAún no hay calificaciones

- Practica - 1 Sis Digis 2Documento7 páginasPractica - 1 Sis Digis 2Mathy MerinoAún no hay calificaciones

- Sistema Básico de Entrada y Salida El BiosDocumento27 páginasSistema Básico de Entrada y Salida El BiosWildines LópezAún no hay calificaciones

- Glab S01 Cmendiola 2023 1Documento7 páginasGlab S01 Cmendiola 2023 1Alex Fernando Arias MamaniAún no hay calificaciones

- S11.s1-Representacion de Variables de EstadoDocumento28 páginasS11.s1-Representacion de Variables de EstadoAntonio CamiloagaAún no hay calificaciones

- S05.s2-Material de ClaseDocumento26 páginasS05.s2-Material de ClaseCleiver Iván AguilarAún no hay calificaciones

- Diodo de PotenciaDocumento69 páginasDiodo de PotenciaMichael R. ArayaAún no hay calificaciones

- Transistores BJTDocumento21 páginasTransistores BJTJose100% (1)

- Presentadfción 1Documento100 páginasPresentadfción 1DavePrs100% (1)

- 1Clase-Control-Digital 2023-1Documento56 páginas1Clase-Control-Digital 2023-1Walter Ruiz PorrasAún no hay calificaciones

- Amplificadores Clase ADocumento6 páginasAmplificadores Clase ALuis AndreAún no hay calificaciones

- Elec Clase 3Documento31 páginasElec Clase 3Celeste SantanderAún no hay calificaciones

- Clase 16Documento22 páginasClase 16Arturo Tadeo Calderón SalazarAún no hay calificaciones

- Presentacion AmplificadorDocumento23 páginasPresentacion AmplificadorRwbfwhfcb BskdbcvdhbsAún no hay calificaciones

- Elec Clase 2Documento26 páginasElec Clase 2Celeste SantanderAún no hay calificaciones

- Clase2 IIDocumento43 páginasClase2 IIAldahir Garcilazo RomeroAún no hay calificaciones

- Amplificador Clase ABDocumento3 páginasAmplificador Clase ABKorange IkaAún no hay calificaciones

- Filtro LCDocumento3 páginasFiltro LCIsrael BackusAún no hay calificaciones

- Tema 3 Ao PDFDocumento8 páginasTema 3 Ao PDFJorge SGAún no hay calificaciones

- Corte 1.1 Introducción A La Electrónica de PotenciaDocumento12 páginasCorte 1.1 Introducción A La Electrónica de PotenciaJonny A ONAún no hay calificaciones

- Circuitos Digitales 1 Informe 3Documento39 páginasCircuitos Digitales 1 Informe 3Rasec MundoAún no hay calificaciones

- Simulacion de TinkercadDocumento7 páginasSimulacion de TinkercadHarlen Robert Archibold IbarraAún no hay calificaciones

- Desarrollo de Un Robot Móvil Con Brazo Robótico para La Gestión de Desastres Naturales en El PerúDocumento25 páginasDesarrollo de Un Robot Móvil Con Brazo Robótico para La Gestión de Desastres Naturales en El PerúPrimus 2018Aún no hay calificaciones

- S02.s1 Material ACCC 1Documento32 páginasS02.s1 Material ACCC 1Segundo Estela CubasAún no hay calificaciones

- Lab 1-3 Amp Clase B AbDocumento25 páginasLab 1-3 Amp Clase B AbAlex ArévaloAún no hay calificaciones

- Lab02 Osciloscopio y GeneradorFxDocumento8 páginasLab02 Osciloscopio y GeneradorFxHarold Zavaleta CastroAún no hay calificaciones

- 04 - Circuitos Rectificadores y FiltroDocumento11 páginas04 - Circuitos Rectificadores y Filtrodiego181802Aún no hay calificaciones

- Labo 2 - Control DigitalDocumento20 páginasLabo 2 - Control DigitalDavid JPAún no hay calificaciones

- Electrotecnia 1ros 12 JulDocumento13 páginasElectrotecnia 1ros 12 JulNick KlarkAún no hay calificaciones

- S04.s1 - Filtros Por CondensadorDocumento16 páginasS04.s1 - Filtros Por CondensadorAlejandro HigaAún no hay calificaciones

- Codigo TrellisDocumento15 páginasCodigo TrellisSILVERACAún no hay calificaciones

- Simbología y AplicacionesDocumento10 páginasSimbología y AplicacionespolicomiAún no hay calificaciones

- Amplificador Clase BDocumento5 páginasAmplificador Clase Bjosebroce4Aún no hay calificaciones

- S01.s1 - Introducción A Los Sistemas de Control DigitalDocumento33 páginasS01.s1 - Introducción A Los Sistemas de Control DigitalSteve NuñezAún no hay calificaciones

- s05 s14 MaterialDocumento26 páginass05 s14 MaterialEdison Lujan vicañaAún no hay calificaciones

- Las Variables de EstadoDocumento4 páginasLas Variables de EstadoORLANDO RODRIGUEZAún no hay calificaciones

- Tecnica de Control Digital IDocumento68 páginasTecnica de Control Digital Ijlb1212Aún no hay calificaciones

- Laboratorio N01 Control Digital PDFDocumento11 páginasLaboratorio N01 Control Digital PDFjorgeAún no hay calificaciones

- ED Practica - 6 Decodificador BCDDocumento2 páginasED Practica - 6 Decodificador BCDCarlos DeleiverAún no hay calificaciones

- Clase 6 Espacio de Estados PLDocumento30 páginasClase 6 Espacio de Estados PLBRYAN FABIAN SIMBA�A FERNANDEZAún no hay calificaciones

- Filtro de CondensadorDocumento6 páginasFiltro de CondensadorJose L Huaman GasparAún no hay calificaciones

- Clase 5, Modelos en Variables de EstadoDocumento28 páginasClase 5, Modelos en Variables de EstadoCarlos GarayAún no hay calificaciones

- 6 Circuitos Combinacionales P ImprimirDocumento36 páginas6 Circuitos Combinacionales P ImprimirFabian AcostaAún no hay calificaciones

- Amplificadores de Potencia IDocumento34 páginasAmplificadores de Potencia IJuan Manuel MuñozAún no hay calificaciones

- Consulta, Factor de Rizado y FiltrosDocumento3 páginasConsulta, Factor de Rizado y FiltrosPaty SalazarAún no hay calificaciones

- Amplificador Clase B ABDocumento8 páginasAmplificador Clase B ABsantiagoAún no hay calificaciones

- L5-Filtro Por CondensadorDocumento5 páginasL5-Filtro Por CondensadorLuis Diego Cuzcano RomoAún no hay calificaciones

- Leccion 4 El DiodoDocumento45 páginasLeccion 4 El DiodoAnibal Muñiz SilvaAún no hay calificaciones

- S02.s1 - Sistemas de Control DigitalDocumento27 páginasS02.s1 - Sistemas de Control DigitalJonas Huamani PumaAún no hay calificaciones

- CuestionarioDocumento2 páginasCuestionarioJonathan Becerra MonroyAún no hay calificaciones

- Hojas Datos de DiodosDocumento6 páginasHojas Datos de DiodosVentura CanoAún no hay calificaciones

- LAN TesterDocumento13 páginasLAN TesterThomas Manrique100% (1)

- Circuitos de Filtrado Con Componentes PasivosDocumento7 páginasCircuitos de Filtrado Con Componentes PasivosFhertronics AutotronicaAún no hay calificaciones

- Practica 4 - ModificadaDocumento6 páginasPractica 4 - ModificadaEddy FernandoAún no hay calificaciones

- Practica Decodificadores y Codificadores TerminadoDocumento25 páginasPractica Decodificadores y Codificadores TerminadojavierAún no hay calificaciones

- Unidad 2 ArmadurasDocumento7 páginasUnidad 2 ArmadurashectorAún no hay calificaciones

- LedsDocumento2 páginasLedshectorAún no hay calificaciones

- Proyecto AmadorDocumento5 páginasProyecto AmadorhectorAún no hay calificaciones

- Proyecto Amador PDFDocumento5 páginasProyecto Amador PDFhectorAún no hay calificaciones

- Practica 3 de ControlDocumento7 páginasPractica 3 de ControlhectorAún no hay calificaciones

- Practica 3 de ControlDocumento7 páginasPractica 3 de ControlhectorAún no hay calificaciones

- P#3 Sensor de Proximidad Equipo#3 Meca2ADocumento12 páginasP#3 Sensor de Proximidad Equipo#3 Meca2AhectorAún no hay calificaciones

- Admooon DosDocumento3 páginasAdmooon DoshectorAún no hay calificaciones

- Unidad 2 ArmadurasDocumento7 páginasUnidad 2 ArmadurashectorAún no hay calificaciones

- Unidad 3Documento9 páginasUnidad 3hectorAún no hay calificaciones

- Discurso de Despedida A Los Alumnos de Tercer GradoDocumento3 páginasDiscurso de Despedida A Los Alumnos de Tercer Gradohector0% (1)

- Silla Con Elevador 1.0Documento1 páginaSilla Con Elevador 1.0hectorAún no hay calificaciones

- Apuntes de Desarrollo Sustentable U.2Documento6 páginasApuntes de Desarrollo Sustentable U.2hectorAún no hay calificaciones

- Fisica y TermoDocumento48 páginasFisica y TermoRobert Andres Ceron BurbanoAún no hay calificaciones

- Vibraciones Mec 2011. Cap 2 PDFDocumento41 páginasVibraciones Mec 2011. Cap 2 PDFNibaldo BernardoAún no hay calificaciones

- Biologia PDFDocumento41 páginasBiologia PDFhectorAún no hay calificaciones

- Biologia PDFDocumento41 páginasBiologia PDFhectorAún no hay calificaciones

- EL3003 Rectificadores FINAL Otro GrupoDocumento20 páginasEL3003 Rectificadores FINAL Otro GrupoChristian EspinozaAún no hay calificaciones

- Practica 2 Lab Electronica Potencia IIDocumento5 páginasPractica 2 Lab Electronica Potencia IIDaniel Palomares GAún no hay calificaciones

- Estres en OrganizacionesDocumento18 páginasEstres en OrganizacioneshectorAún no hay calificaciones

- Estructura Lateral SuperiorDocumento1 páginaEstructura Lateral SuperiorhectorAún no hay calificaciones

- Cotizacion de PararrayosDocumento1 páginaCotizacion de PararrayosEmilio Cardenas ChuAún no hay calificaciones

- Formulario - Sistemas de Control AutomáticosDocumento3 páginasFormulario - Sistemas de Control AutomáticosRuben Perez Mamani100% (1)

- 198111Documento54 páginas198111Mario ParedesAún no hay calificaciones

- Incorporador de AireDocumento11 páginasIncorporador de AireKlever Saenz RepuelloAún no hay calificaciones

- Bombas LOU IDocumento45 páginasBombas LOU ILuis Cesar Gutierrez MedranoAún no hay calificaciones

- Trabajo - Practico4 Ejercicios de Esfuerzo EfectivoDocumento4 páginasTrabajo - Practico4 Ejercicios de Esfuerzo Efectivorafael romanAún no hay calificaciones

- PRACTICA 07 2016 - CEs (Sales)Documento41 páginasPRACTICA 07 2016 - CEs (Sales)Vera Cieza EynerAún no hay calificaciones

- CBC MecanicoautoDocumento429 páginasCBC MecanicoautojoseritoAún no hay calificaciones

- Proyecto Integrador Mecánica de FluidosDocumento12 páginasProyecto Integrador Mecánica de Fluidospaulo50% (2)

- Catalogo SpencerDocumento32 páginasCatalogo SpencerCesar PanizoAún no hay calificaciones

- Guia de Aprendizaje Semana2 - LuisBuitragoDocumento3 páginasGuia de Aprendizaje Semana2 - LuisBuitragoluisbuitragorey50% (2)

- Estudio Cantera y Diseño MezclaDocumento23 páginasEstudio Cantera y Diseño Mezclasaidy24100% (1)

- Calibrar C15 y C18Documento4 páginasCalibrar C15 y C18Helio Villar Rabanal100% (3)

- Segunda EntregaDocumento3 páginasSegunda EntregaMaria Margarita AndradeAún no hay calificaciones

- NetflixDocumento22 páginasNetflixAnonymous ljbMSyqgAún no hay calificaciones

- Estudio HidrogeológicoDocumento47 páginasEstudio HidrogeológicoSergio AndrésAún no hay calificaciones

- Ensayo Residuos IndustrialesDocumento4 páginasEnsayo Residuos IndustrialesAnva Arboleda Valencia100% (1)

- Manual Usuario Maior Eolo 28 4EDocumento32 páginasManual Usuario Maior Eolo 28 4EHarlan Simonetti JaraAún no hay calificaciones

- Inversiones Vila Andreu S, ADocumento1 páginaInversiones Vila Andreu S, ANathanael JoyaAún no hay calificaciones

- Compensación de La Energia Reactiva BT y MT PDFDocumento144 páginasCompensación de La Energia Reactiva BT y MT PDFAlfredo GilAún no hay calificaciones

- Curso Basico de Arcgis 3d AnalystDocumento35 páginasCurso Basico de Arcgis 3d AnalystAreli NogueiraAún no hay calificaciones

- 23.7 MANUAL LIPOLASER ACTUALIZADO (Correjir)Documento31 páginas23.7 MANUAL LIPOLASER ACTUALIZADO (Correjir)oscar martinezAún no hay calificaciones

- Guía de Geometría y Trigonometría 2018Documento145 páginasGuía de Geometría y Trigonometría 2018Miguel Esparza OchoaAún no hay calificaciones

- Infraestructura VIAL EN PERUDocumento27 páginasInfraestructura VIAL EN PERUAlex PanccAún no hay calificaciones

- Proyecto de Equipamiento de Laboratorio de Mantenimiento Electrico de Fases 1,2,3,4,5,6 Revision 2Documento30 páginasProyecto de Equipamiento de Laboratorio de Mantenimiento Electrico de Fases 1,2,3,4,5,6 Revision 2Fernando Peñafiel FernandezAún no hay calificaciones

- Informe #4 I. Datos Informativos DE: Arias Vilca, Angélica MaríaDocumento5 páginasInforme #4 I. Datos Informativos DE: Arias Vilca, Angélica Maríaapi-520847691Aún no hay calificaciones

- Aritmetica en El ComputadorDocumento40 páginasAritmetica en El ComputadorJaime Oros GamarraAún no hay calificaciones

- Cómo Crear Un Efecto de Texto de Cómic - Scribus WikiDocumento2 páginasCómo Crear Un Efecto de Texto de Cómic - Scribus WikiPayasoTecnoAún no hay calificaciones

- PC-03 (Es832-I) 2021-1Documento1 páginaPC-03 (Es832-I) 2021-1JORGE ENRIQUEAún no hay calificaciones

- Tanque Septico y LetrinasDocumento32 páginasTanque Septico y LetrinasDiegoRiveroPardoAún no hay calificaciones