Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Lab 1 Digital 1 07032013 PDF

Lab 1 Digital 1 07032013 PDF

Cargado por

Jasmany FaritTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Lab 1 Digital 1 07032013 PDF

Lab 1 Digital 1 07032013 PDF

Cargado por

Jasmany FaritCopyright:

Formatos disponibles

UNIVERSIDAD TECNICA DE ORURO

FACULTAD NACIONAL DE INGENIERIA

CARRERA: INGENIERIA ELECTRICA ELECTRONICA

LABORATORIO DE DISEO DE SISTEMAS DE CONTROL (ELT 3832)

_____________________________________________________________________________

LABORATORIO N 1

SIMPLIFICACION DE FUNCIONES LOGICAS POR MAPAS DE KARNAUGH Y

ALGEBRA DE BOOLE

1.- Objetivo.- Realizar la simplificacin de funciones lgicas mediante mapas de

Karnaugh y Algebra de Boole.

2.- Fundamento Terico.El mapa de Karnaugh es un mtodo grfico que se utiliza para simplificar una ecuacin

lgica para convertir una tabla de verdad a su circuito lgico correspondiente en un

proceso simple y ordenado. Aunque un mapa de Karnaugh (que de aqu en adelante se

abreviar como mapa K) se puede utilizar para resolver problemas con cualquier numero

de variables de entrada, su utilidad practica se limita a seis variables.

Ejemplo: Se tiene la siguiente tabla de verdad para tres variables.

F=ABC+ABC+ABC+ABC+ABC+ABC

Se desarrolla la funcin lgica basada en ella. (primera forma cannica). Ver que en la

frmula se incluyen solamente las variables (A, B, C) cuando F cuando es igual a "1".

Si A en la tabla de verdad es "0" se pone A, si B = "1" se pone B, Si C = "0" se pone C,

etc

Una vez obtenida la funcin lgica, se implementa el mapa de Karnaugh.

UNIVERSIDAD TECNICA DE ORURO

FACULTAD NACIONAL DE INGENIERIA

CARRERA: INGENIERIA ELECTRICA ELECTRONICA

LABORATORIO DE DISEO DE SISTEMAS DE CONTROL (ELT 3832)

_____________________________________________________________________________

Este mapa tiene 8 casillas que corresponden a 2 n, donde

n = 3 (nmero de variables (A, B, C))

La primera fila corresponde a A = 0

La segunda fila corresponde a A = 1

La primera columna corresponde a BC = 00 (B=0 y C=0)

La segunda columna corresponde a BC = 01 (B=0 y C=1)

La tercera columna corresponde a BC = 11 (B=1 y C=1)

La cuarta columna corresponde a BC=10 (B=1 y C=0)

En el mapa de Karnaugh se han puesto "1" en las casillas que corresponden a los

valores de F = "1" en la tabla de verdad.

Tomar en cuenta la numeracin de las filas de la tabla de verdad y la numeracin de las

casillas en el mapa de Karnaugh.

Para proceder con la simplificacin, se crean grupos de "1"s que tengan 1, 2, 4, 8, 16,

etc. (slo potencias de 2).

Los "1"s deben estar adyacentes (no en diagonal) y mientras ms "1"s tenga el grupo,

mejor.

La funcin mejor simplificada es aquella que tiene el menor nmero de grupos

con el mayor nmero de "1"s en cada grupo

Se ve del grfico que hay dos grupos cada uno de cuatro "1"s, (se permite compartir

casillas entre los grupos).

La nueva expresin de la funcin boolena simplificada se deduce del mapa de

Karnaugh.

- Para el primer grupo (rojo): la simplificacin da B (los "1"s de la tercera y cuarta

columna) corresponden a B sin negar)

- Para el segundo grupo (azul): la simplificacin da A (los "1"s estn en la fila inferior que

corresponde a A sin negar)

Entonces el resultado es F = B + A F = A + B

UNIVERSIDAD TECNICA DE ORURO

FACULTAD NACIONAL DE INGENIERIA

CARRERA: INGENIERIA ELECTRICA ELECTRONICA

LABORATORIO DE DISEO DE SISTEMAS DE CONTROL (ELT 3832)

_____________________________________________________________________________

Ejemplo:

Una tabla de verdad como la de la derecha da la siguiente

funcin booleana:

F= ABC+ABC+ABC+ABC

Se ve claramente que la funcin es un reflejo del contenido de

la tabla de verdad cuando F = "1"

Con esta ecuacin se crea el mapa de Karnaugh y se

escogen los grupos. Se lograron hacer 3 grupos de dos "1"s

cada uno.

Se puede ver que no es posible hacer grupos de 3, porque

3 no es potencia de 2. Se observa que hay una casilla que

es

Compartida por los tres grupos.

La funcin simplificada es:

F=AB+AC+BC

Laboratorio:

Grupo: 10:30 a 12:00

1) Se pretende construir un circuito combinacional de control de paro automtico del

motor de un ascensor de un edificio. El funcionamiento del motor depende de 4 variables.

En el caso, que la puerta del ascensor est abierta o cerrada (A); en segundo lugar, del

peso de las personas que suben al ascensor (B); en tercer lugar, que alguna de las

personas haya pulsado los pulsadores de las distintas plantas (C); y por ltimo, de la

temperatura del motor (D). El motor se parar automticamente siempre que la puerta del

ascensor est abierta, o bien se sobrepase el peso mximo, que es de 1000 kg.

a) Calcule la funcin lgica de salida de paro automtico del motor del ascensor.

b) Simplifique la funcin lgica mediante el mtodo de Karnaugh y Algebra de Boole

c) Implemente el circuito con compuertas lgicas TTL

UNIVERSIDAD TECNICA DE ORURO

FACULTAD NACIONAL DE INGENIERIA

CARRERA: INGENIERIA ELECTRICA ELECTRONICA

LABORATORIO DE DISEO DE SISTEMAS DE CONTROL (ELT 3832)

_____________________________________________________________________________

2) Un circuito digital consta de cinco entradas (a, b, c, d y e) y una salida F. Esta salida

tomar el valor lgico 1 cuando existan mayoria de unos en las cinco entradas.

a) Obtener la tabla de verdad y la funcin lgica del circuito.

b) Simplificar la funcin lgica mediante el mtodo de Karnaugh y Algebra de Boole.

c) Implementar el circuito con compuertas lgicas TTL

3) En un control de calidad de un proceso industrial, las piezas acabadas se verifican de

cuatro en cuatro. El proceso ser diseado cuando, al menos dos de las cuatro piezas

estn defectuosas se dispare una seal de alarma.

a) Obtener la tabla de verdad y la funcin lgica del circuito.

b) Simplifique la funcin lgica obtenida mediante el mtodo de Karnaugh y Algebra de

Boole.

c) Implemente el circuito con compuertas lgicas TTL

4) Dada la siguiente funcion logica F= ( 1,3,4,6,8,9,11,14,15,16,19,23,25,29,30)

a) Simplifique la funcin obtenida utilizando el mapa de Karnaugh y Algebra de Boole.

c) Implemente la funcin simplificada con compuertas lgicas TTL

Grupo 16:00 a 18:00

1) Disee el circuito lgico del sistema de alarma contra robos de la caja fuerte de un

banco cuyo esquema se muestra en la figura. El sensor de presin est ubicado debajo

de la caja para saber si alguin intenta moverla de su lugar. La puerta slo puede abrirse

en horario de oficina.

Escriba la ecuacin de la salida de alarma de modo que produzca un 1 lgico cuando la

caja se mueve y el interruptor de control est cerrado, o cuando el gabinete se abre fuera

de horas hbiles, o cuando el gabinete est abierto con el interruptor de control abierto.

Construya el circuito de la alarma usando circuitos integrados CMOS

UNIVERSIDAD TECNICA DE ORURO

FACULTAD NACIONAL DE INGENIERIA

CARRERA: INGENIERIA ELECTRICA ELECTRONICA

LABORATORIO DE DISEO DE SISTEMAS DE CONTROL (ELT 3832)

_____________________________________________________________________________

Vcc

Cerrado

Int. Control

Abierto

Vcc

Alarma

Sensor de Presin

Normal

Alarma

Vcc

Horas

hbiles

Fuera de Trab.

tttTraba

Vcc

horario

Cerrada

Reloj

B

CIRCUITO

Puerta

Abierta

LGICO

ALRM

a) Obtenga la tabla de verdad y la funcin lgica.

b) Simplifique la funcin obtenida utilizando el mapa de Karnaugh y Algebra de Boole.

c) Implemente la funcin simplificada con compuertas lgicas CMOS

C

2) El sistema de disparo (apagado del reactor) de una central nuclear est controlado por

cinco seales: una de disparo manual del reactor (A), y otras cuatro de disparo

automtico (B, C, D, E ). El sistema se activar siempre que se produzca disparo manual

o cuando al menos dos de las seales de disparo automtico se activen.

a) Obtenga la tabla de verdad y la funcin lgica.

b) Simplifique la funcin obtenida utilizando el mapa de Karnaugh y Algebra de Boole.

c) Implemente la funcin simplificada con compuertas lgicas TTL

3) Dada la siguiente funcion logica F= ( 0,1,3,5,6,7,12,13,14,16,21,22,28,29,30,31)

a) Simplifique la funcin obtenida utilizando el mapa de Karnaugh y Algebra de Boole.

b) Implemente la funcin simplificada con compuertas lgicas CMOS.

UNIVERSIDAD TECNICA DE ORURO

FACULTAD NACIONAL DE INGENIERIA

CARRERA: INGENIERIA ELECTRICA ELECTRONICA

LABORATORIO DE DISEO DE SISTEMAS DE CONTROL (ELT 3832)

_____________________________________________________________________________

4) Disee un circuito digital de control, que compare a la entrada dos palabras binarias de

2 bits (ab y cd), de manera que cuando la combinacin binaria formada por los bits ab,

sea menor que la combinacin binaria formada por los bits cd, la salida sea 1.

a) Calcule la funcin lgica de salida del circuito que activa el motor de cierre.

b) Simplifique la funcin lgica mediante el mtodo de Karnaugh y Algebra de Boole

c) Implemente el circuito con puertas lgicas universales TTL.

Informe: Realizar e implementar la practica en grupos de 3 personas, presentar el

diseo en forma manuscrita (con puntabola). Realizar la simulacin de cada circuito

en Proteus (version 7.10) y Winbreadboard, entregar en un CD. Implementar todos los

circuitos en Protoboard.

También podría gustarte

- Selección Del TrabajoDocumento4 páginasSelección Del TrabajoIvaan AlehaandrooAún no hay calificaciones

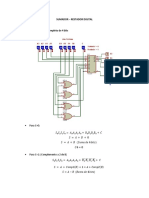

- Sumador - Restador DigitalDocumento2 páginasSumador - Restador Digitaltony tornadoAún no hay calificaciones

- Capitulo 1 PDFDocumento12 páginasCapitulo 1 PDFtony tornadoAún no hay calificaciones

- Ecualizador Digital en SimulinkDocumento1 páginaEcualizador Digital en Simulinktony tornadoAún no hay calificaciones

- Examen ResueltoDocumento10 páginasExamen Resueltotony tornado100% (1)

- Lab 3 Digital 1 18102012Documento17 páginasLab 3 Digital 1 18102012tony tornadoAún no hay calificaciones

- Lab Nº3 Digital 2 08042013Documento4 páginasLab Nº3 Digital 2 08042013tony tornadoAún no hay calificaciones

- Problemas TransistoresDocumento3 páginasProblemas Transistorestony tornadoAún no hay calificaciones

- Planificación TerritorialDocumento3 páginasPlanificación TerritorialCristian FioleAún no hay calificaciones

- Relato Imaginería en Pareja, Curso Amistad, Poesía y Salud IntegralDocumento8 páginasRelato Imaginería en Pareja, Curso Amistad, Poesía y Salud IntegralNicholas RhodesAún no hay calificaciones

- Ejercicios de Energías RenovablesDocumento2 páginasEjercicios de Energías Renovablesingeniero_ronald0% (1)

- InferenciasDocumento13 páginasInferenciasAngeluis PuyconAún no hay calificaciones

- FilosofíaDocumento7 páginasFilosofíaleilanisAún no hay calificaciones

- Tarea de ComunicaciónDocumento3 páginasTarea de ComunicaciónDaniel GuerraAún no hay calificaciones

- Odi - Maestro MecanicoDocumento6 páginasOdi - Maestro MecanicoManuel Alejandro Gonzalez Lopez50% (2)

- Marca PersonalDocumento11 páginasMarca PersonalWendy VásquezAún no hay calificaciones

- Ejercicios Diagrama Casos de UsoDocumento2 páginasEjercicios Diagrama Casos de Usomarynar24Aún no hay calificaciones

- 28 de Agosto - Sesión 5 AñosDocumento9 páginas28 de Agosto - Sesión 5 AñosMarielenaAún no hay calificaciones

- Metodología de La Auditoría - Fase 5Documento26 páginasMetodología de La Auditoría - Fase 5Catalina Caballero ZamoraAún no hay calificaciones

- Título de La SesiónDocumento4 páginasTítulo de La SesiónFranklin RomeroAún no hay calificaciones

- Guía Texto 20. LA. Stam, Burgoyne y Fitterman-Lewis 1-1Documento2 páginasGuía Texto 20. LA. Stam, Burgoyne y Fitterman-Lewis 1-1tomasAún no hay calificaciones

- Formato - Plan de Acción (1) EDUCANDO EN FAMILIADocumento2 páginasFormato - Plan de Acción (1) EDUCANDO EN FAMILIAGema Cedeño100% (1)

- Penal III (Economico)Documento8 páginasPenal III (Economico)Mariana HerediaAún no hay calificaciones

- Unidad 07 - Energia Potencial y Conservación de La EnergíaDocumento17 páginasUnidad 07 - Energia Potencial y Conservación de La EnergíaLucas GamboaAún no hay calificaciones

- CA109ES1104Documento24 páginasCA109ES1104carlos vidalAún no hay calificaciones

- Derecho A Castigar y PenarDocumento12 páginasDerecho A Castigar y PenarInsegura SeguridadAún no hay calificaciones

- Codigo Urbanistico 2021Documento44 páginasCodigo Urbanistico 2021Malee InsfranAún no hay calificaciones

- Cuadro Comparativo Levantamientos Topográficos y AltimétricosDocumento3 páginasCuadro Comparativo Levantamientos Topográficos y Altimétricosjenny_plazas_150% (2)

- La Corrupción en Nuestro PaísDocumento3 páginasLa Corrupción en Nuestro PaísJuan Claudio Torres RodriguezAún no hay calificaciones

- Djwhal Khul - Conexion Cosmica Con Mentes TerrestresDocumento35 páginasDjwhal Khul - Conexion Cosmica Con Mentes TerrestresMaría Del Pilar Del Río Hernández100% (2)

- 7.2. El Procedimiento de Investigación 16.03.2022Documento13 páginas7.2. El Procedimiento de Investigación 16.03.2022Rebeca Suyapa Rivera ValleAún no hay calificaciones

- Ciencia JurídicaDocumento10 páginasCiencia JurídicaEthel SanchezAún no hay calificaciones

- Que Es Una MezclaDocumento4 páginasQue Es Una MezclaRenzo Jesus Orozco RamosAún no hay calificaciones

- Depresión en Personas Que Viven Con VIHDocumento19 páginasDepresión en Personas Que Viven Con VIHAndriana GaribayAún no hay calificaciones

- Cinco Propuestas de Integración TIC en Ciencias NaturalesDocumento3 páginasCinco Propuestas de Integración TIC en Ciencias NaturalesMarceloAún no hay calificaciones

- La Comunicación Efectiva Del Líder en La OrganizaciónDocumento5 páginasLa Comunicación Efectiva Del Líder en La OrganizaciónAdriana VegaAún no hay calificaciones

- Cuestionario Com300!1!2019 (Defensa)Documento4 páginasCuestionario Com300!1!2019 (Defensa)Nancy Vargas RodriguezAún no hay calificaciones